MicroZed Chronicles: Advanced Select I/O Logic Resources

February 25, 2022

Editor’s Note: This content is republished from the MicroZed Chronicles, with permission from the author.

Last week we looked at IDELAY2 and ODELAY2 in 7 series IO, the selectIO which is included in 7 Series, UltraScale and UltraScale+ provides users with several additional features which can help significantly in our designs. One of these OSERDESE2 and ISERDESE2 these structures enable conversion between serial and parallel formats in the IO. When transmitting data, the OSERDESE2 provides conversion from parallel to serial, while the ISERDESE2 provides serial to parallel conversion. Of course, for these to correctly function we need to provide a reference clock at the correct ration for the serialisation, de serialisation with respect to the data clock frequency.

In this week’s blog we are going to examine the ISERDESE2, this is the input de-serialiser and comes in very useful in several applications e.g., image and signal processing. The usefulness of the ISERDESE2 is its ability to align a training pattern sent by an upstream device so that we can recover the data correctly.

Like many structures the ISERDESE2 provides support for a range of applications from DDR and QDR memory interfaces, work with strobed interfaces, networked and asynchronous interfaces.

At the high level the ISERDESE2 operates in either Single Data Rate or Double Data Rate conversion providing serial to parallel conversion of 2 to 8 data bits or 2 to 14 when two cascaded together. To enable reordering of the parallel data a bitslip module is provided which changes the order of the parallel interface.

One of the most common uses of ISERDESE2 is in alignment of data for training sequences when source synchronous interfaces are used.

To get started looking at this we are going to create a simple design which instantiates a ISERDES2E in the networking mode and applies to it a sequence of data which contains a training sequence to lock on to.

In this example we will be performing an 8:1 de-serialisation, this means the parallel data output will be at 1/8th the input data rate. For this example, I chose a line rate of 100MHz which gives an output data rate of 12MHz. We need to provide both these clocks to the ISERDES2E module on the clock and clock divide inputs.

Locking on to the training sequence will require the use of the bitslip interface to align the data to the expected sequence. Controlling the bitslip interface will be a state machine which is observing the parallel output of the ISERDESE2.

Inserting the data will be a simple test bench which cycles through a long, small section of data which contains several training sequences along with normal data.

The state machine which controls the bitslip interface is simple, the bitslip interface is clocked by the clock divide. The bitslip input can be asserted high for one clock cycle and depending on the mode either SDR or DDR the controlling state machine should wait either two or three clock cycles before it checks the output pattern. For this application we are working in the SDR mode.

To instantiate the ISERDESE2 I again used the language templates provided by Vivado and edited the template for the configuration I desired for the application.

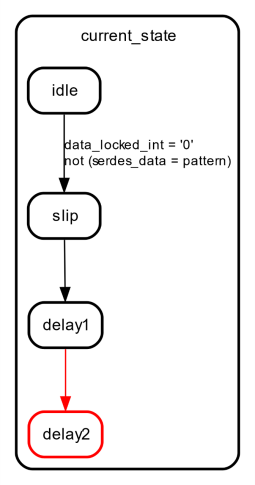

The state machine design is simple and implements the following state diagram.

The FSM is designed usch that once the pattern is detected it stops looking for it and locks, asserting a locked signal. This signal will be lost on reset as the FSM is reset and the ISERDESE2 reverts to its initial configuration.

Stimulating the design using test bench, shows the initial start up after reset when the statemachine is looking for the training pattern (in this case eb). The simulation waveform below clearly shows the bitslip being asserted, each time following its assertion there is atleast 2 divided clock cycles.

Once the training pattern is detected the FSM stops asserting bitshift an the locked signal is asserted.

In the simulation waveform we can see the several training pattern being identified and then the expected count. As this is a simple test bench the pattern then just repeats until the end of the testbench.

I have uploaded the application to my github.

We will look at OSERDESE2 in a blog soon as we explore the Select I/O!

Xilinx Xclusive Blog

-

- AMD Telecom Leadership Showcased at OFC 2022

- Mar 08, 2022

-

- 准备呐喊助威吧:赛灵思将参加 BattleBots电视系列角逐赛

- Dec 07, 2021

Adaptable Advantage 博客

Xilinx AI 和软件博客

-

- Vitis AI 2.0 现已推出!

- Jan 20, 2022

-

- 连获“双奖”,Xilinx AI 团队实力绽放国际视觉顶会

- Oct 08, 2021

-

- 您是否了解过赛灵思应用商店?评估和购买 Alveo 及 Kria SOM 解决方案的一站式商店。

- Sep 23, 2021