ASIC 仿真实现

ASIC 和 SoC 仿真的突破性性能与集成

概述

硬件仿真是对开发中的系统进行调试和功能验证的过程。综合硬件功能验证对于降低开发成本和缩短上市进程至关重要。处理设计修改时,仿真可提供快速启动和快速周转时间。此外,仿真还可提供高度的设计可访问性及调试可见性,这样,ASIC 设计人员就可在流片前发现潜在的硬件故障。随着软件复杂性和成本的急剧上升,早期的硬件验证对于降低风险和加速系统开发至关重要。

为了最大限度提高系统性能并使用仿真器实现可预测的更快设计周期,Xilinx提供了最全面的设计方法和设计开发平台。Vivado 设计套件向仿真类系统设计人员提供了业界一流的开发体验。这是 Xilinx 第三代仿真类工具、IP 及设计流程。

对于仿真平台,Xilinx 解决方案:

- 有助于大型设计消除在许多情况下对多芯片分区的需求

- 通过提供快速的布局和路由来降低大型 ASIC 和 ASSP 设计的开发风险

- 降低系统级功耗

- 通过 ASIC 类时钟及路由架构实现高利用率

- 实现高级调试与仿真加速

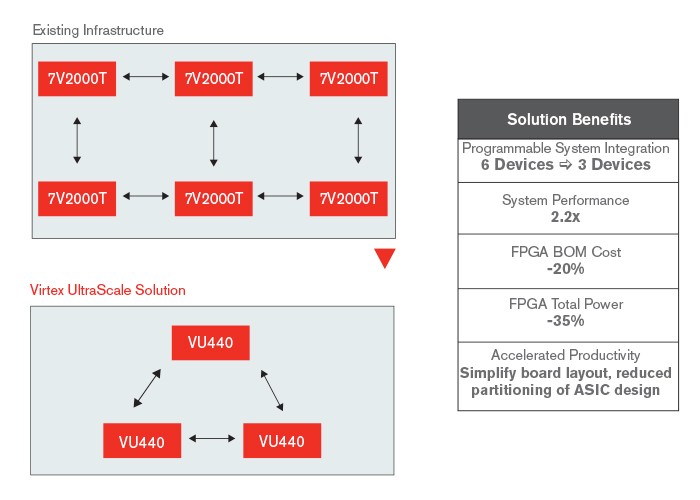

凭借 Virtex®-7 2000T FPGA 和 Virtex UltraScale™ VU440 FPGA, Xilinx 一直是最大容量 FPGA 的市场领导者。16nm Virtex UltraScale+™ 系列现包括全球最大的 FPGA - Virtex UltraScale+ VU19P FPGA,可实现连续三代高端产品领先地位。

Virtex-7 2000T

内置 ASIC 仿真功能

- 2M 逻辑单元、 6.8B 晶体管

- 36 个 12.5Gb/s 串行收发器

- 46 Mb block RAM

- 1,200 个 I/O

- 第一代 SSI 技术

Virtex UltraScale VU440

在 20nm 下将器件密度提高 4 倍

- 5.5M 系统逻辑单元、 20B 晶体管

- 48 个 16.3Gb/s 串行收发器

- 89 Mb block RAM

- 1,456 个 I/O

- 第二代 SSI 技术

Virtex UltraScale+ VU19P

具全球最大容量的 FPGA

- 拥有 900 万个系统逻辑单元、35B 晶体管

- 80 个 28Gb/s 串行收发器

- 94.5Mb block RAM

- 2,072 个 I/O

- 第三代 SSI 技术

技术文档

设计范例

使用 Xilinx UltraScale™ 架构,ASIC 原型 & 模拟可实现突破性性能和集成。Virtex® UltraScale 器件通过高逻辑容量、超过 90% 器件利用率、堪比 ASIC 的时钟、增强型布线和面向引脚多路复用的高速收发器简化设计分区。突破性架构融合 Xilinx Vivado® Design Suite 为满足领先的 ASIC 和 SoC 平台需求提供了理想的解决方案。

解决方案概述与优势

- 突破性器件容量 降低分区数量,并简化开发板布局

- Vivado Design Suite 增强型布线和协同优化确保超过 90% 的器件利用率

- 堪比 ASIC 的时钟性能 有效地映射复杂的 ASIC 和 SoC 时钟树

- 高速收发器 实现 FPGA 之间高效的引脚多路复用,并支持下一代系统的 I/O 接口需求

UltraScale 架构优势

- 海量 I/O 带宽

- 提供超过 1 Tbps 的芯片对芯片带宽

- 低延时收发器实现芯片间互连

- 海量数据流 & 路由

- 支持高性能的本地 ASIC 总线

- 支持高性能的本地 ASIC 总线

- 堪比 ASIC 的时钟性能

- 最大化复杂 SoC 原型设计的灵活性

- 最大化复杂 SoC 原型设计的灵活性

- 系统性能

- 单器件性能提升 15-30 %

- 分区减少,性能提升 3 倍

- 功耗管理

- 系统功耗最多可降低 35%