MicroZed Chronicles: Answering Webinar Questions

March 11, 2022

Editor’s Note: This content is republished from the MicroZed Chronicles, with permission from the author.

A couple of week ago, I held several webinars on how to convert Spartan-6 designs into 7 series devices. There were several interesting questions raised during the webinars which I thought would be best answered here in more detail.

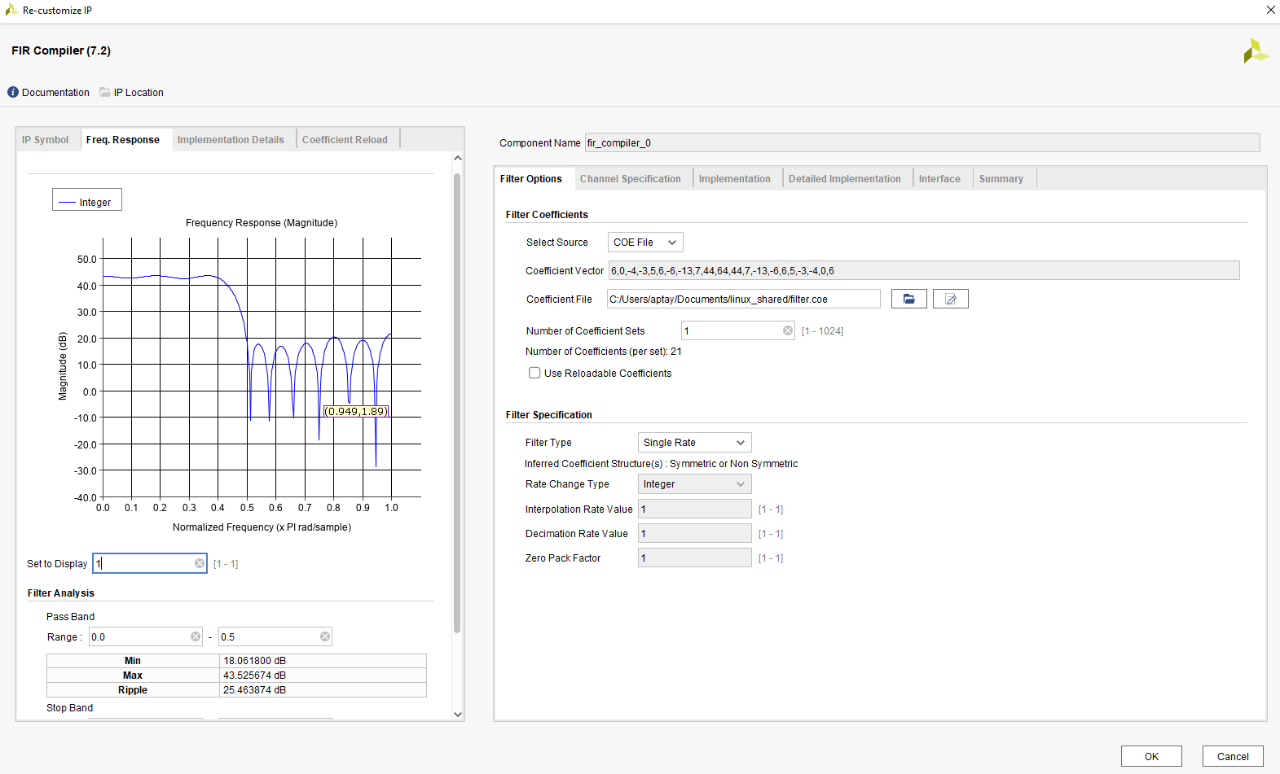

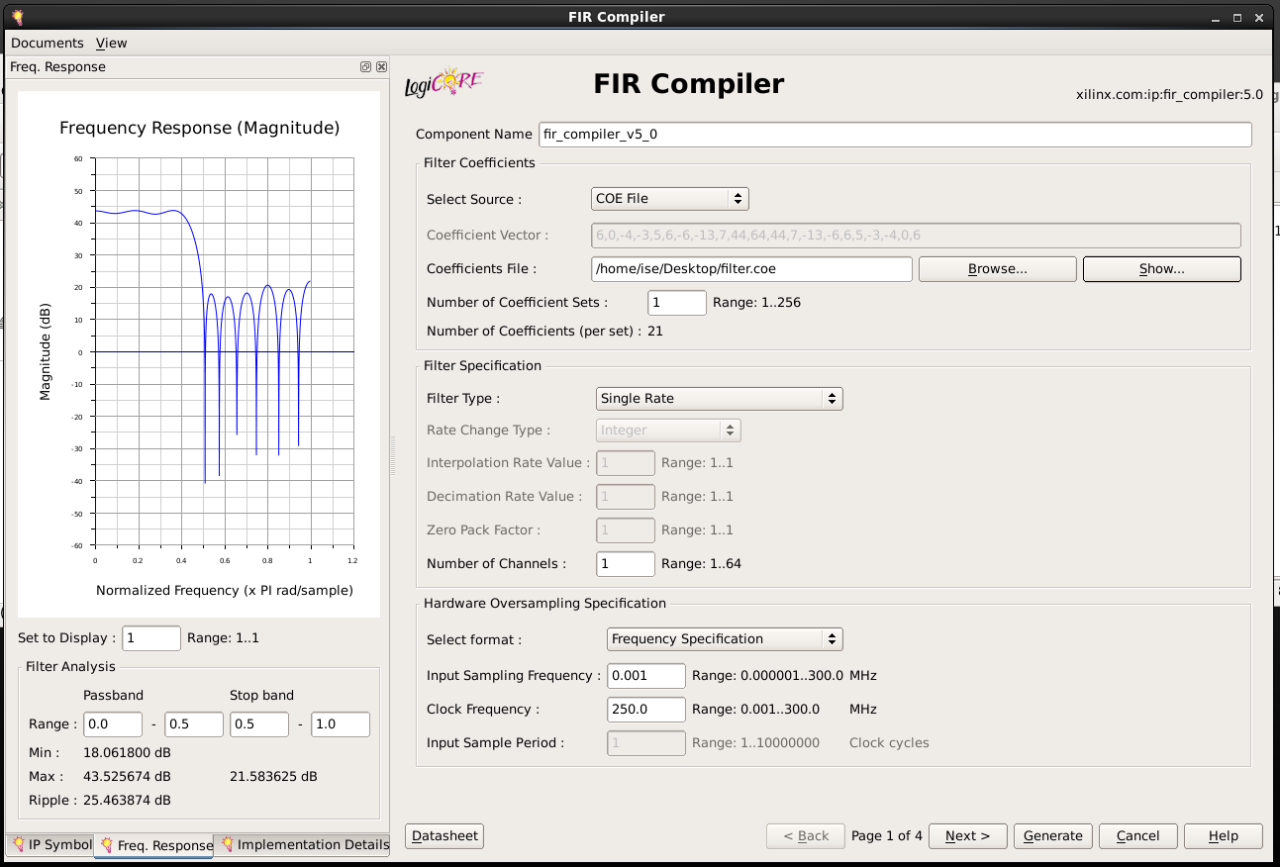

The first question was about the FIR compiler in the ISE design suite and asked if the Filter design coefficients would be able to be used without modification in Vivado. The COE format used by the ISE design suite and Vivado is identical. For a successful COE file, we need to provide the radix and the coefficient data as demonstrated below.

radix=10;

Coefdata = 6,0,-4,-3,5,6,-6,-13,7,44,64,44,7,-13,-6,6,5,-3,-4,0,6;

Once the COE file has been created, we can load it into both FIR compilers in the ISE design suite and Vivado to define the filter.

Since the filter coefficients stay the same, we can benefit from several enhancements in the filter design in Vivado. These include leveraging AXI and the 18x25 signed DSP in place of the 18x18 provided in Spartan-6.

The second question was in respect to IO migration. It’s important to note that the Spartan-6 and 7 series devices have different IO capabilities. 7 series IO is provided in two classes: High Range (HR) and High Performance (HP). HR banks support IO standards of 3v3 and 2v5, while HP banks support IO standards up to 1v8 and are intended to support higher-performance interfaces.

In comparison, Spartan-6 devices do not have the different classes of banks because each IO bank will support any of the supported standards, provided that the VCCIO is configurated correctly. Care must be taken then when transitioning from Spartan-6 to 7 series devices to make sure sufficient IO resources of the required type are available.

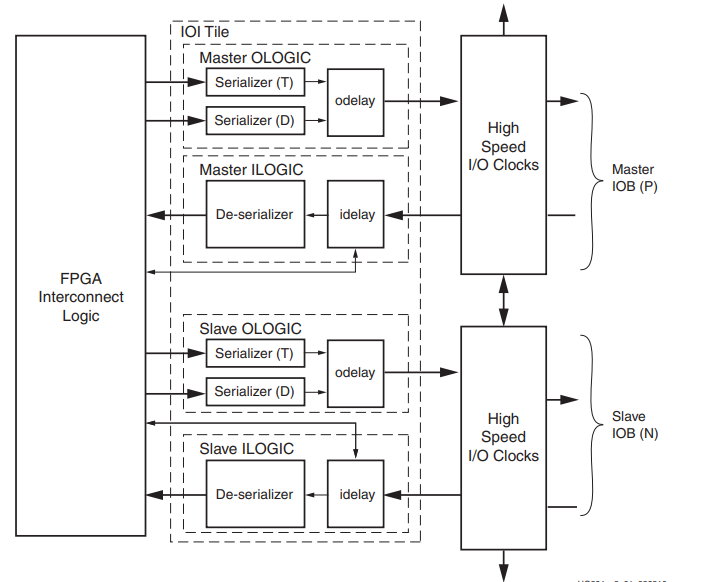

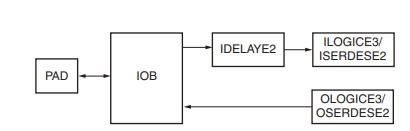

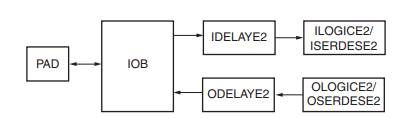

Along with the supported IO standard and the split between HP and HR IO on 7 series devices, we also need to consider the resources available in the IO logic. Spartan-6 devices provide both IOSERDES and IODELAYS in the IO structure.

Within the 7 series range, Spartan-7 and Artix-7 provide the designer with only HR IO. These HR IO contain IOSERDES but only IDELAY. There is no ODELAY available. If an ODELAY is required, HP IO are required and these are available only on the Kintex-7 and Virtex-7 devices.

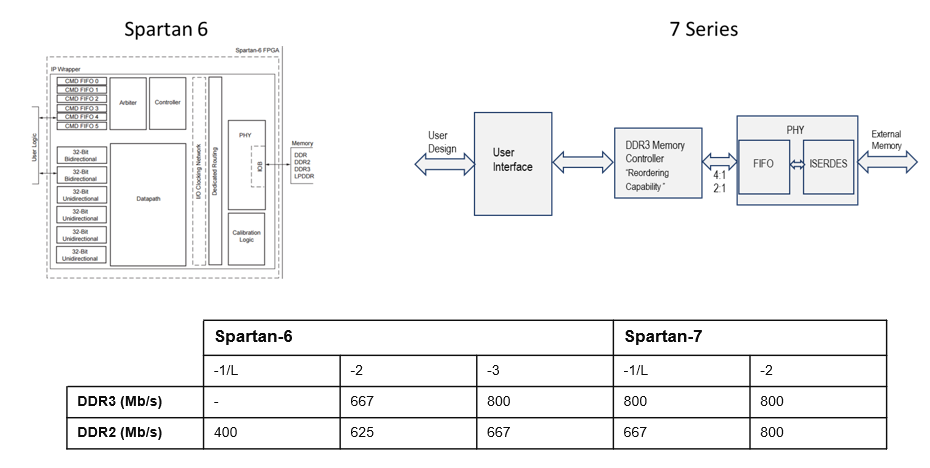

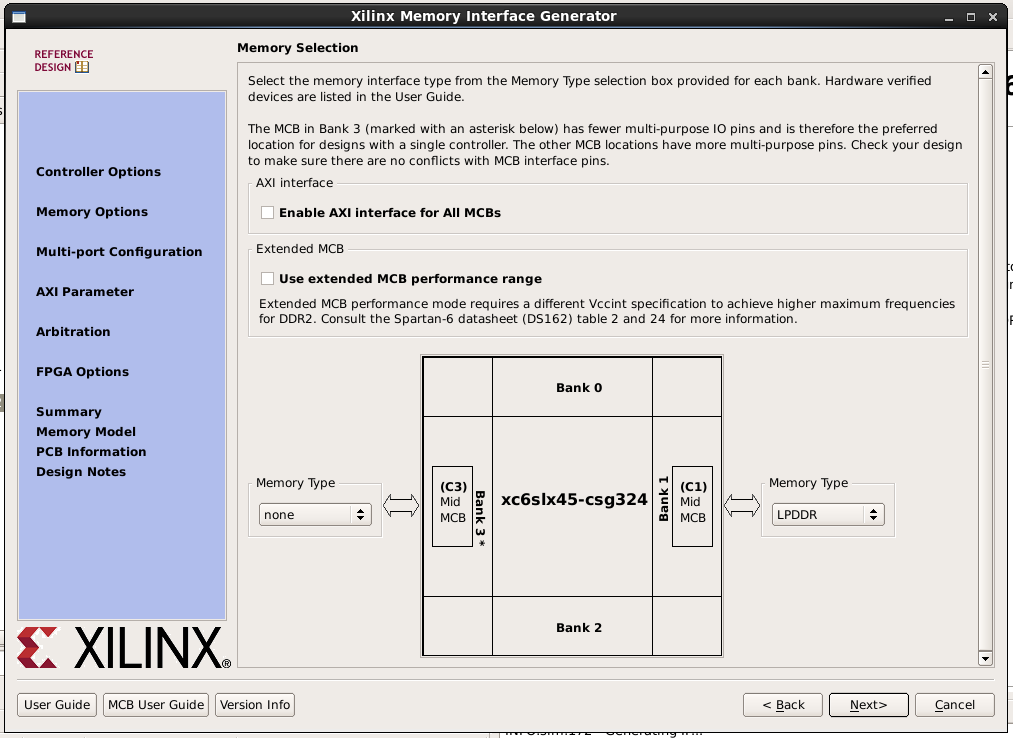

The final question was related to the Spartan-6 Memory Controller Block (MCB). In the Spartan-6 range, the MCB is implemented as a hard macro within the silicon. This means the MCB IO are provided on fixed pins on IO banks which limits flexibility with the pinout. By contrast, 7 series devices provide a soft-core memory controller for DDR2 / DDR3 interfaces which enables greater flexibility for the IO placement.

Both DDR2 / DDR3 are supported in Spartan-6 and 7 series devices and conversion from S6 to S7 is straightforward. We can use the wizards in both devices to configure the Memory Interface Generator for the selected memory component.

Hopefully this answers the questions for the participants. I suggest you check out the webinar if you have not yet watched it and are considering changing from Spartan-6 to 7 series devices.

Xilinx Xclusive Blog

-

- AMD Telecom Leadership Showcased at OFC 2022

- Mar 08, 2022

-

- 准备呐喊助威吧:赛灵思将参加 BattleBots电视系列角逐赛

- Dec 07, 2021

Adaptable Advantage 博客

Xilinx AI 和软件博客

-

- Vitis AI 2.0 现已推出!

- Jan 20, 2022

-

- 连获“双奖”,Xilinx AI 团队实力绽放国际视觉顶会

- Oct 08, 2021

-

- 您是否了解过赛灵思应用商店?评估和购买 Alveo 及 Kria SOM 解决方案的一站式商店。

- Sep 23, 2021