AR# 52491

|14.3 EDK, Zynq-7000 - How do I run the Zynq PS-PL AXI interfaces at the highest frequency?

描述

How do I run the Zynq PS-PL AXI interfaces at the highest frequency?解决方案

The Zynq PS AXI interfaces are able to close timing above 200 MHz, but may require assistance in ISE-based tools.

In ISE Design Suite tools, the Zynq PS AXI interfaces respond very well to basic floorplanning of the axi_interconnect connecting to the right side of the PS7 primitive.

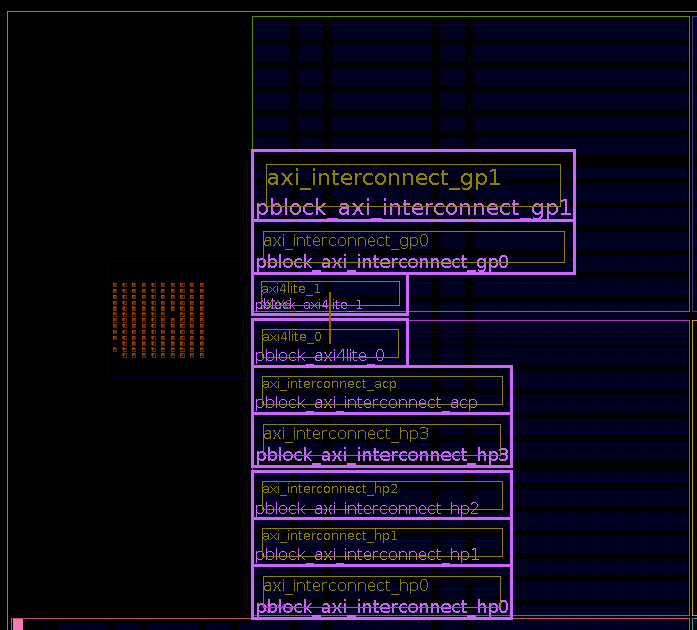

For example, see the following zc7045 floorplan (as viewed from PlanAhead Device view):

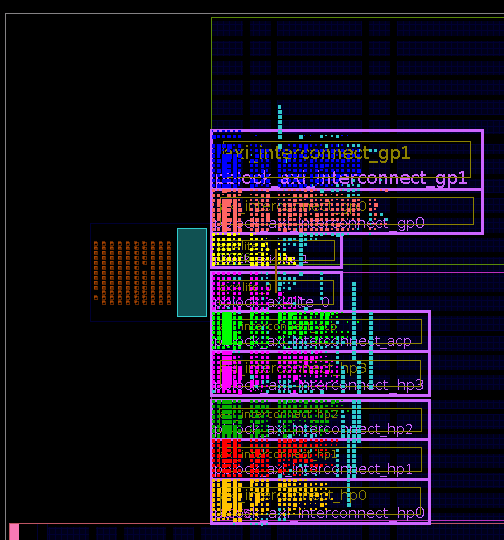

The resulting placement of a synchronous interconnect performing AXI4-AXI3 conversions and register pipelining yield:

The size and placements can be modified to accommodate the PS AXI interfaces uses, and the size of the axi_interconnect residing in the PL.

Example Constraints for 7045:

The following constraints instance name and placement locations can be modified for other designs/devices.

# HP Slave Interfaces

INST "system_i/axi_interconnect_hp0" AREA_GROUP = "pblock_axi_interconnect_hp0";

AREA_GROUP "pblock_axi_interconnect_hp0" RANGE=SLICE_X26Y250:SLICE_X61Y258;

INST "system_i/axi_interconnect_hp1" AREA_GROUP = "pblock_axi_interconnect_hp1";

AREA_GROUP "pblock_axi_interconnect_hp1" RANGE=SLICE_X26Y259:SLICE_X61Y266;

INST "system_i/axi_interconnect_hp2" AREA_GROUP = "pblock_axi_interconnect_hp2";

AREA_GROUP "pblock_axi_interconnect_hp2" RANGE=SLICE_X26Y267:SLICE_X61Y274;

INST "system_i/axi_interconnect_hp3" AREA_GROUP = "pblock_axi_interconnect_hp3";

AREA_GROUP "pblock_axi_interconnect_hp3" RANGE=SLICE_X26Y275:SLICE_X61Y283;

# GP Slave Interfaces

INST "system_i/axi_interconnect_gp0" AREA_GROUP = "pblock_axi_interconnect_gp0";

AREA_GROUP "pblock_axi_interconnect_gp0" RANGE=SLICE_X26Y307:SLICE_X71Y315;

INST "system_i/axi_interconnect_gp1" AREA_GROUP = "pblock_axi_interconnect_gp1";

AREA_GROUP "pblock_axi_interconnect_gp1" RANGE=SLICE_X26Y316:SLICE_X71Y326;

#ACP Slave Interface

INST "system_i/axi_interconnect_acp" AREA_GROUP = "pblock_axi_interconnect_acp";

AREA_GROUP "pblock_axi_interconnect_acp" RANGE=SLICE_X26Y284:SLICE_X61Y291;

#GP Master Interfaces

INST "system_i/axi4lite_0" AREA_GROUP = "pblock_m_gp0";

AREA_GROUP "pblock_m_gp0" RANGE=SLICE_X26Y292:SLICE_X47Y299;

INST "system_i/axi4lite_1" AREA_GROUP = "pblock_m_gp1";

AREA_GROUP "pblock_m_gp1" RANGE=SLICE_X26Y300:SLICE_X47Y306;

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 52540 | Zynq-7000 SoC - Frequently Asked Questions | N/A | N/A |

| AR# 52491 | |

|---|---|

| 日期 | 02/28/2013 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |