AR# 67544

|UltraScale DDR4/DDR3 - Tactical Patch - Data errors seen at user interface when using Normal Ordering Error

描述

Version Found: DDR4 v2.0, DDR3 v1.2

Version Resolved: See (Xilinx Answer 69035) for DDR4 and (Xilinx Answer 69036) for DDR3.

An issue with the DDR4/DDR3 user interface has been identified where the data presented is from a future read from the same address. When this occurs, a data error would be triggered. After the data error, app_rdy might get stuck low and the read buffer stay full forever.

This issue can occur with any type of DDR4/3 traffic pattern although it is extremely rare for this lock condition to occur. The issue has been seen in both hardware and simulation. The error is not seen when using the Strict Ordering mode of the controller.

Including the attached patch is recommended.

解决方案

Issue Details:

The User Interface sends the same read data buffer address (dBufAdr) a second time to the memory controller before the memory controller has finished writing back the first read data into the read buffer. This causes the unrecoverable lock condition.

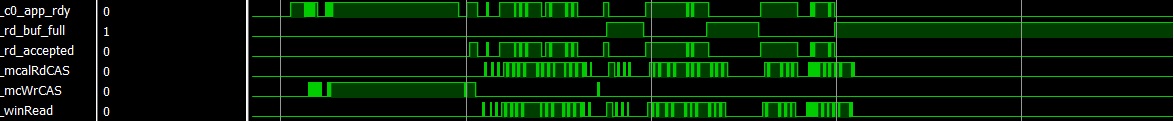

If the stuck behavior occurs, it would look similar to the following example:

Attached to this answer record are patches for Vivado 2016.1 and 2016.2 to resolve this issue as well as instructions on patch installation.

If a patch for a previous version is required, please open a Service Request.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| AR67544_Vivado_2016_1_preliminary_rev1.zip | 1 MB | ZIP |

| AR67544_Vivado_2016_2_preliminary_rev1.zip | 1 MB | ZIP |

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 69036 | UltraScale/UltraScale+ DDR3 - Release Notes and Known Issues | N/A | N/A |

| 69035 | UltraScale/UltraScale+ DDR4 - Release Notes and Known Issues | N/A | N/A |