AR# 63849

|JESD204 v6.1 (PG066) Product Guide - Table 2-14 and Table 2-15 contain typos

描述

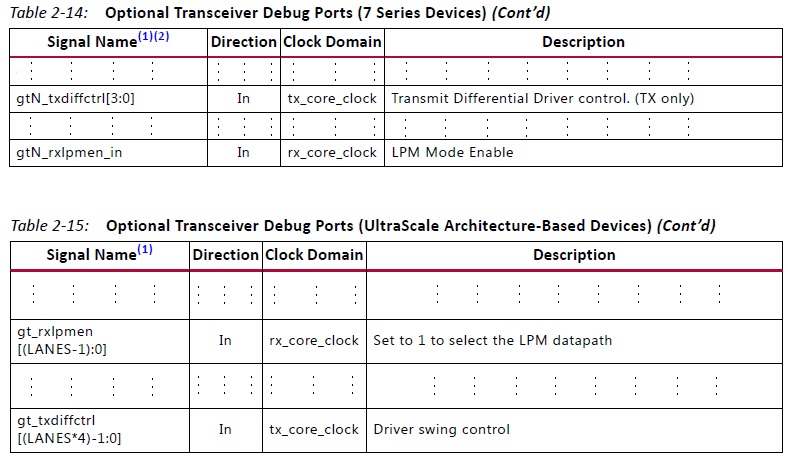

The JESD204 Product Guide (PG066), v6.1, lists the Optional Transceiver Debug Ports for 7 Series (Table 2-14) and UltraScale (2-15) devices.

The clock domain is also listed in these tables.

Two signals (gt_rxlpmen and gt_txdiffctrl) do not have the correct clock domain listed.

解决方案

The following signals in Table 2-14 and 2-15 are listed as being synchronous to the core clock (either rx_core_clk or tx_core_clk):

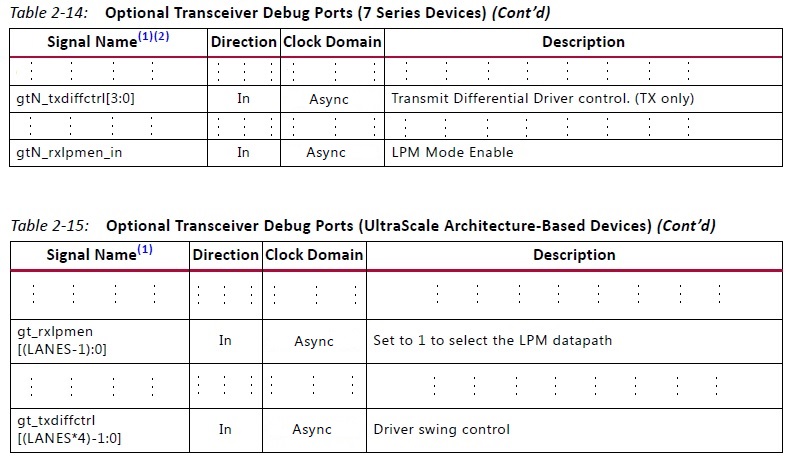

These signals are asynchronous inputs to the core and are not synchronous to the core clocks as indicated in (PG066) v6.1.

Table 2-14 and 2-15 should read as follows:

This has been corrected in (PG066) v7.0.

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 54480 | LogiCORE IP JESD204 - Release Notes and Known Issues for Vivado 2013.1 and newer tools | N/A | N/A |

| AR# 63849 | |

|---|---|

| 日期 | 04/26/2016 |

| 状态 | Active |

| Type | 综合文章 |

| IP | |

People Also Viewed