AR# 52808

|KC705 Example Designs - MIG Design Files enhanced window margining

描述

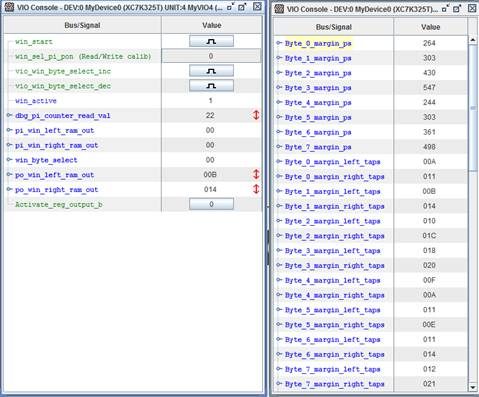

The MIG Example Design targeting the KC705 contains new window margining features.

These are included starting with the 14.3/2012.3 software release.

The window margining can be used to determine if sufficient margin is available for reliable operation and should be used for debugging purposes if data errors are seen after calibration.

The window margining can be performed using a manual or automated flow as described in the 7 Series Hardware Debug Guide available in (Xilinx Answer 43879).

The KC705 MIG Design files contain modifications that enhance the automated window margining feature in the following way:

The KC705 MIG Design files contain modifications that enhance the automated window margining feature in the following way:

- Stores left and right edge values from block RAM into registers

- Stores the worst case values in picoseconds

- Calculates margin for each byte group and displays results in picoseconds in ChipScope analyzer

- Scanning of the I/O margin continues running indefinitely until a reset or a value of 0 on the VIO Activate_reg_output port occurs.

See the image below:

解决方案

The KC705 MIG Example Design files containing the enhanced window margining are listed below:

- ise_flow.bat

- vio_async_in256_cg.xco

- ddr2_ddr3_chipscope.v

- ddr_icon_cg.xco

- example_top.v

- rem_files.bat

- example_top.cpj

Revision History:

11/8/2012 - Initial Release

本答复记录是否对您有帮助?

链接问答记录

子答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 43879 | 7 系列 MIG DDR3/DDR2 - 硬件调试指南 | N/A | N/A |

| AR# 52808 | |

|---|---|

| 日期 | 02/25/2015 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| Tools | |

| IP | |

| Boards & Kits | |

People Also Viewed