Versal ACAP’s CPM: Satisfying the Most Demanding Connectivity Requirements with PCI Express

September 8, 2020

Editor’s Note: This content is contributed by Eric Crabill, Technical Marketing Engineer at Xilinx

More than a decade ago, we anticipated the pervasiveness of PCI Express® and began offering integrated blocks for it in our devices. Over the years, we have refined our integrated block offering with each new Xilinx architecture. We now see PCI Express applied in nearly all our developers’ markets.

The What of CPM

The Versal® architecture continues to offer a Programmable Logic Integrated Block for PCI Express (PL PCIE) further improved from that available in prior architectures and adds an Integrated Block for PCI Express with DMA and Cache Coherent Interconnect (CPM). Architecturally, CPM is one component of the Versal architecture integrated shell, the whole of which is timing closed and resides “outside” the programmable logic (PL). The illustration below shows where CPM resides, with PL PCIE included for context:

<Where CPM and PL PCIE reside>

CPM is adjacent to the PL, the processing system (PS), the network on chip (NoC), and transceivers – in support of tight coupling to all these resources. CPM provides high bandwidth data transfer between the PCI Express link partner, the PL, the Scalar Engines, and the programmable NoC. The programmable NoC is highly connected, providing a performance route into one or more integrated DDR memory controllers and other device resources.

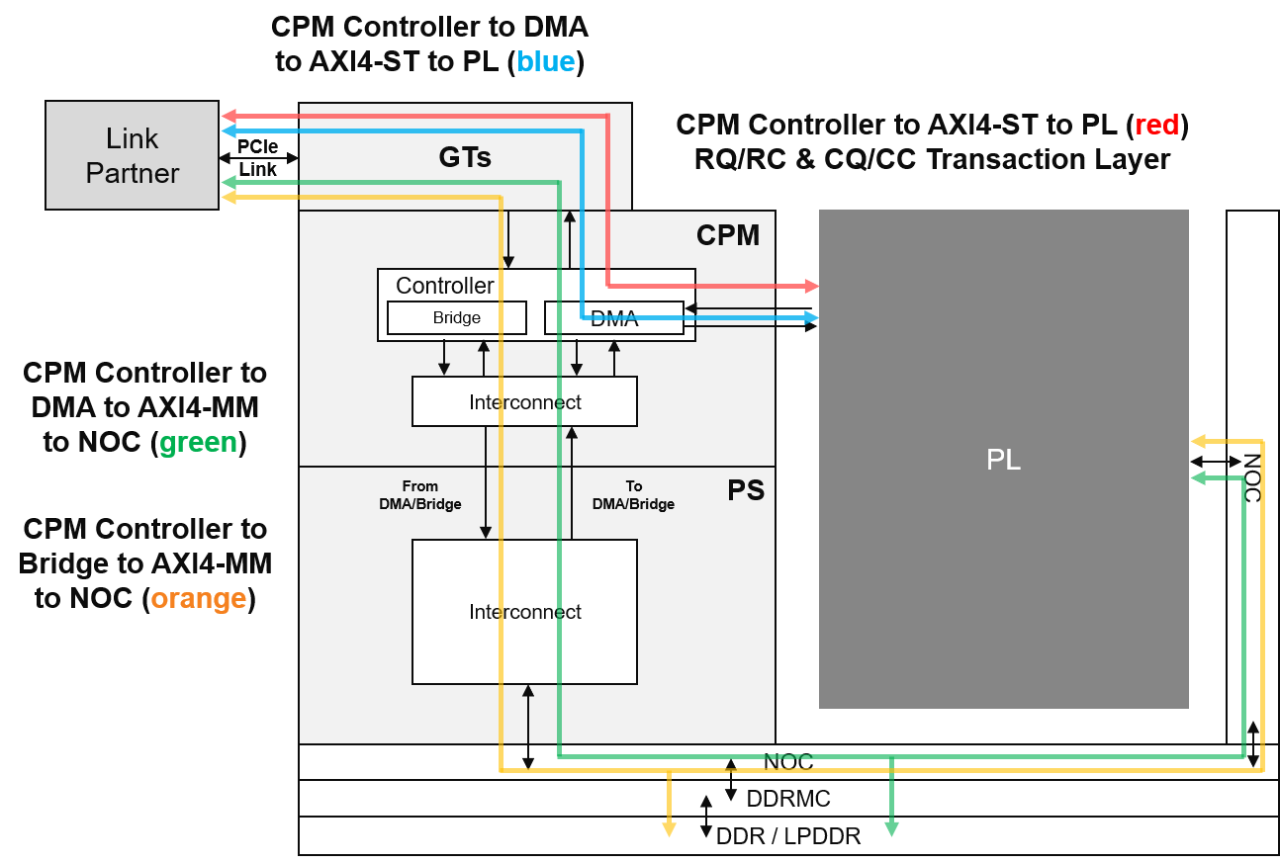

CPM offers a variety of datapath options depending on the mode in which it is used. The following diagram is a simplified partial view showing a superposition of available paths through CPM across one of its controllers for PCI Express and an associated DMA/Bridge subsystem:

<Simplified view of various datapath options>

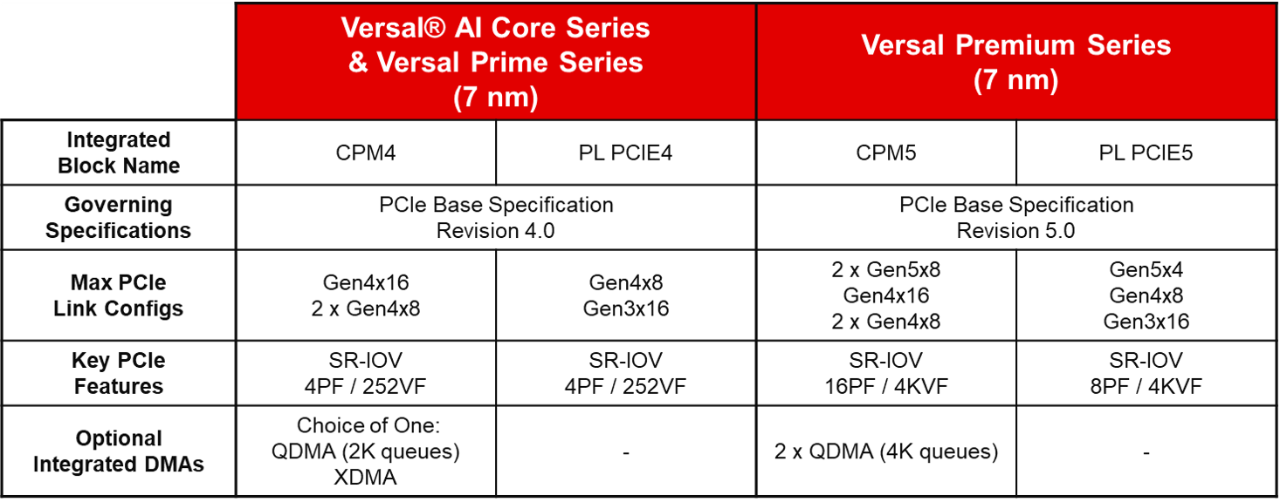

Turning to the question of the totality of what is in CPM for PCIe and how that compares to PL PCIE (without venturing into cache coherent interconnect support), we need to dive deeper and push into implementation details. Take a quick look at the table below, which reveals specifics for PCI Express in CPM and PL PCIE as implemented across several series of Versal ACAPs. Note that the numerical suffix for each block name indicates a relative sequence in the evolution of each block type:

Leveraging either CPM4 or CPM5 in a design pulls in a completely verified Xilinx subsystem, delivering access to the result of 100 person-years of Xilinx R&D, at no additional cost. And, these integrated blocks provide remarkable value in equivalent programmable logic LUTs over soft IP implementations. Depending on the features enabled, CPM4 can represent up to 800K LUTs, and CPM5 can represent up to 1,000K LUTs. Both are offered with supporting collateral – including extensive documentation and driver examples.

The Why of CPM

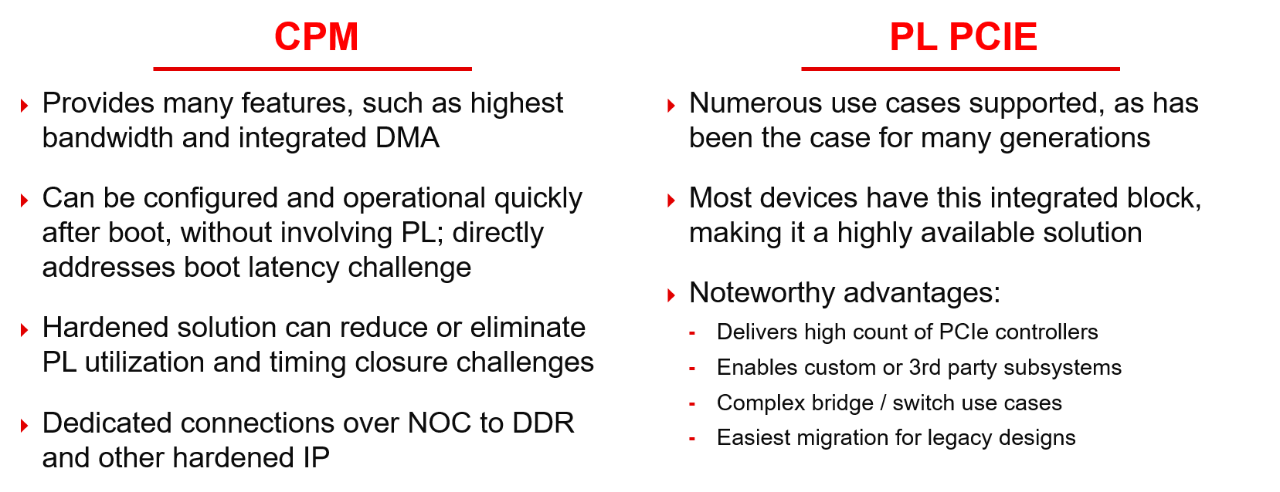

An adaptive compute acceleration platform needs the capability to transmit and receive enormous volumes of data, and PCI Express is highly effective in this regard. The Versal architecture provides system designers with new, additional options for integrating PCI Express to satisfy the most demanding connectivity requirements. Let’s look at the following chart of strengths of each Versal architecture solution for PCI Express:

<CPM vs. PL PCIE>

CPM brings the highest bandwidth and a host of new features and is woven into the architecture to provide even more compelling value. This value includes adaptability and time-to-revenue advantages you expect, plus seamless NoC integration, substantial PL resource savings, options for turn-key timing closure, and low latency boot flows. CPM supports operation without PL configuration or PS involvement, which is a key technical feature supporting low latency boot in applications involving PCI Express.

The When of CPM

Now! Versal AI Core series & Versal Prime series offering CPM4 are already shipping to customers with early access to the Vivado® Design Suite enabled for Versal ACAP, and can start prototyping with a VCK5000, VCK190, or VMK180 evaluation kit. From within Vivado Design Suite, CPM4 is accessed through the control interfaces and processing system (CIPS) IP in the Vivado IP Catalog. The availability of CPM5 is planned for Versal Premium series.

I invite you to browse PG346, Versal ACAP CPM Mode for PCI Express Product Guide, and take the next step in evaluating how CPM addresses connectivity needs for PCI Express, enabling you to focus your R&D on the unique value proposition of your product. Please also visit the PCI Express technology page on the Xilinx website at https://www.xilinx.com/products/technology/pci-express.html. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license.