AR# 72084

|UltraScale/UltraScale+ : FIFO_EMPTY behavior details

描述

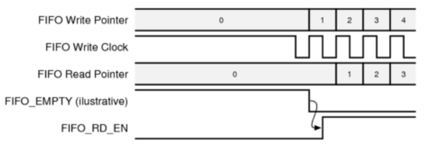

FIFO_EMPTY is typically used to indicate when the FIFO_WR_CLK starts at the end of the startup sequence as shown below:

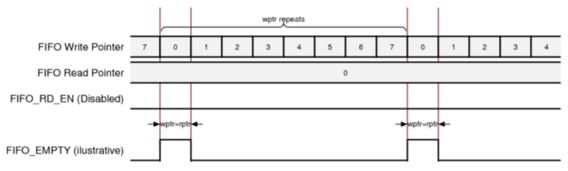

If FIFO_RD_EN is not asserted at the end of the startup sequence, FIFO_EMPTY should pulse once every 8 FIFO_WR_CLK cycles (see figure).

This is not reliable. The issue is dependent on the relative clock phases of the FIFO_WR_CLK and FIFO_RD_CLK which gets routed through the fabric.

For example, some designs do not use the first falling edge of the FIFO_EMPTY to assert FIFO_RD_EN at the end of startup sequence and instead use one of the subsequent FIFO_EMPTY pulses.

In this case FIFO_RD_EN might never assert and as a result no data will get read out of the FIFO.

Affected Designs:

- 1G BASE-X IPs for UltraScale (Version 16.1 rev 5)

- 1G BASE-X and SGMII IPs for UltraScale+ (Version 16.1 rev 5)

解决方案

This behavior applies to RX_BITSLICE, RXTX_BITSLICE, and ISERDESE3 for all UltraScale and UltraScale+ devices.

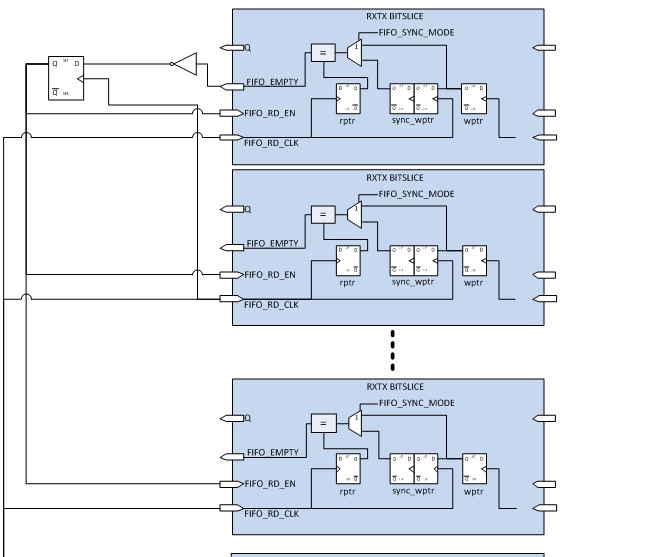

The solution is to use the first de-assertion of FIFO_EMPTY after reset to assert FIFO_RD_EN.

The FIFO_RD_EN circuitry should use the first de-assertion of FIFO_EMPTY as shown below.

The FIFO_EMPTY from the Bitslice furthest from the strobe is typically used.

In the case of multiple FIFO_EMPTY signals being used, NOR all of the FIFO_EMPTY signals to ensure that FIFO_RD_EN is asserted after the FIFO_WR_CLK has started for all of the Bitslices.

The fix has been included in the following version of the IP:

- 1G BASE-X IP for UltraScale (Version 16.1 rev 6)

- 1G BASE-X and SGMII for UltraScale+ (Version 16.1 rev 6)