AR# 72044

|UltraScale/UltraScale+ Memory IP - Default Vivado Simulation Behavior Change in 2018.2 and Later Versions

描述

Version Found: All memory IP Example Designs in Vivado 2018.2 and later versions

Version Resolved : See (Xilinx Answer 58435)

In previous versions of Vivado, when simulating the IP Example Design the Simulation Language was set to Mixed. As a result, the simplified behavioral test bench for the IP was executed.

The simplified test bench skips the calibration process and is fully supported with Vivado simulator.

Starting with Vivado 2018.2, the default Simulation Language is set to Verilog. When trying to simulate the IP Example Design with the Simulation Language set to Verilog, the tools will try to run a netlist simulation.

When using Vivado simulator the simulation will not start or will not run correctly. When using other simulators the simulation time will be extremely long because it is executing the entire calibration sequence.

解决方案

In order to run the Example Design simulation that skips the calibration sequence, the Simulation Language must be set to Mixed for all target simulators.

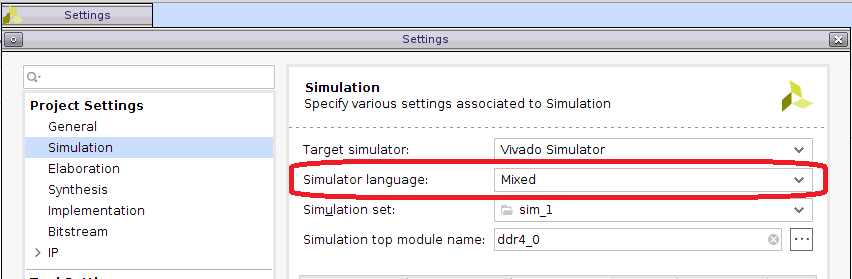

To make this change, click on the Settings button under the Project Manager heading in the Vivado Flow Navigator GUI:

Next change the "Simulation language" option to "Mixed":

Press Apply to set the changes.

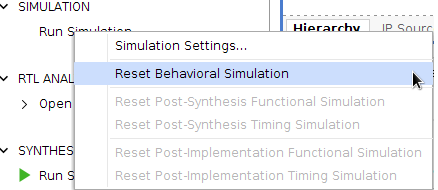

Next reset the simulation test bench by right-clicking on the Simulation heading in the Flow Navigator, and then select Reset Behavioral Simulation:

Now run the simulation as you normally would and it should return to the default behavior from previous versions of Vivado.

Revision History

02/20/2019 - Initial Release