AR# 71575

|JESD204B - Guidance when using multiple JESD204 RX cores to connect to one or more ADCs

描述

In certain circumstances it is necessary or desirable to connect multiple JESD204 RX cores to one or more ADCs.

This Answer Record provides guidance on how to correctly connect up multiple JESD204 RX cores and make sure there that is no latency difference between them.

解决方案

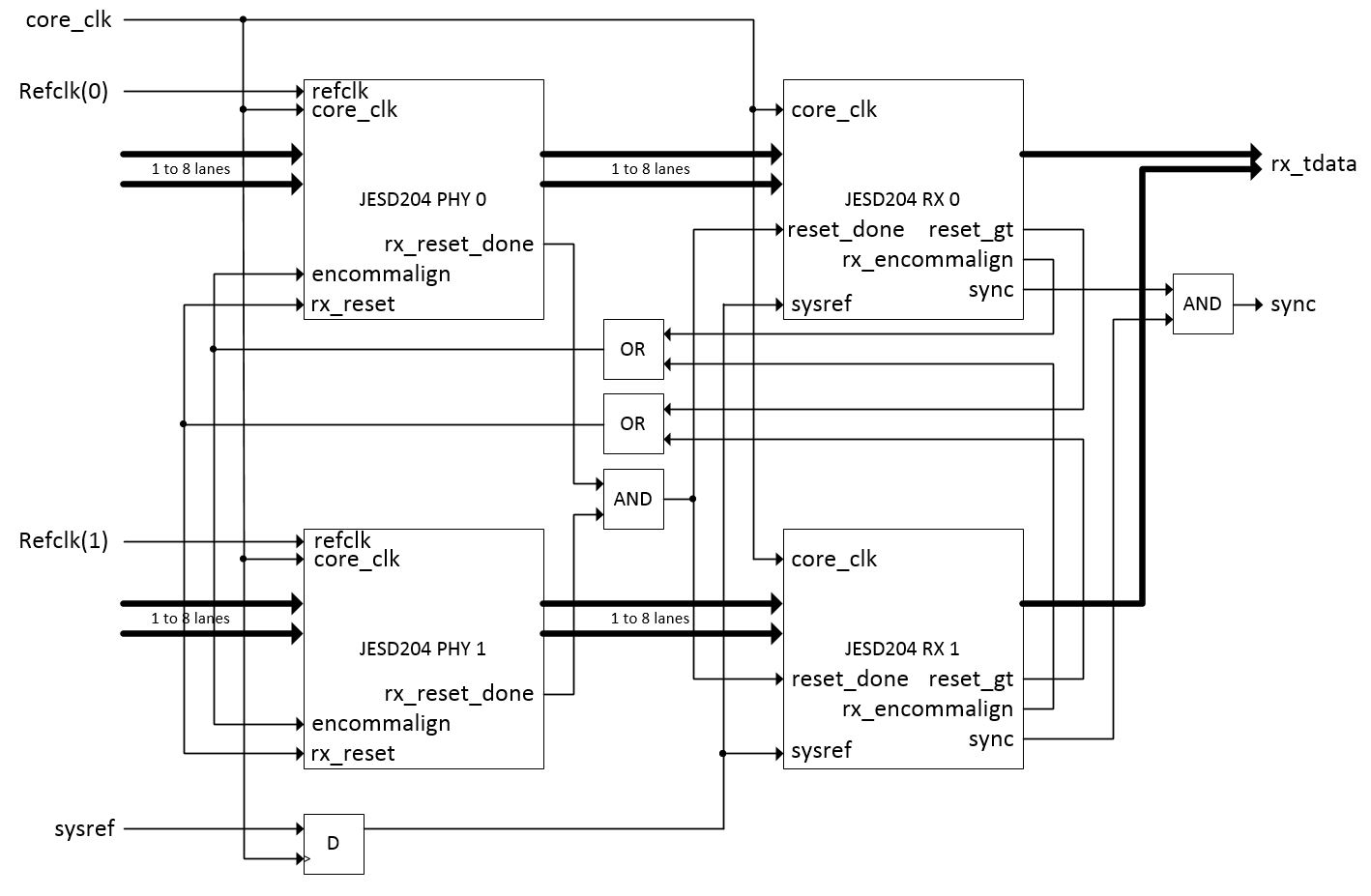

The block diagram below shows two JESD204 RX cores and two JESD204_PHY cores connected together.

The points to pay attention to are as follows.

- The whole system is synchronous and as such all clocks should be generated from a common source.

- Each JESD204_PHY core will require its own refclk.

- All JESD204_PHY cores and JESD204 RX cores will share a single common core_clk.

- Both "separate refclk and core_clk" and "refclk as core_clk" clocking schemes are supported (see (PG066) for details).

However if "refclk as core_clk" is used then core_clk will be generated from only one of the refclks. - core_clk is used as the AXI stream clock for both JESD204 RX AXI-Stream data interfaces.

- To ensure successful capture of SYSREF by both JESD204 RX cores, a D type flip flop should be placed on the input SYSREF signal.

The output of this should then be fed into both JESD204 RX cores.

The Tsu Thd requirements of this flip flop w.r.t core_clk must be met. - The ANDed SYNC signal should be used to drive all ADCs

The output of both JESD204 RX cores will be aligned with no latency differences if the above is implemented correctly.

To confirm this:

- Monitor the AXI stream rx_tvalid signals. They should both be asserted high on the same core_clk cycle.

- Monitor the start/end of frame/multiframe signals. They should be identical.

Revision History:

10/16/2018 - Initial Release

本答复记录是否对您有帮助?

| AR# 71575 | |

|---|---|

| 日期 | 10/16/2018 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| IP | |

People Also Viewed