AR# 71314

|Guidance and Mitigation for Configuration Readback induced Time Interval Error in MMCMs and PLLs

描述

Summary:

Configuration Readback exercises data lines that have a small amount of coupling into the VCO of the MMCM and PLLs.

As a result, varying amounts of increased Time Interval Error (TIE) jitter can be observed on a small subset of circuits.

Any use of configuration readback will result in the same effect.

This includes Readback CRC, SEM-IP, internal or external SEU scrubbing, and other configuration readback activities.

See the solution below for details on what types of circuits are affected and how to detect and mitigate them accordingly.

Design Impact:

In a design with configuration readback:

- Only MMCMs and/or PLLs are affected.

- GTs, Memory, and all other standalone blocks (BRAM, DSP, Fabric, etc.) are not affected

Device Impact:

- 7 Series: Both the MMCM and PLLs are impacted

- UltraScale: Both the MMCM and PLLs are impacted

- UltraScale+: No impact

- For UltraScale devices: Refer to the Vivado tools 2020.1.1 and new sections below.

解决方案

Below you will find the types of designs affected by the configuration readback induced TIE jitter increase and the mitigation recommendations for each use case.

Use Case #1:

Design features:

Designs involving synchronous clock domain crossing between clocks from:

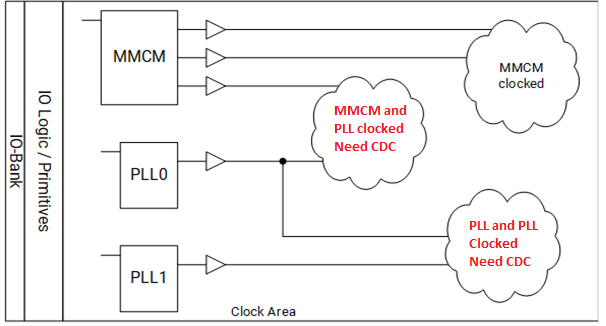

- MMCM and a PLL ( Including MMCM->PLL cascade and MMCM) (Fig 1)

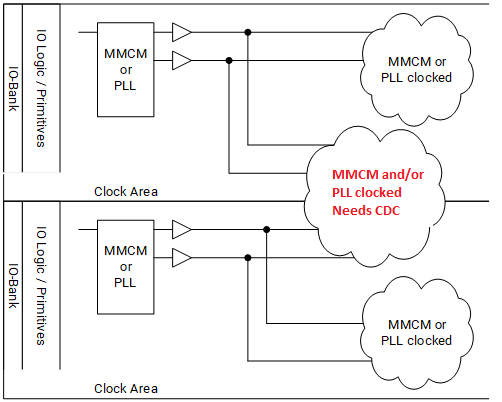

- Two MMCMs in different banks (Fig 2)

- Two PLLs in different banks (Fig 2)

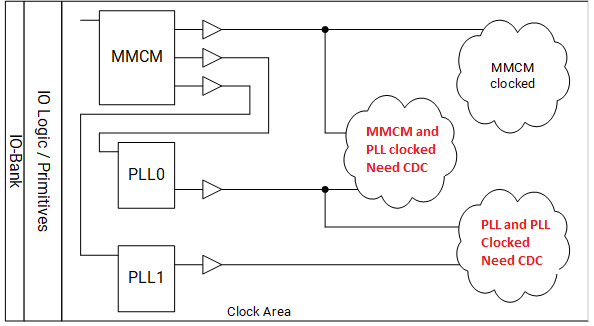

- MMCM->PLL cascade and PLL, even if in the same bank (Fig 3)

Figure 1: Designs involving synchronous CDC between clocks from an MMCM and a PLL

Figure 2: Designs involving synchronous CDC between clocks from MMCMs/PLLs in two different banks

Figure 3: Designs involving synchronous CDC between clocks from MMCM ->PLLs cascade and a PLL

Assessment steps:

Total TIE jitter increase on a clock output as a result of readback CRC is a function of input clock frequency, VCO frequency (M divider value), and the type of clock management element used (MMCM or PLL or MMCM->PLL cascade).

In 7 Series devices, the jitter effect due to readback CRC is worse for a PLL than a MMCM. Conversely, in UltraScale devices the jitter effect due to readback CRC is worse for an MMCM than a PLL.

Additionally, the MMCM/PLLs residing in different banks are affected independently by the TIE jitter effect, due to the row-by-row readback CRC scanning sequence and because different banks are in different rows of the device architecture.

These factors can cause a timing margin reduction in the CDC paths involving clocks from the clocking configurations described above.

Please use the following references provided by Xilinx to assess TIE increase based on the clock topology used on all CDC paths in the categories described above.

7 Series:

MMCM and PLL: Refer to the following table:

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | |

|---|---|---|

| MMCM (Default BW) | > 25MHz | 0 |

| <= 25MHz | 400 | |

PLL (Default BW) | ||

| > 50 MHz | 200 | |

| 25 < X <= 50MHz | 400 | |

< 25MHz | 1000 |

This factor will be applied as an additional timing constraint to the CDC paths affected by this issue after running the attached script.

If there is enough timing margin left with the additional constraints, the system is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the 7 Series mitigation section below.

7 Series Mitigation steps:

- Consolidate the critical paths to use only one clock management element, if possible - one MMCM clocking the entire path

- If PLL is used, switch to MMCM

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

- Rerun the attached script

Re-assess timing margins after trying some or all of these changes.

UltraScale: (Vivado tools 2020.1.1 and newer)

Important Note: The BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH properties can be set to POSTCRC but do not function correctly in Vivado tools versions 2019.2 through 2020.1, and the POSTCRC setting in these Vivado tools versions can cause the PLL or MMCM to fail to lock.

Only use this POSTCRC setting with Vivado tools 2020.1.1 or later. For designs in Vivado tools 2020.1 and earlier, see the UltraScale Mitigation steps: (Vivado tools 2020.1 and older) section.

Set the applicable write_bitstream property shown below to optimize the PLL/MMCM's settings to reduce the varying amounts of configuration readback induced TIE jitter.

**set_property BITSTREAM.PLL.BANDWIDTH POSTCRC [current_design]

**set_property BITSTREAM.MMCM.BANDWIDTH POSTCRC [current_design]

Note: Refer to (UG908) for details on write_bitstream properties.

PLL: Refer to the following table:

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | Timing Margin erosion due to TIE Jitter increase as a result of readback applying write_bitstream properties (ps) | |

|---|---|---|---|

PLL (Default BW) | > 400 | +/- 125 | +/- 105 |

| 200 < X <= 400 MHz | +/- 175 | +/- 130 | |

| 100 < X <= 200 MHz | +/- 240 | +/- 165 | |

<= 100 MHz (except M = 16) | +/- 260 | +/- 185 | |

| <= 100 MHz (M=16) | +/- 190 | +/- 115 |

MMCM: Refer to the following Equations to determine Timing Margin erosion due to TIE Jitter increase as a result of configuration readback (ps)

Equation: (Vivado tools 2020.1.1 and newer with write_bitstream BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH property set to POSTCRC)

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

A = -0.0819*(M)^2 - 5.7699*(M) - 405.03

B = 1.1648*(M)^2 - 39.737*(M) + 2953.7

M = Feedback divide ratio = VCO frequency / Reference frequency

Equation: (Vivado tools 2020.1 and older)

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

M = Feedback divide ratio = VCO frequency / Reference frequency

This factor will be applied as an additional timing constraint to the CDC paths affected by this issue after running the attached script.

If there is enough timing margin left with the additional constraints, the system is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the UltraScale mitigation section below.

UltraScale Mitigation steps: (Vivado tools 2020.1 and older)

- Consolidate the critical paths to use only one clock management element, if possible - one PLL clocking the entire path

- If MMCM is used, switch to PLL.

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

- Rerun the attached script

Re-assess timing margins after trying some or all of these changes.

Use Case #2:

Design features:

System Synchronous (or synchronous phase unknown) or Asynchronous Select I/O receiver interfaces.

Assessment steps:

Total TIE jitter increase on a clock output as a result of readback CRC is a function of input clock frequency, VCO frequency (M divider value), and the type of clock management element used (MMCM or PLL or MMCM->PLL cascade).

In 7 Series devices, the jitter effect due to readback CRC is worse for a PLL than a MMCM. Conversely, in UltraScale devices, the jitter effect due to readback CRC is worse for an MMCM than a PLL.

These effects can reduce the overall receiver margins in I/O interfaces requiring static/dynamic phase tracking to center the data with respect to an asynchronous or synchronous phase-unknown clock coming in through an MMCM or a PLL.

Please use the following reference provided by Xilinx to assess TIE increase based on the clock topology used.

7 Series:

MMCM and PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback(ps) | |

|---|---|---|

| MMCM (Default BW) | > 25MHz | 0 |

| <= 25MHz | 400 | |

PLL (Default BW) | ||

| > 50 MHz | 200 | |

| 25 < X <= 50MHz | 400 | |

< 25MHz | 1000 |

This factor will be applied as additional error (Data Valid window closure) for the receiver margin calculations.

If there is enough receiver margin left with the additional error, the receiver interface is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the 7 Series mitigation section below.

7 Series Mitigation Steps:

- If PLL is used, switch to MMCM.

- Get rid of MMCM->PLL cascade, if any

- Increase input clock frequency to the maximum frequency possible

- Increase VCO frequency to the maximum possible

UltraScale: (Vivado tools 2020.1.1 and newer)

Important Note: The BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH properties can be set to POSTCRC but do not function correctly in Vivado tools versions 2019.2 through 2020.1, and the POSTCRC setting in these Vivado tools versions can cause the PLL or MMCM to fail to lock.

Only use this POSTCRC setting with Vivado tools 2020.1.1 or later. For designs in Vivado tools 2020.1 and earlier, see the UltraScale Mitigation steps: (Vivado tools 2020.1 and older) section.

**set_property BITSTREAM.PLL.BANDWIDTH POSTCRC [current_design]

**set_property BITSTREAM.MMCM.BANDWIDTH POSTCRC [current_design]

Note: Refer to (UG908) for details on write_bitstream properties.

PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | Timing Margin erosion due to TIE Jitter increase as a result of readback applying write_bitstream properties (ps) | |

|---|---|---|---|

PLL (Default BW) | > 400 | +/- 125 | +/- 105 |

| 200 < X <= 400 MHz | +/- 175 | +/- 130 | |

| 100 < X <= 200 MHz | +/- 240 | +/- 165 | |

<= 100 MHz (except M = 16) | +/- 260 | +/- 185 | |

| <= 100 MHz (M=16) | +/- 190 | +/- 115 |

MMCM: Refer to the following equations to determine Timing Margin erosion due to TIE Jitter increase as a result of configuration readback (ps)

Equation: (Vivado tools 2020.1.1 and newer with write_bitstream BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH property set to POSTCRC)

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

A = -0.0819*(M)^2 - 5.7699*(M) - 405.03

B = 1.1648*(M)^2 - 39.737*(M) + 2953.7

M = Feedback divide ratio = VCO frequency / Reference frequency

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

M = Feedback divide ratio = VCO frequency / Reference frequency

This factor will be applied as additional error (Data Valid window closure) for the receiver margin calculations.

If there is enough receiver margin left with the additional error, the receiver interface is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the UltraScale mitigation section below.

UltraScale Mitigation Steps: (Vivado tools 2020.1 and older)

- If MMCM is used, switch to PLL.

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

Re-assess receiver margins after trying some or all of these changes.

Use Case #3:

Design features:

Transmit I/O interfaces with no associated forwarded clock (System synchronous or asynchronous interface transmitters)

Total TIE jitter increase on a clock output as a result of readback CRC is a function of input clock frequency, VCO frequency (M divider value) and the type of clock management element used (MMCM or PLL or MMCM->PLL cascade).

In 7 Series the jitter effect due to readback CRC is worse for a PLL than an MMCM. Conversely, in UltraScale the jitter effect due to readback CRC is worse for an MMCM than a PLL.

Please use the following reference provided by Xilinx to assess TIE increase based on the clock topology used.

7 Series:

MMCM and PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | |

|---|---|---|

| MMCM (Default BW) | > 25MHz | 0 |

| <= 25MHz | 400 | |

PLL (Default BW) | ||

| > 50 MHz | 200 | |

| 25 < X <= 50MHz | 400 | |

< 25MHz | 1000 |

This factor will be applied as additional transmit error (Data Valid window closure) to the far-end receiver margin calculations.

If there is enough receiver margin left, the system is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the 7 Series mitigation section below.

7 Series Mitigation Steps:

- If PLL is used, switch to MMCM.

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

Re-assess system margin after trying some or all of these changes.

UltraScale: (Vivado tools 2020.1.1 and newer)

Important Note: The BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH properties can be set to POSTCRC but do not function correctly in Vivado tools versions 2019.2 through 2020.1, and the POSTCRC setting in these Vivado tools versions can cause the PLL or MMCM to fail to lock.

Only use this POSTCRC setting with Vivado tools 2020.1.1 or later. For designs in Vivado tools 2020.1 and earlier, see the UltraScale Mitigation steps: (Vivado tools 2020.1 and older) section.

**set_property BITSTREAM.PLL.BANDWIDTH POSTCRC [current_design]

**set_property BITSTREAM.MMCM.BANDWIDTH POSTCRC [current_design]

Note: Refer to (UG908) for details on write_bitstream properties.

PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | Timing Margin erosion due to TIE Jitter increase as a result of readback applying write_bitstream properties (ps) | |

|---|---|---|---|

PLL (Default BW) | > 400 | +/- 125 | +/- 105 |

| 200 < X <= 400 MHz | +/- 175 | +/- 130 | |

| 100 < X <= 200 MHz | +/- 240 | +/- 165 | |

<= 100 MHz (except M = 16) | +/- 260 | +/- 185 | |

| <= 100 MHz (M=16) | +/- 190 | +/- 115 |

MMCM: Refer to the following equation to determine Timing Margin erosion due to TIE Jitter increase as a result of configuration readback (ps).

Equation: (Vivado tools 2020.1.1 and newer with write_bitstream BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH property set to POSTCRC)

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

A = -0.0819*(M)^2 - 5.7699*(M) - 405.03

B = 1.1648*(M)^2 - 39.737*(M) + 2953.7

M = Feedback divide ratio = VCO frequency / Reference frequency

Where:

M = Feedback divide ratio = VCO frequency / Reference frequency

This factor will be applied as additional transmit error (Data Valid window closure) to the far-end receiver margin calculations.

If there is enough receiver margin left, the system is immune to readback CRC induced jitter and no further actions are needed. If not, please refer to the UltraScale mitigation section below.

UltraScale Mitigation Steps: (Vivado tools 2020.1 and older)

- If MMCM is used, switch to PLL.

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

Re-assess system margin after trying some or all of these changes.

Use Case #4:

Design features:

Source Synchronous Transmit I/O interfaces with data/clock spanning more than 1 bank that are clocked by clock management elements (MMCMs or PLLs) from multiple banks.

Assessment steps:

Total TIE jitter increase on a clock output as a result of readback CRC is a function of input clock frequency, VCO frequency (M divider value), and the type of clock management element used (MMCM or PLL or MMCM->PLL cascade).

In 7 Series the jitter effect due to readback CRC is worse for a PLL than a MMCM. Conversely, in UltraScale the jitter effect due to readback CRC is worse for an MMCM than a PLL.

Readback CRC happens one row at a time. The TIE jitter increase due to this activity is not seen on the clock outputs of MMCM/PLLs residing in different banks simultaneously.

This will lower the system margin on interfaces that span multiple banks that are clocked by MMCMs or PLLs from more than 1 bank and are required to have a fixed phase relationships at the far end.

Please use the following reference provided by Xilinx to assess TIE increase based on the clock topology used.

7 Series:

MMCM and PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | |

|---|---|---|

| MMCM (Default BW) | > 25MHz | 0 |

| <= 25MHz | 400 | |

PLL (Default BW) | ||

| > 50 MHz | 200 | |

| 25 < X <= 50MHz | 400 | |

< 25MHz | 1000 |

This factor will be applied as additional transmit error (Data Valid window closure) for the far-end receiver margin calculations.

If there is enough receiver margin left, the system is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the 7 Series mitigation section below.

7 Series Mitigation Steps:

- Consolidate the interface to use only one clock management element, if possible - one MMCM clocking the entire interface.

- If PLL is used, switch to MMCM.

- Get rid of the MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

Re-assess system margin after trying some or all of these changes.

UltraScale: (Vivado tools 2020.1.1 and newer)

Important Note: The BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH properties can be set to POSTCRC but do not function correctly in Vivado tools versions 2019.2 through 2020.1, and the POSTCRC setting in these Vivado tools versions can cause the PLL or MMCM to fail to lock.

Only use this POSTCRC setting with Vivado tools 2020.1.1 or later. For designs in Vivado tools 2020.1 and earlier, see the UltraScale Mitigation steps: (Vivado tools 2020.1 and older) section.

**set_property BITSTREAM.PLL.BANDWIDTH POSTCRC [current_design]

**set_property BITSTREAM.MMCM.BANDWIDTH POSTCRC [current_design]

Note: Refer to (UG908) for details on write_bitstream properties.

PLL: Refer to the following table

| REFCLK Frequency (MHz) | Timing Margin erosion due to TIE Jitter increase as a result of readback (ps) | Timing Margin erosion due to TIE Jitter increase as a result of readback applying write_bitstream properties (ps) | |

|---|---|---|---|

PLL (Default BW) | > 400 | +/- 125 | +/- 105 |

| 200 < X <= 400 MHz | +/- 175 | +/- 130 | |

| 100 < X <= 200 MHz | +/- 240 | +/- 165 | |

<= 100 MHz (except M = 16) | +/- 260 | +/- 185 | |

| <= 100 MHz (M=16) | +/- 190 | +/- 115 |

MMCM: Refer to the following equation to determine Timing Margin erosion due to TIE Jitter increase as a result of configuration readback (ps).

Equation: (Vivado tools 2020.1.1 and newer with BITSTREAM.PLL.BANDWIDTH and BITSTREAM.MMCM.BANDWIDTH property set to POSTCRC)

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

A = -0.0819*(M)^2 - 5.7699*(M) - 405.03

B = 1.1648*(M)^2 - 39.737*(M) + 2953.7

M = Feedback divide ratio = VCO frequency / Reference frequency

CFG_RDBK TIE jitter(ps) = A* ln(Reference_freq in MHz) + B

Where:

M = Feedback divide ratio = VCO frequency / Reference frequency

This factor will be applied as additional transmit error (Data Valid window closure) for the far-end receiver margin calculations.

If there is enough receiver margin left, the system is immune to readback CRC induced jitter and no further actions are needed.

If not, please refer to the UltraScale mitigation section below.

UltraScale Mitigation Steps: (Vivado tools 2020.1 and older)

- Consolidate the interface to use only one clock management element, if possible - one PLL clocking the entire interface.

- If MMCM is used, switch to PLL.

- Get rid of MMCM->PLL cascade, if any

- Increase the input clock frequency to the maximum frequency possible

- Increase the VCO frequency to the maximum possible

Re-assess system margin after trying some or all of these changes.

Vivado tools 2019.2 through 2020.1

The two new bitstream bandwidth properties also exist in Vivado tools 2019.2-2020.1.

However, these two properties must NOT be set in Vivado tools 2019.2-2020.1. In Vivado tools 2019.2-2020.1, these property settings can cause lock failures.

set_property BITSTREAM.PLL.BANDWIDTH POSTCRC [current_design]

set_property BITSTREAM.MMCM.BANDWIDTH POSTCRC [current_design]

The above two bitstream bandwidth properties should only be used with Vivado tools 2020.1.1 or later.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| TIE_Checker.tcl | 19 KB | TCL |