AR# 71191

|UltraScale+ FPGA Integrated Endpoint Block for PCI Express / PCIe UltraScale+ 4c / UltraScale Architecture PHY for PCI Express (Vivado 2018.1) - Link does not train in Gen1 design with Refclk at 125 MHz and 250 MHz speeds

描述

Version Found: Vivado 2018.1

Version Resolved and other Known Issues:

- UltraScale+ PCI Express Integrated Block (Xilinx Answer 65751)

- UltraScale Architecture PHY for PCI Express (Xilinx Answer 66988)

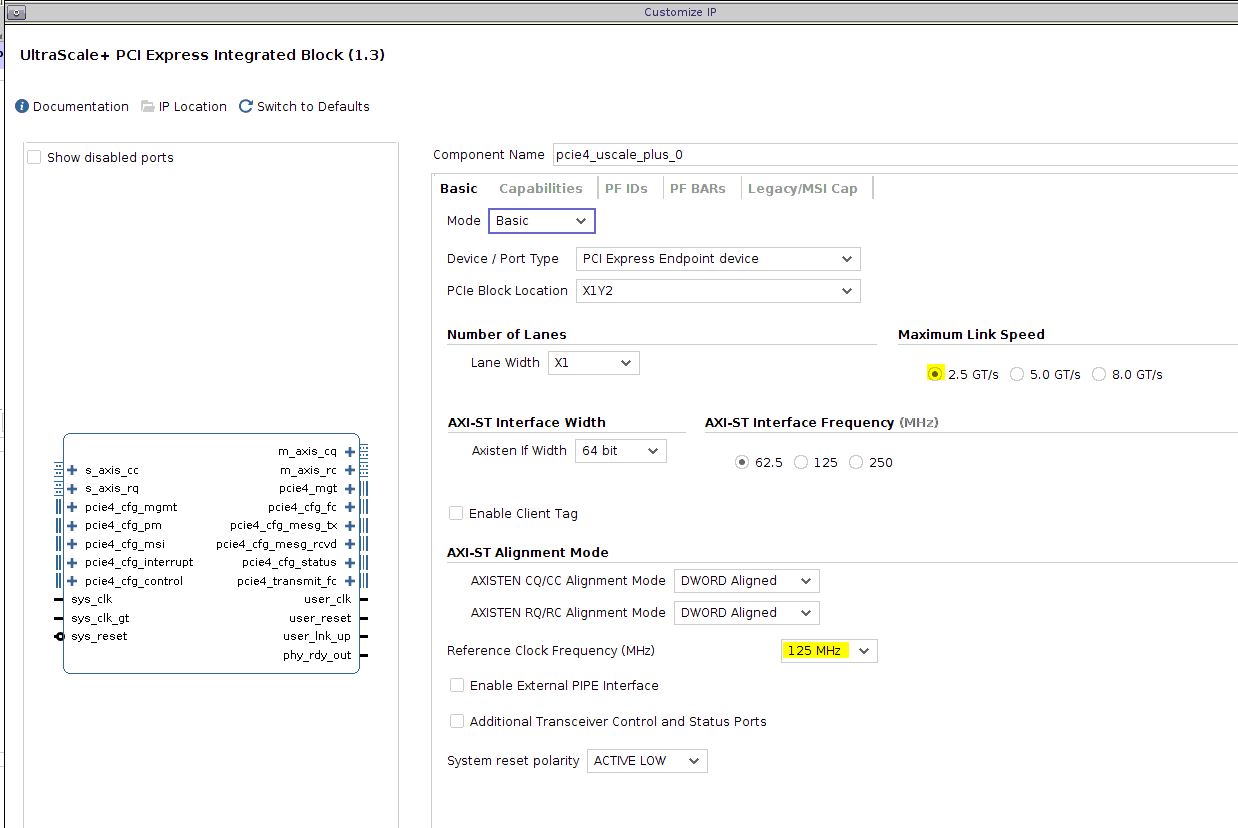

When selecting a system Reference Clock at the 125 Mhz or 250 Mhz frequency, along with PCI Express Gen1 speed selection (2.5 GT/s), the generated core fails to link train in both hardware and simulation.

This is because the incorrect TXOUTCLK source is selected in the GT Wizard subcore, causing the TXPROGDIV_OUT to not be driven correctly. This stalls link training at txprogdiv_reset_done.

Additionally, if you generate the GT Wizard as part of the Example Design, the design will not synthesize due to a port mismatch.

This article is part of the PCI Express Solution Centre

| (Xilinx Answer 34536) | Xilinx Solution Center for PCI Express |

解决方案

The issues listed in this answer record will be fixed in a future release of the core.

For instructions on installing the patch, please check the instructions in the 'patch_readme' directory in the attached patch file.

This patch is specifically for the UltraScale+ FPGA Integrated Endpoint Block for PCI Express, PCIe UltraScale+ 4c, and UltraScale Architecture PHY for PCI Express in Vivado 2018.1.

Note: The "Version Found" lists the version where the problem was first discovered.

The problem also exists in earlier versions, but no specific testing has been performed to verify earlier versions.

Revision History:

06/12/2018 - Initial Release

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| AR71191_Vivado_2018_1_preliminary_rev1.zip | 3 MB | ZIP |

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 71147 | DMA / Bridge Subsystem for PCI Express (Vivado 2018.1) - Tactical patch for issue fixes | N/A | N/A |

| AR# 71191 | |

|---|---|

| 日期 | 06/15/2018 |

| 状态 | Active |

| Type | 已知问题 |

| IP | |