AR# 69405

|DMA / Bridge Subsystem for PCI Express and UltraScale+ PCI Express Integrated Block (Vivado 2017.2) - Tactical patch for issue fixes and enhancements

描述

Version Found:

- DMA / Bridge Subsystem for PCI Express v3.1 (Rev. 1) - (Vivado 2017.2)

- UltraScale+ PCI Express Integrated Block v1.2 (Rev. 1) - (Vivado 2017.2)

Version Resolved and other Known Issues: DMA Subsystem for PCI Express (Xilinx Answer 65443) / UltraScale+ PCI Express Integrated Block (Xilinx Answer 65751)

The issues listed in the patch might have existed in previous versions of the core.

The tactical patch provided with this Answer Record provides the following fixes and enhancements:

DMA / Bridge Subsystem for PCI Express v3.1 (Rev. 1) - (Vivado 2017.2)

All of the issues listed are for both DMA Mode and Bridge Mode

- Bug Fix: Added missing ports for 'Include GT Wizard in Example Design' mode

- Bug Fix: Corrected GT DRP address width for UltraScale+ device family

- Bug Fix: PIO failure for 'Include GT Wizard in Example Design' mode

- Bug Fix: Updated GT Wizard QPLL attributes

- Bug Fix: CPLL CAL inclusion for 'Include GT Wizard in Example Design' mode'

- Bug Fix: Corrected MSI-X Table Size to 'h1F (32 vectors)

- Feature Enhancement: Added option to enable external BUFG_GT/SYNC for sys_clk

- Feature Enhancement: Moved phy_clk module in support wrapper when selecting 'Include GT Wizard in Example Design mode'

- Feature Enhancement: New GT Sharing modes - GT Common in Example Design

All of the issues listed are for Bridge Mode only

- Bug Fix: Allow MSI-X Table and PBA registers to be programmed while MSI-X Enable bit in MSIX Control register is 0.

- Bug Fix: Updated GT Wizard QPLL attributes

- Bug Fix: CPLL CAL inclusion for 'Include GT Wizard in Example Design' mode'

- Bug Fix: PIO failure for 'Include GT Wizard in Example Design' mode

- Feature Enhancement: Added option to enable external BUFG_GT/SYNC for sys_clk

- Feature Enhancement: Moved phy_clk module in support wrapper when selecting Include GT Wizard in Example Design mode

- Feature Enhancement: New GT Sharing modes - GT Common in Example Design

This article is part of the PCI Express Solution Centre

解决方案

This issue will be fixed in the next release of the core. Please install the patch in Vivado 2017.1/2017.2 as described below:

METHOD 1:

- Navigate to the $XILINX_VIVADO/patches directory (create this directory if it does not exist)

- Extract the contents of the ".zip" archive to a directory starting with the name AR69405

Note: most extraction tools will allow you to automatically create a directory with the same name as the zip file - Run Vivado software tools from the original install location.

METHOD 2:

- Create a separate directory for the patched files

- Extract the contents of the ".zip" archive to the desired patch directory location

- Set the MYVIVADO environment variable to point to the Vivado directory under this patch directory

For example:

set MYVIVADO=C:\MYVIVADO\vivado-patch-AR69405vivado\ - Run Vivado software tools from the original install location.

Instantiate BUFG_GT / BUFG_GT_SYNC external to the IP and IP Properties:

This fixes an issue where sharing sys_clk from the PCI Express IBUFDS_GTE4 between two or more components causes design not to route.

This must be done prior to "Open Example Design". With this patch, after "Open Example Design" Step 3 & 4 will be exectued automatically.

- In DMA Subsystem for PCI Express or PCI Express Integrated Block, set the following property in the Vivado Tcl console:

- For non-IP Integrator (non-Block Design) flow:

set_property CONFIG.ext_sys_clk_bufg true [get_ips <ip_name>]

- For IP Integrator (Block Design) flow:

set_property CONFIG.ext_sys_clk_bufg true [get_bd_cells <ip_name>]

- Reset Output Products on the IP or your Block Design and Regenerate Output Products again to have the new settings applied to the design.

- Instantiate BUFG_GT and BUFG_GT_SYNC in your design as follows:

wire sys_clk_bufg;

wire sys_clk_ce_out;

wire sync_sc_ce;

wire sync_sc_clr.

BUFG_GT bufg_gt_sysclk (.CE (sync_sc_ce), .CEMASK (1'd0), .CLR (sync_sc_clr), .CLRMASK (1'd0), .DIV (3'd0), .I (sys_clk), .O (sys_clk_bufg));

BUFG_GT_SYNC sys_sys_clk (.CESYNC(sync_sc_ce), .CLRSYNC (sync_sc_clr), .CE(sys_clk_ce_out), .CLK(sys_clk), .CLR (1'b0));

- Add/Replace the following ports in your DMA Subsystem for PCI Express or PCI Express Integrated Block IP instantiation:

.sys_clk ( sys_clk_bufg ),

.sys_clk_ce_out (sys_clk_ce_out)

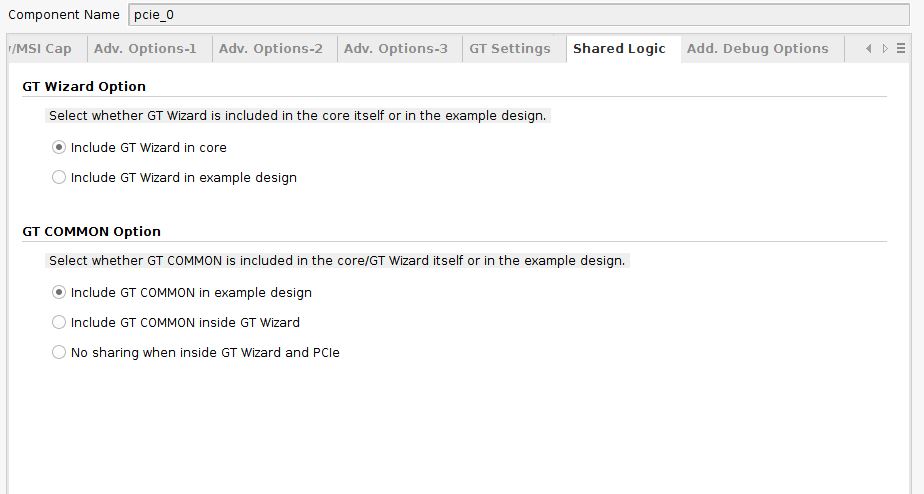

To share GT Common in the example design:

This feature is to be used when 2 different IPs need to use the same MGT Quad, and thus share the GT COMMON.

Previously, designs sharing the GT Common required 'Include GT Wizard in example design' mode, however, this has been simplified with the 'Include GT COMMON in example design' mode.

Note that different configurations will require different selections - please contact Xilinx Technical Support if you need assistance identifying the correct settings for a specific architecture.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| AR69405_Vivado_2017_2_preliminary_rev5.zip | 5 MB | ZIP |

| AR# 69405 | |

|---|---|

| 日期 | 05/04/2018 |

| 状态 | Active |

| Type | 已知问题 |

| 器件 | |

| Tools | |

| IP | |