AR# 68028

|UltraScale/UltraScale+ Memory IP - Pulse width violations occur for designs that violate the maximum BUFGCE timing spec with the Reference Input Clock Speed (ps)

描述

Version Found: DDR4 v2.1, DDR3 v1.3, RLDRAM3 v1.3, QDRII+ v1.3, QDRIV v1.2

Version Resolved: See (Xilinx Answer 58435)

The UltraScale Memory IP allows user to select the Reference Input Clock Speed (ps) based on the selected Memory Device Interface Speed (ps).

The IP uses the maximum MMCM timing specification to create the list of available Reference Input Clock Speeds.

However, because the input clock to the MMCM is driven by a BUFGCE, the maximum timing specifications of the BUFGCE should be used to limit the available input frequencies.

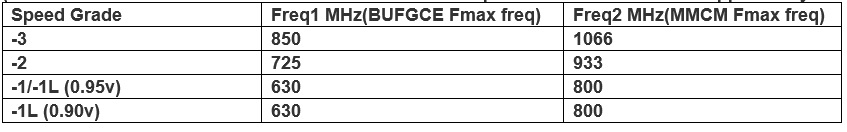

Here is an example of the differences in timing specifications between the BUFGCE and MMCM:

IP that use a Reference Clock Input Speed above the allowed BUFGE Fmax will see pulse width timing violations in the timing report.

解决方案

To resolve these errors, a reference clock must be selected that meets the BUFGCE Fmax datasheet specification. Future versions of the UltraScale Memory IP will adhere to the BUFGCE Fmax limits.

Revision History:

10/05/2016 - Initial Release

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 58435 | MIG UltraScale - IP Release Notes and Known Issues for Vivado 2014.1 and newer tool versions | N/A | N/A |