AR# 67551

|Vivado Simulator does not give any warning or error message when an integer goes out of range

描述

I have the following code in VHDL including a signal clk_count whose range is defined as integer range 0 to 4.

This signal is going out of range at simulation. However, Vivado Simulator is not displaying any error message at the simulation stage.

--------------------------------------------------

signal clk_count : INTEGER range 0 to 4;

clk_gen_adc: process(clk,reset)

begin

If(reset = ?1?) then

clk_count <= 0;

elsif rising_edge (clk) begin

If clk_count = 9 then

clk_count <= 0;

else

clk_count <= clk_count + 1;

endif;

endif;

end process;

------------------------------------------------

解决方案

Vivado Simulator does have a rangecheck option but it is disabled by default.

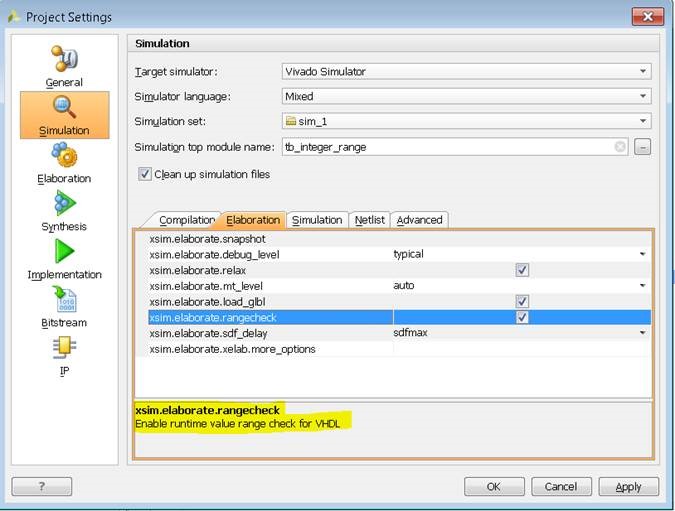

You will need to enable the rangecheck option in the simulation settings as shown in the below screen capture to turn on the error message.

After enabling the rangecheck option highlighted above, Vivado simulator stops when the value reaches 5 with the following error message:

ERROR: runtime range check value 5 is out of valid range 0 to 4.

Note: The rangecheck switch was disabled by default as it causes the compiler to generate extra code for the range check and slows down the simulation.

It is provided as an option which can be turned on in specific cases where you want the tool to perform rangecheck.

| AR# 67551 | |

|---|---|

| 日期 | 07/22/2016 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| Tools | |