AR# 65587

|UltraScale FPGA Gen3 Integrated Block for PCI Express v4.1 (Vivado 2015.3) - CRITICAL WARNING: [Timing 38-282] Negative SETUP slack violation

描述

Version Found: 4.1

Version Resolved and other Known Issues: (Xilinx Answer 57945)

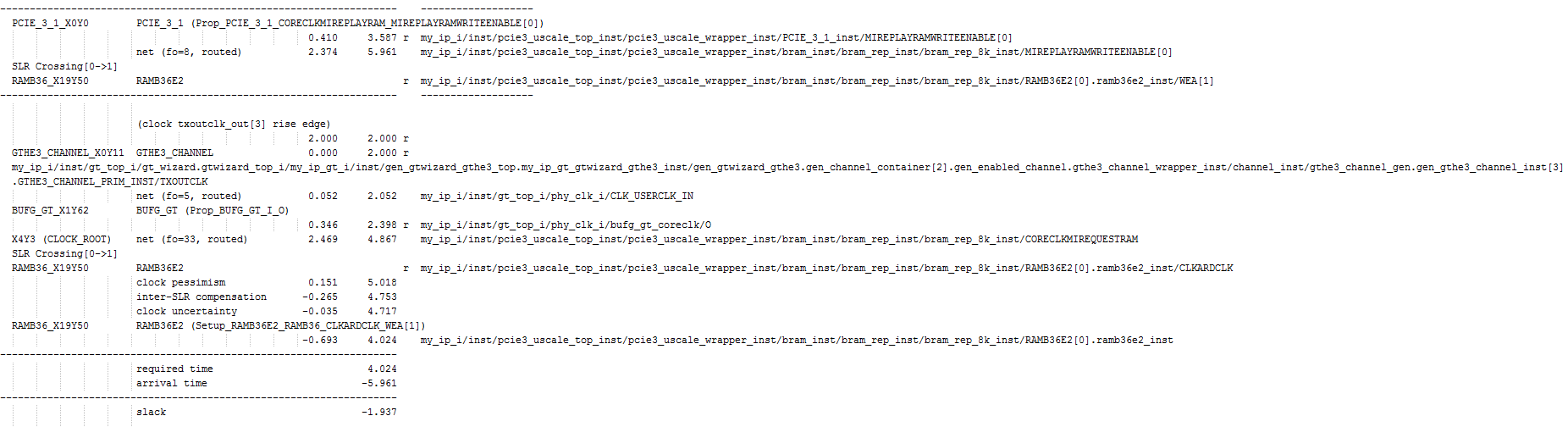

When implementing the UltraScale FPGA Gen3 Integrated Block for PCI Express core example design in Vivado 2015.3 for a XCVU160-FLGC2104 device, if I select PCIe Block X0Y0, the tool reports the following negative setup slack violation:

See (Xilinx Answer 34536) Xilinx Solution Center for PCI Express

解决方案

This issue is due to incorrect constraints in the IP XDC file. To resolve the issue, please update the IP XDC file as follows.

This will be fixed in the next release of the core.

Change the constraints from:

# Replay Buffer RAMB Placement

set_property LOC RAMB36_X19Y50 [get_cells {pcie3_uscale_top_inst/pcie3_uscale_wrapper_inst/bram_inst/bram_rep_inst/bram_rep_8k_inst/RAMB36E2[0].ramb36e2_inst}]

set_property LOC RAMB36_X19Y51 [get_cells {pcie3_uscale_top_inst/pcie3_uscale_wrapper_inst/bram_inst/bram_rep_inst/bram_rep_8k_inst/RAMB36E2[1].ramb36e2_inst}]

Change the constraints to:

# Replay Buffer RAMB Placement

set_property LOC RAMB36_X19Y46 [get_cells {pcie3_uscale_top_inst/pcie3_uscale_wrapper_inst/bram_inst/bram_rep_inst/bram_rep_8k_inst/RAMB36E2[0].ramb36e2_inst}]

set_property LOC RAMB36_X19Y47 [get_cells {pcie3_uscale_top_inst/pcie3_uscale_wrapper_inst/bram_inst/bram_rep_inst/bram_rep_8k_inst/RAMB36E2[1].ramb36e2_inst}]

Note: "Version Found" refers to the version the problem was first discovered.

The problem may also exist in earlier versions, but no specific testing has been performed to verify earlier versions.

Revision History:

10/08/2015 - Initial Release

| AR# 65587 | |

|---|---|

| 日期 | 10/23/2015 |

| 状态 | Active |

| Type | 已知问题 |

| IP | |