AR# 64718

|UltraScale FPGA Gen3 Integrated Block for PCI Express (Vivado 2015.1) - Incorrect refclk_buf location for XCVU095 - FFVC2104, XCVU190 - FLGA2577 and XCVU125 - FLVC2104

描述

Version Found: v4.0 (Vivado 2015.1)

Version Resolved and other Known Issues: See (Xilinx Answer 57945)

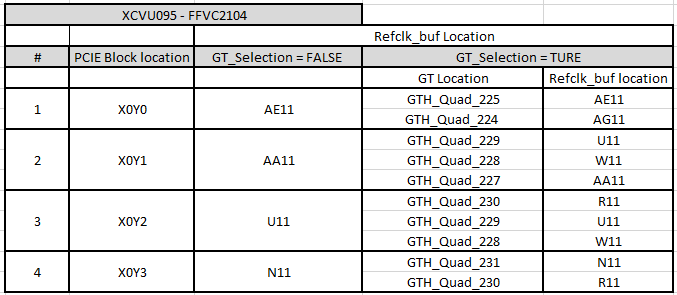

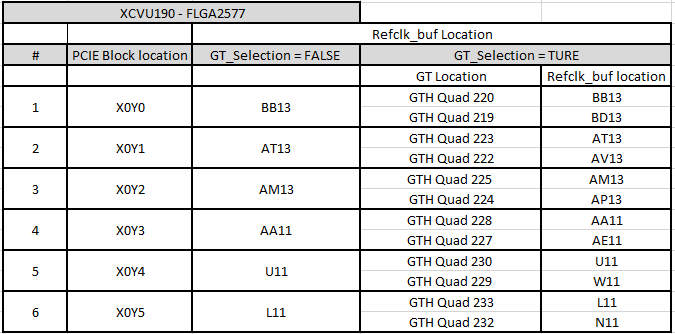

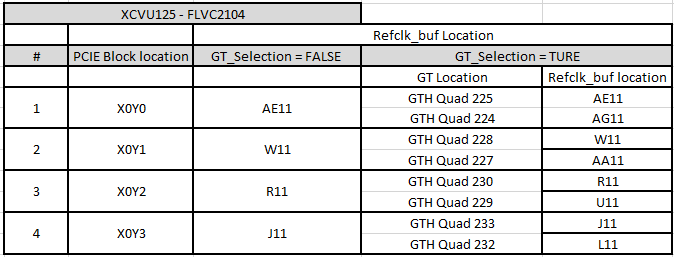

When generating UltraScale FPGA Gen3 Integrated Block for PCI Express core for the following devices, the generated XDC file consists of incorrect refclk_buf locations.

- XCVU095 - FFVC2104

- XCVU190 - FLGA2577

- XCVU125 - FLVC2104

解决方案

This is a known issue to be fixed in the next release of the core.

Please correct the constraints as follows:

Note: The "Version Found" column lists the version the problem was first discovered.

The problem also exists in earlier versions, but no specific testing has been performed to verify earlier versions.Revision History:

06/02/2015 - Initial Release

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 57945 | UltraScale FPGA Gen3 Integrated Block for PCI Express - Release Notes and Known Issues | N/A | N/A |

| AR# 64718 | |

|---|---|

| 日期 | 06/26/2015 |

| 状态 | Active |

| Type | 已知问题 |

| IP | |

People Also Viewed