AR# 63988

|How to run timing simulation using Vivado Simulator?

描述

You can perform timing simulation after Synthesis or Implementation.At the post-synthesis simulation stage, although it is not typical, you can perform timing simulation with estimated timing numbers.

At the post-implementation simulation stage, timing simulation is the closest emulation to actually downloading a design to a device.

It allows you to ensure that the implemented design meets functional and timing requirements and has the expected behavior in the device.

It allows you to ensure that the implemented design meets functional and timing requirements and has the expected behavior in the device.

NOTE: Post-Synthesis and Post-Implementation timing simulations are supported for Verilog only.

There is no support for VHDL timing simulation.

There is no support for VHDL timing simulation.

This article describes the two ways to run timing simulation using Vivado Simulator: from the Vivado IDE and from the command line.

解决方案

Vivado IDE:- In the Vivado project, run Synthesis or Implementation.

- Specify Vivado Simulator Simulation Settings if necessary.

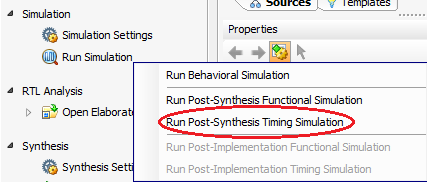

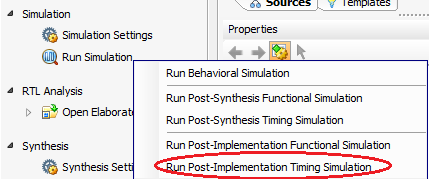

- From the Flow Navigator, select

Run Simulation > Run Post-Synthesis Timing Simulation

or

Run Simulation > Run Post-Implementation Timing Simulation.

The option becomes available only when synthesis or implementation is run successfully.

Run From Command Line:

- Generate a Verilog timing simulation netlist for the design.

open_checkpoint top.dcp

write_verilog -mode timesim -sdf_anno true top_timesim.v

2. Generate an SDF delay file with all the timing delays annotated.

Example:

write_sdf top_timesim.sdf

3. Parse the individual files or a project file, elaborate and generate a snapshot by appropriately annotating the SDF file, and then simulate.

The Vivado simulator models use interconnect delays.

As a result, additional switches are required for proper timing simulation, as follows:

The Vivado simulator models use interconnect delays.

As a result, additional switches are required for proper timing simulation, as follows:

-transport_int_delays -pulse_r 0 -pulse_int_r 0

Example:

xvlog top_timesim.v

xvlog testbench.v

xvlog $XILINX_VIVADO/data/verilog/src/glbl.v

xelab -debug typical -maxdelay -L secureip -L simprims_ver -transport_int_delays -pulse_r 0 -pulse_int_r 0 testbench glbl -s top_timesim

xsim top_timesim -gui

For more information on using Vivado Simulator and the command line options, please refer to (UG900) Vivado Design Suite User Guide: Logic Simulation.

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2015_1/ug900-vivado-logic-simulation.pdf

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 58879 | Xilinx 仿真解决方案中心 — 设计助手 — Vivado 仿真器 — 时序仿真 | N/A | N/A |

| AR# 63988 | |

|---|---|

| 日期 | 05/05/2015 |

| 状态 | Active |

| Type | 综合文章 |

| Tools | |

People Also Viewed