AR# 63149

|Design Advisory for Zynq-7000 SoC: Secure Lockdown triggered by PS_POR_B reset sequence

描述

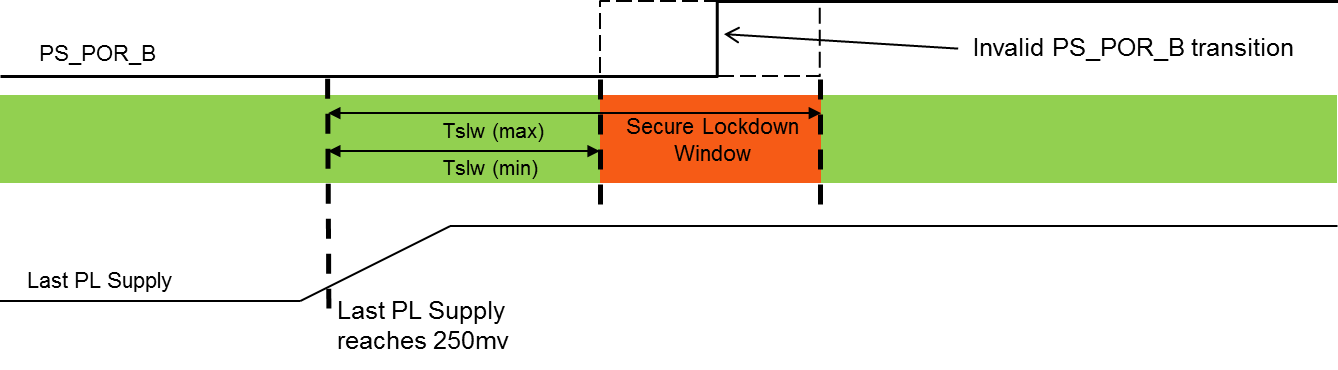

On initial device power up, when the PS PS_POR_B de-asserts within a certain timing window in relationship to power up of the last PL power supply (VCCINT, VCCBRAM, VCCAUX or VCCO_0), the device can enter Secure Lockdown state and will prevent boot from completing per the lockdown specification.

This window is defined as a minimum and maximum time relative to the last PL power supply ramp:

Tslw (min) = Time from last PL power supply reaching 250mv to start of Secure Lockdown Window

Tslw (max) = Time from last PL power supply reaching 250mv to end of Secure Lockdown Window

解决方案

How do I evaluate if my system is impacted?

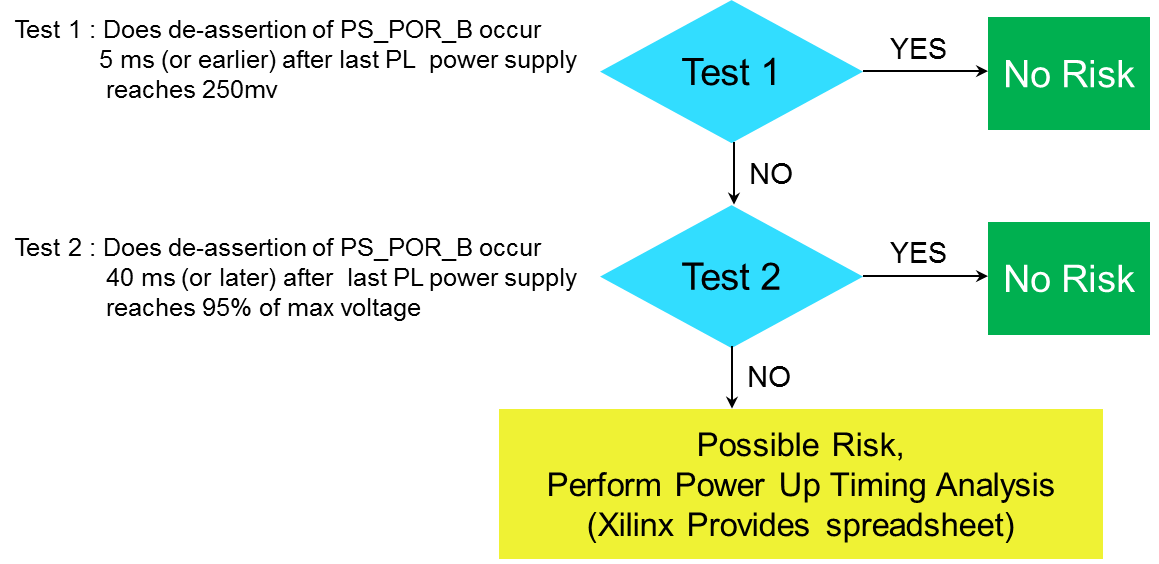

Tests 1 and 2 below can be performed on design specifications or optionally on hardware to evaluate if a specific system is impacted.

Important Test Assumptions: eFuse for 128K CRC is not enabled AND PLLs are not bypassed.

Steps for hardware testing:

- Identify probe points for PS_POR_B, VCCINT (PL), VCCAUX (PL), VCCBRAM, VCCO_0 (PL).

- For PL supply, identify the probe points near to the die, typically on the supply bypass capacitor.

- Use an oscilloscope to measure the relative time between the signals for Test 1 and Test 2.

In the "Possible Risk" scenario, the power up sequence and de-assertion timing of PS_POR_B must be analyzed to determine if it falls within the Secure Lockdown timing window (Tslw).

The Tslw min/max values are dependent on several system level factors (Zynq-7000 AP SoC Device, PS_CLK frequency, and PL power supply ramp time).

A Power Up Timing Spreadsheet Calculator has been created to determine this range based on the values from the customers system. This spreadsheet is attached.

As an example, a 7Z020 device with a 33.33 MHz PS_CLK and a 6ms PL power supply ramp time has a Secure Lockdown timing window (Tslw) of 13.45ms to 38.99ms after the last PL power supply started to ramp.

If PS_POR_B is de-asserted during this window, the device can enter Secure Lockdown state.

If PS_POR_B is de-asserted either before or after this window, the device is not exposed this behavior.

If PS_POR_B is de-asserted either before or after this window, the device is not exposed this behavior.

How to confirm that boot did not complete because of this event?

All of the following specific symptoms need to be present to confirm this issue is the root cause:

- If you do an initial power-up AND

- If you see a hang during boot AND

- If you do not see an access to your boot device AND

- If you see the PL JTAG TAP in the JTAG chain AND

- If you do not see the PS JTAG TAP in the JTAG chain AND

- INIT_B goes HIGH and stays HIGH after secure lockdown AND7. If PS_POR_B de-assertion falls inside the Secure Lockdown window

What solutions are available?

Xilinx has created multiple solutions to avoid the Secure Lockdown Window.

The solutions have been classified into the following categories.

- Change timing relationship between last PL power ramp and PS_POR_B using PCB level circuits (Preferred Solution)

- Change PS BootROM code execution time (*) to shift the window by

- enabling 128K CRC check by burning a PS eFuse bit or

- enabling PLL Bypass (**)

Please, open a Service Request with "Secure Lockdown Window" in the title ONLY after collecting the following:

- Results of the attached spreadsheet analysis (a snapshot of the timing in the spreadsheet)

- Scope-shots of PS_POR_B, VCCINT (PL), VCCAUX (PL), VCCBRAM, VCCO_0 (PL) and INIT_B (the time relationship between the signals is required)

NOTES:

(*): Changing the PS BootROM code execution time in systems that have stringent startup timing may not be desirable.

Longer execution times can be mitigated by using the register initialization functionality to optimize boot time (Refer Chapter 3 of Zynq 7000 Software Developers Guide and section 6.3.3 of Zynq 7000 Technical Reference Manual )

(**): A patch for 2014.4 FSBL is required for this method. See (Xilinx Answer 63576).

本答复记录是否对您有帮助?

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| ps_por_b_timing_calculator_rev1.0.xlsm | 46 KB | XLSM |

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 47915 | Zynq-7000 SoC 器件的设计咨询主答复记录 | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 63539 | Zynq-7000, ZC702 (Rev 1.1) is NOT impacted by Design Advisory 63149 "Secure Lockdown triggered by PS_POR_B reset sequence" | N/A | N/A |

| 63540 | Zynq-7000、ZC706(Rev 1.1、Rev 1.2 和 Rev 2.0)未受到设计咨询 63149“PS_POR_B 复位顺序触发的安全闭锁”的影响 | N/A | N/A |

| 56195 | Zynq-7000 SoC 设计咨询:适用于 ES 芯片的设计为什么现在不能通过生产芯片启动? | N/A | N/A |

| AR# 63149 | |

|---|---|

| 日期 | 05/28/2018 |

| 状态 | Active |

| Type | 设计咨询 |

| 器件 | |

People Also Viewed