AR# 57782

|MIG 7 Series DDR3 - Issues with sys_clk type in ZC706 reference design

描述

Version Found: v2.0 Rev1

Version Resolved: See (Xilinx Answer 54025)

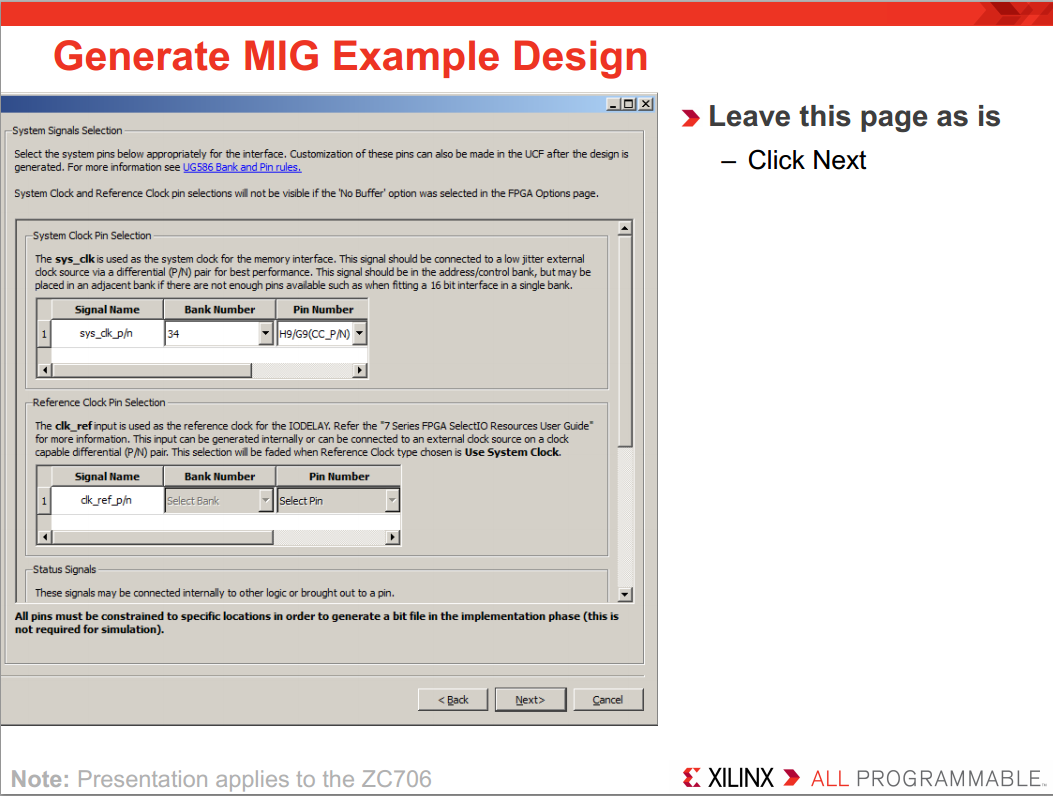

On page 28 of the ZC706 MIG Design Creation PDF (XTP244), the screenshot shows the correct pins selected for sys_clk and states that the page can be left as is and users can just click next:

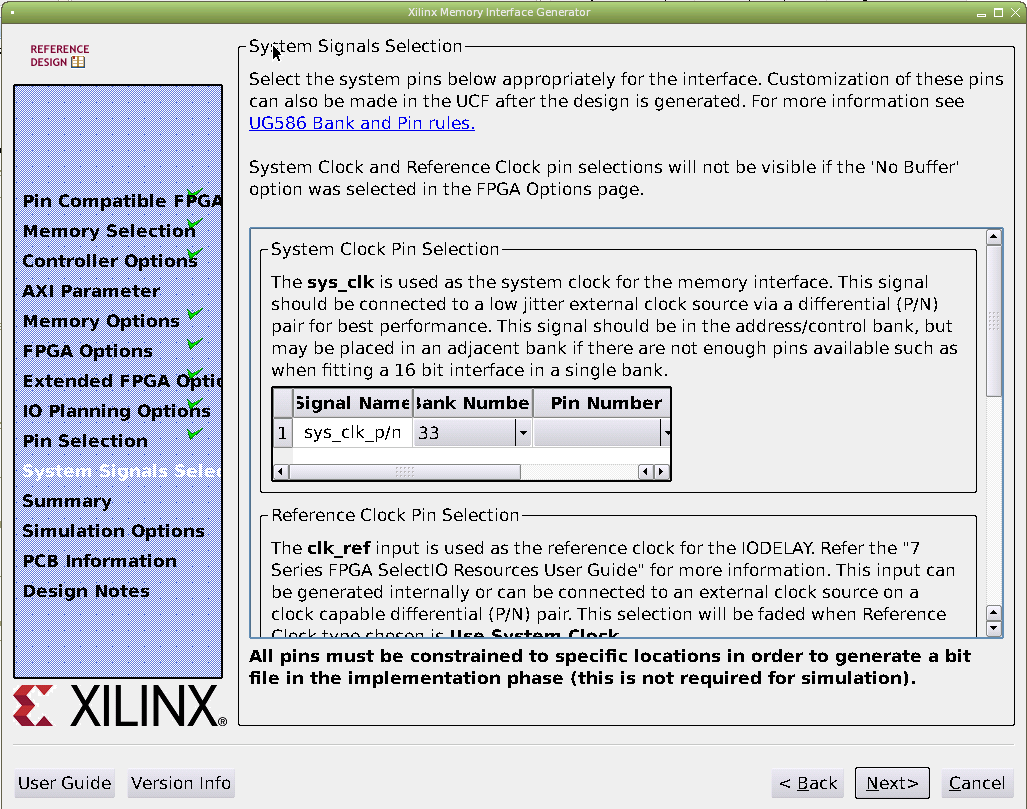

However, when running through the exact steps of the PDF slides, the System Signals Selection page chooses Bank 33 for the default sys_clk assignment, which has no available CCIOs. There is a bug in the MIG GUI which allows you to click Next and generate the core without assigning a pin to sys_clk, even though the sys_clk type is set to DIFFERENTIAL: see the screenshot below.

Typically, an error message is given stating the signal must be connected and the Next button is disabled. However, certain configurations, including the ZC706 MIG flow, allow the core to be build with no actual sys_clk pin assigned.

This causes issues when the IP Example Design is open or the core is regenerated. The mig_ex.tcl script regenerates the core and since no sys_clk pins are defined, the tools recognize this as the "NO BUFFER" option being used and switches the sysclk_type setting from "DIFFERENTIAL" to "NO BUFFER" in the regenerated IP. sysclk_type is still set to "DIFFERENTIAL" in the example_top.v and sim_tb_top.v, while the <core_name>.v top level file uses "NO BUFFER" and does not instantiate system clock signals. This contention between modules leads to synthesis and simulation errors.

解决方案

To avoid this problem, you need to manually select the proper sys_clk pins when generating a MIG core for the ZC706. On The System Signals Selection page, sys_clk_p/n needs to be assigned to H9/G9 in Bank 33 as shown in the screenshot of the PDF slide above.

Revision History

12/18/2013 - Initial release