AR# 57727

|Vivado Synthesis - Net names are not preserved by mark_debug

描述

There are situations after synthesis wherein the net names marked for debug via MARK_DEBUG constraint are not preserved, and as a result these debug nets are not available in the design for debugging purposes.

For example:

Reg RndData[0] -> pin Q -> net Q -> cell LUT RndDataxxx

In the above case, the original debug net associated with register RndData[0] changes name after synthesis, and takes the name of output pin Q.

What can be done to preserve the nets and make them available for Debugging in a design?

解决方案

This issue has been fixed in Vivado release 2014.2.

In the meantime, to work around this issue in 2014.1 and older versions, the following options are available:

Option 1:

Using the elaborated design, it is possible to find the correct net name whose names need to be preserved and set the correct MARK_DEBUG constraints in the XDC.

The correct name for the RndData net is Data because the net exits the module via port Data.

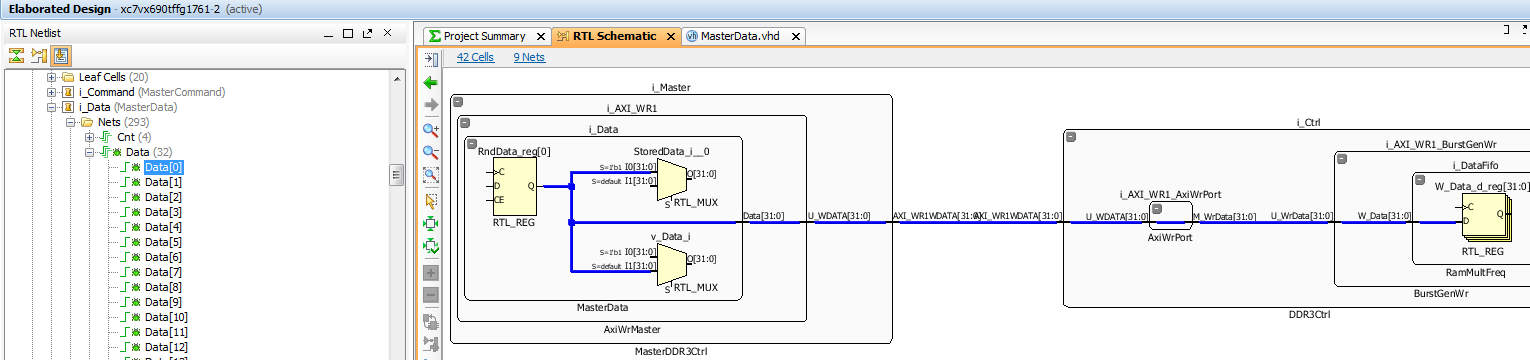

RTL Schematic:

After applying MARK_DEBUG constraint on these net names found via the elaborated design using set_property MARK_DEBUG true [get_nets ...], synthesis is able to correctly apply the constraints and preserve the nets.

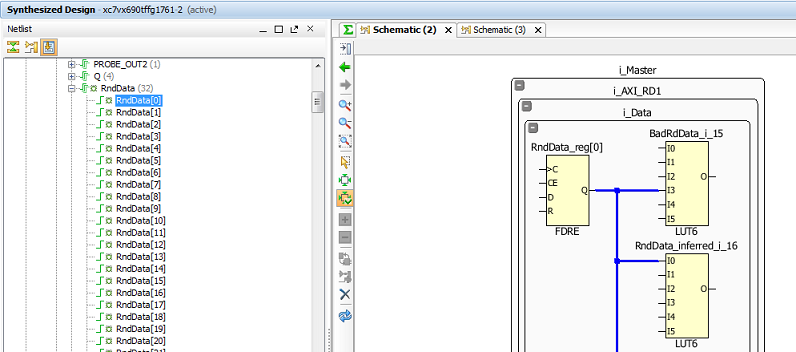

In the netlist, the net name does change, but the MARK_DEBUG properties are preserved.

This is an expected behavior as Vivado synthesis does rename ports in the default flatten_hierarchy rebuilt flow.

Vivado Synthesis Schematic:

Option 2: Run the design with flatten_hierarchy set to "none".

Option 3: Apply DONT_TOUCH on the instance (which can be done through XDC set_property DONT_TOUCH true [get_cells ...])

| AR# 57727 | |

|---|---|

| 日期 | 06/06/2014 |

| 状态 | Active |

| Type | 已知问题 |

| 器件 | |

| Tools | |