AR# 57261

|Xilinx HSSIO Solution Center - Design Assistant Digital Simulation of Serial Transceivers

描述

Digital simulation should be performed to verify the behavior of the digital side of a transceiver as well as its interface to user logic.

To this end, the wizard provides wrappers around a digital simulation model of the transceiver with every generated core.

These primitives model transceiver behavior as closely as possible and provide realistic system behavior in simulations.

They can, and should, be used to accurately simulate transceiver bring-up, resets, and interaction with user logic.

For each core generated by the wizard, an example design is also included which allows for immediate simulation of the chosen transceiver setup.

Below is a guide to digitally simulating the example designs provided by the transceiver wizard.

What is presented below is an overview, for a more detailed discussion see the Vivado Design Suite User Guide: Logic Simulation(UG900).

We recommend using the Document Navigator in the latest Vivado Version to find this, or any, User Guide.

Note: This article is part of the Xilinx HSSIO Solution Center and is available to address all questions related to HSSIO.

Whether you are starting a new design or troubleshooting a problem, use the HSSIO Solution Center to guide you to the right information.

解决方案

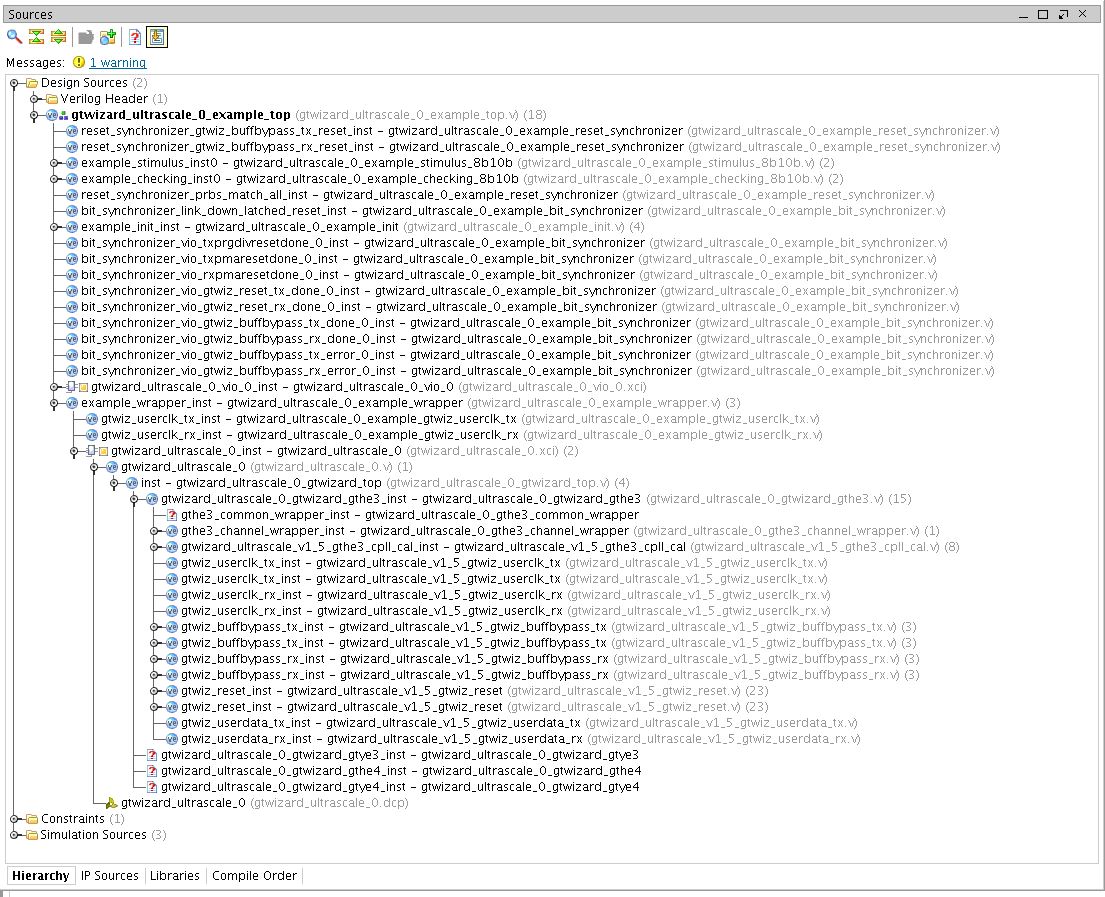

Example Design

directory/file structure

coregen directory - core files (.xco, .v[hd], _readme.txt, _flist.txt)

core directory

doc - documentation

example_design - example design files

implement - implementation scripts

simulation - testbenches

functional - simulation scripts for example design

netlist - simulation scripts for implemented design

You can open an example design in the Vivado tool by right-clicking on designName.v and selecting Open IP example design.

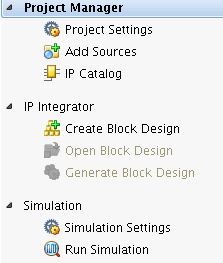

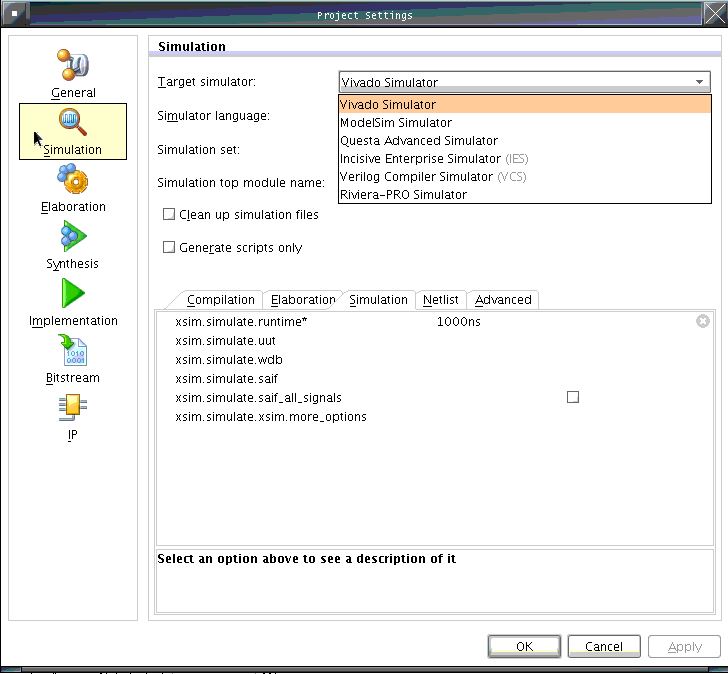

Simulation start / simulators

Go into the functional directory and either run the simulation script simulate_[simulator].[sh|bat] (ISIM,XSIM,NC,VCS), or start the simulator and start the run script simulate_mti.do there (ModelSim)

From the Vivado tool, in the left side of the Project Manager panel, select simulation settings.

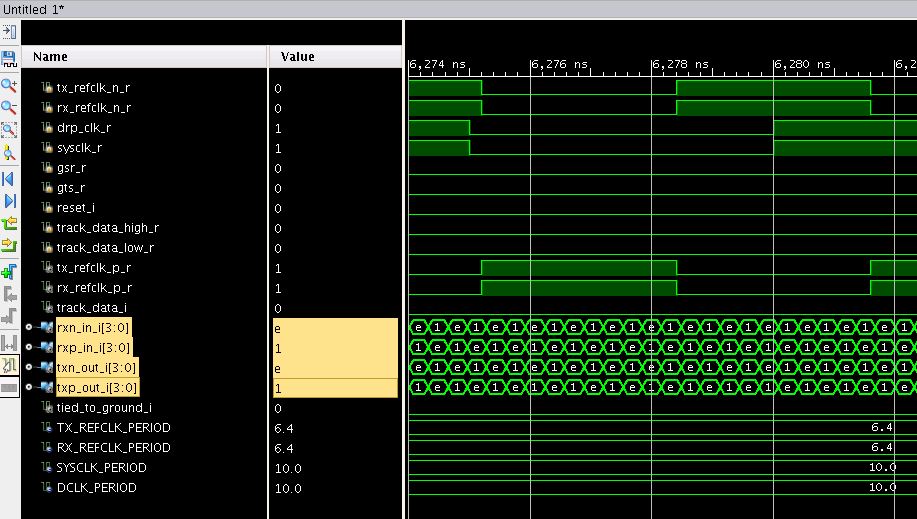

- testbench structure for Kintex GTX as an example:

_tb

global reset

clock settings/generation

_exdes

reset for supporting modules

_gt_usrclk_source - usrclk generation

_gt_frame_gen - frame generator to provide data stream for TX - gt_rom_init_tx.dat used

_gt_frame check - check of RX data against send data stream - gt_rom_init_rx.dat used

ICON/VIO/ILA for Chipscope

_init - GT wrapper and initialisation

core - GT wrapper

RX startup FSM

TX startup FSM

recclk_monitor

RX/TX phase alignment

Add or delete waves to tailor the simulation to the signals of interest.

Digital Simulations Use Cases

Digital simulations of GT's are excellent for making sure you have the right connections and that the basic installation is correct.

A successful simulation shows that the clock frequencies and connections are correct and that the use case is viable.

Digital simulations however, will not show that the equalization, termination and physical layout of the channel is workable.

These issues could be addressed with electrical simulations.