AR# 53368

|PlanAhead and Vivado - Constraining a differential pair with PULLUP and PULLDOWN ignores one of the constraints

描述

I have a design in the PlanAhead or Vivado pin-planning tool and assign PULLUP and PULLDOWN constraints to the P and N pins of the differential signals respectively in UCF or XDC files, as shown in the following UCF example:

NET "<p_pin>" IOSTANDARD = LVDS_25;

NET "<p_pin>" PULLUP;

NET "<n_pin>" IOSTANDARD = LVDS_25;

NET "<n_pin>" PULLDOWN;

After implementing the design, a new UCF file is created in the PlanAhead implementation runs folder "<project_name>/<project_name>.runs/impl_1". The new UCF files change the PULLDOWN constraint to PULLUP for the <n_pin>.

In general, both of the differential pins are assigned only a single constraint (either PULLUP or PULLDOWN) based on which constraint is given last in the UCF.

Why does this happen and how can I work around this problem?

解决方案

For all Xilinx families prior to UltraScale, all the PlanAhead and Vivado tools will take only the last value for all the properties of differential pairs.

When you try to give different attributes to the P and N parts of a differential pairs (in this case, PULLUP and PULLDOWN), the tool automatically converts the property to the one which is given last in the UCF or XDC file, or assigned in a TCL script.

In the example mentioned, the PULLTYPE attribute for both the P and N pairs is converted to PULLDOWN as this constraint is give the latest in the UCF

Writing PULLUP and PULLDOWN attributes through coding into the RTL does not fix this problem.

If the desire is to have opposite pull-types, the solution is to instantiate the PULLUP and PULLDOWN primitives in the design RTL, instead of using the PULLUP and PULLDOWN attributes.

See the <Xilinx Device Family> Libraries Guide for HDL Designs for more information about instantiating the PULLUP/PULLDOWN primitives.

During implementation, the tools should not change the primitives, and you will enable the PULLUP and PULLDOWN in the IO as you intend.

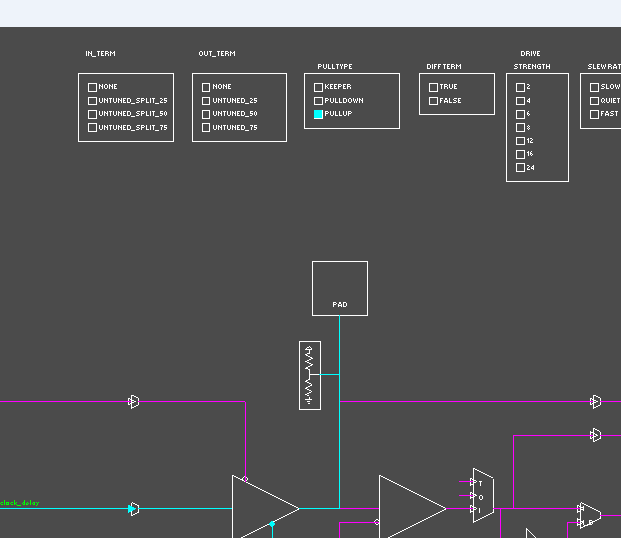

An alternative solution for the ISE/PlanAhead tool flow, is to modify the properties of the P or N pads individually in the FPGA editor after the implementation runs:

- Search for the P and N differential signals in FPGA editor.

- Double-click on the pads to open the properties of the PAD.

- Change the PULLTYPE property on the P and N pads based on your requirements as shown in the figure below.

This will modify the NCD file, hence a valid bit stream can be generated. However, you will have to reassign the properties in FPGA editor each time you re-implement the design.

Starting with the UltraScale family in the 2014.1 Vivado software release, the tool will automatically infer opposite pull-types (pull-up or pull-down) for all differential pin pairs by default, taking the last pull-type assigned to one of the pins, and assign the opposite pull-type to the opposite pin.