AR# 51635

|Xilinx MIG 7 Series Solution Center - Design Assistant - Synthesis and Implementation usage and debug

描述

This section of the MIG 7 Series Design Assistant focuses on Synthesis and Implementation of the MIG 7 Series designs. Please select from the below options to find information related to your specific question.Note: This Answer Record is a part of the Xilinx MIG Solution Center (Xilinx Answer 34243). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

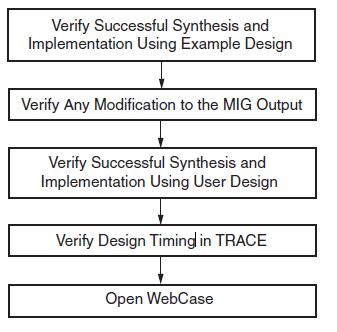

The general flow for debugging synthesis and implementation errors is:

mig_imp_debug_flow.JPG

Verify Successful Synthesis and Implementation

ISE - There are multiple supported flows for generating and implementing the MIG 7 Series cores within ISE Design Suite.

- Generate the core through CORE Generator stand alone. The example design generated by the MIG 7 Series tool includes synthesis/implementation script files. Both the example design and user design include user constraint files (.ucf). These files should be used to properly synthesize and implement the targeted design and generate a working bitstream. The synthesis/implementation script file, called ise_flow.bat, is located inthe example_design/par directory. Execution of this script runs the example designthrough synthesis, translate, MAP, PAR, TRACE, and BITGEN. The options set for each of these processes are the only ones that have been tested with theMIG 7 Series designs. A successfully implemented design completes all processes with no errors (including zero timing errors).

- Generate the core through CORE Generator stand alone. The example _design/par directorygeneratedwith the MIG 7 Series core includes a create_ise script file. Upon executing the script file, an ISE project file(*.ise) is created. This ISE project has all MIG rtl,UCF constraints, and process options (i.e., MAP options) set appropriately.

- Within an ISE project, select to create a New Source. Customize the MIG 7 Series IP and use the instantiation template to pull the core into the target design.

Vivado - See (Xilinx Answer 47273)

Verify Modifications to the MIG Output

The MIG 7 Series tool allows the user to either select the FPGA banks and byte groupsfor the memory interface signals (New Design flow) or select each desired pin location by either manually selecting the pins or uploading a UCF (Fixed Design or Verify UCF and Update Design flows). Based on the selections, the MIG tool outputs a UCF with all required location constraints and corresponding rtl parameters. The UCFfile is located in both the example_design/par and user_design/constraints directories and should not be modified. The MIG tool outputs open source RTL code parameterized by top-level HDL parameters. These parameters are set by the MIG tool and should not be modified manually. If changes are required, such as increasing or decreasing the frequency orchanging the pin locations, the MIG tool should be rerun to create an updated design. Manual modifications are not supported and should be verified independently in behavioral simulation, synthesis, and implementation. Manually modifying the MIGUCF orRTL parameters is the main reason implementation errors are seen. Strict adherence to this step is strongly recommended.

The MIG 7 Series tool allows the user to either select the FPGA banks and byte groupsfor the memory interface signals (New Design flow) or select each desired pin location by either manually selecting the pins or uploading a UCF (Fixed Design or Verify UCF and Update Design flows). Based on the selections, the MIG tool outputs a UCF with all required location constraints and corresponding rtl parameters. The UCFfile is located in both the example_design/par and user_design/constraints directories and should not be modified. The MIG tool outputs open source RTL code parameterized by top-level HDL parameters. These parameters are set by the MIG tool and should not be modified manually. If changes are required, such as increasing or decreasing the frequency orchanging the pin locations, the MIG tool should be rerun to create an updated design. Manual modifications are not supported and should be verified independently in behavioral simulation, synthesis, and implementation. Manually modifying the MIGUCF orRTL parameters is the main reason implementation errors are seen. Strict adherence to this step is strongly recommended.

Error Analysis

- When errors are seen during synthesis, verify any modifications to the output RTL or the core's instantiation into the user design.

- When errors are seen during NGDBuild, verify any modifications to the output constraints in the UCF and top-level RTL parameters. All of the constraints/parameters provided with the MIG 7 Series core are required. The only changes should be to include the paths from the user design into the MIG constraints.

- When errors are seen during MAP/PAR, most often pin-outs, general MIG constraints, clocking, or RTL parameters that define placement have been modified. To verify any changes, please see:

- (Xilinx Answer 51317) Pin-Out and Banking Requirements

- (Xilinx Answer 40603) Clocking Guidelines

Verify Successful Synthesis and Implementation using User Design

Once the MIG 7 Series Example Design and any modificationsare running through the tools properly, the User Design should be inserted into the target design. The core_name.v module located in the generated user_design/rtl directory is the top level of the actual MIG 7 Seriescore and should be used to include thecore in the target design. All files within the example_design directory are specific to the example design/traffic generator only. The constraints within the user_design/constraints/*.ucf file should be merged with the target design constraints file.

Once the MIG 7 Series Example Design and any modificationsare running through the tools properly, the User Design should be inserted into the target design. The core_name.v module located in the generated user_design/rtl directory is the top level of the actual MIG 7 Seriescore and should be used to include thecore in the target design. All files within the example_design directory are specific to the example design/traffic generator only. The constraints within the user_design/constraints/*.ucf file should be merged with the target design constraints file.

Identifying and Analyzing Timing Failures

The MIG 7 Series designs have been verified to meet timingacross a wide range of configurations. However, timing violations might occur, for example, when integrating the MIG design with the target design. Any timing violations that are encountered must be isolated. The timing report output by TRACE (.twx/.twr) should be analyzed to determine if the failing paths exist in the MIG 7 Seriesdesign or the UI (backend application) to the MIG 7 Series design. If failures are encountered, the user must ensure that the build options (that is, XST, MAP, PAR) specified in the ise_flow.bat file are used. If failures still exist, Xilinx has many resources available to aid in closing timing. The PlanAhead toolcan be used to improve performance and quality of the entire design. The Xilinx Timing Constraints User Guide provides valuable information on all available Xilinx constraints.

The MIG 7 Series designs have been verified to meet timingacross a wide range of configurations. However, timing violations might occur, for example, when integrating the MIG design with the target design. Any timing violations that are encountered must be isolated. The timing report output by TRACE (.twx/.twr) should be analyzed to determine if the failing paths exist in the MIG 7 Seriesdesign or the UI (backend application) to the MIG 7 Series design. If failures are encountered, the user must ensure that the build options (that is, XST, MAP, PAR) specified in the ise_flow.bat file are used. If failures still exist, Xilinx has many resources available to aid in closing timing. The PlanAhead toolcan be used to improve performance and quality of the entire design. The Xilinx Timing Constraints User Guide provides valuable information on all available Xilinx constraints.

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 51313 | Xilinx MIG 7 Series Solution Center - Design Assistant | N/A | N/A |

子答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 51317 | MIG 7 Series DDR2/DDR3 - Verify pin-out/banking requirements are met | N/A | N/A |

| 40603 | MIG 7 Series FPGAs DDR3/DDR2 - Clocking Guidelines | N/A | N/A |

| 47273 | MIG 7 Series - How to Generate and Implement the Example Design in Vivado 2012.1-2012.2 Tools | N/A | N/A |

| AR# 51635 | |

|---|---|

| 日期 | 09/05/2012 |

| 状态 | Active |

| Type | 解决方案中心 |

| 器件 | |

| IP | |

People Also Viewed