AR# 51178

|Xilinx MIG 7 Series Design Assistant - Simulating a MIG DDR3 example design using VCS

描述

MIG 7 Series does not support VCS simulations and only supports ISE Simulation, Vivado Simulator, and ModelSim prior to MIG v2.0 Rev1.

This answer record was created to help users who need to simulate using VCS and includes the steps and a simulation script to do so. For MIG v2.0 Rev1 users, see (Xilinx Answer 58057).

MIG VCS simulations are not supported and have not been fully tested by Xilinx, but this script has been validated using the following versions of software and IP:

OS: RHEL 5.6

ISE: 14.2

VCS: F-2011.12

MIG: MIG 7 Series v1.6 DDR3

Note: This article is part of the Xilinx MIG Solution Center (Xilinx Answer 51313). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you to the right information.

解决方案

Steps for simulating a MIG 7 Series example design in VCS F-2011.12 using the script provided:

1. Create a CORE Generator project or Vivado project. Select Verilog as the preferred design language.

2. Select, configure, and generate a MIG 7 Series DDR3 design. The scripts included with this answer record expect the core name to be mig_7series_v1_6_vcs.

Note: If the core name is changed, then files_rev.f contained in attached rev_vcs.zip, line 5, must be updated with the matching IP name.

3. Open a new terminal and source the Xilinx environment (settings32.sh or settings64.sh).

4. In the terminal, browse to the MIG simulation directory (ex. cd /<your_design_name>/example_design/sim/).

5. Download the attachment vcs_rev.zip and unzip the contents to the "sim" directory.

6. In the terminal, type vcs_run.sh. A VCS GUI should appear as below:

7. In the DVE console, type source session.inter.vpd.tcl as shown above. VCS will run for some time and then another window will open containing the waveforms.

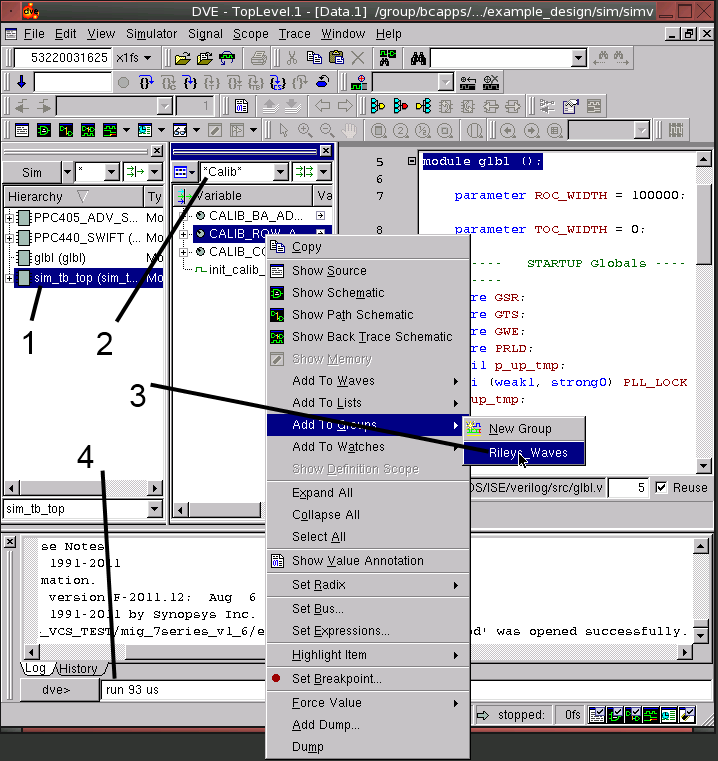

Steps for viewing additional waveforms:

1. Select the level of hierarchy containing the desired signals.

2. Type in the name of the signal. Wildcards (*) are supported.

3. Right-click the signal and add it to existing group, or create a New Group and add it there.

4. Restart the simulation by typing restart in the DVE console and type run X ns, where is X is the length of time you wish to run the simulation.

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| vcs_rev.zip | 6 KB | ZIP |

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 51671 | Xilinx MIG 7系列解决方案中心设计助手:仿真器支持 | N/A | N/A |

子答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 58057 | MIG 7 Series - IES and VCS Simulator Support | N/A | N/A |

| AR# 51178 | |

|---|---|

| 日期 | 10/25/2013 |

| 状态 | Active |

| Type | 解决方案中心 |

| 器件 | |

| IP | |