AR# 47232

|MIG 7 系列 DDR3L - 满足 JEDEC 标准要求的 RESET# 建议

描述

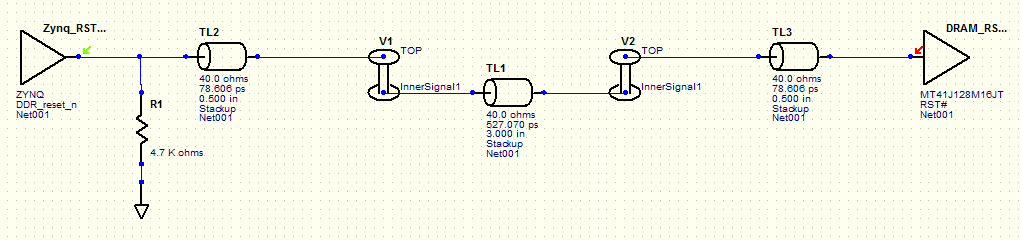

本答复记录包括特定的 RESET# 指南,应遵循此指南确保使用 DDR3L MIG 7 系列 FPGA 设计时能够充分满足 JEDEC 要求 (VIL/VIH = 20%/80%/VCCO)。

注:本答复记录是 Xilinx MIG 解决方案中心(Xilinx 答复 34243)的一部分。

Xilinx MIG 解决方案中心可解决所有与 MIG 相关的问题。

无论您是要使用 MIG 来进行新设计还是要解决问题,请使用 MIG 解决方案中心来指导您获取相应的信息。

解决方案

本指南包括:

- RESET# 引脚使用 SSTL135。

- SSTL135 到 RESET# 的信号不得端接于 Vtt (0.65V)。

- SSTL135 到 RESET# 的信号不得使用大于 4.7K 欧姆的外部下拉电阻值。

本信息将被添加到 7 系列 MIG 用户指南 (UG586)。

SSTL135 的 VOH MIN (VOH min = 0.825V) 未达到 RESET# 的 VIH MIN 要求 (VIH MIN = 1.08V)。

建议执行前后布局仿真来确保符合 DRAM RESET# VIH MIN 要求。

本指南适用于 MIG 和 PS 内存控制器。

以下设置用于仿真 SSTL135、SSTL15 和 LVCMOS15。

适当的 VIH MIN 可使用带所有工艺角的所有驱动程序来满足。

运行 LVCMOS15 是为了实现完整性,推荐使用 SSTL135 和 SSTL15 来驱动 RESET# 信号。

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 34370 | MIG DDR3 - JEDEC 规范;DDR3 SDRAM 复位引脚 | N/A | N/A |

| AR# 47232 | |

|---|---|

| 日期 | 08/13/2018 |

| 状态 | Active |

| Type | 解决方案中心 |

| IP | |

People Also Viewed