AR# 44012

|7 Series Integrated Wrapper for LogiCORE CPRI - TXOUTCLK and RXOUTCLK Port Restrictions

描述

There are some restrictions in using the TXOUTCLK and RXOUTCLK ports for the Initial Engineering Sample (ES) silicon.As a result, you need to update your instantiations to account for these restrictions.For more information, please see (Xilinx Answer 43244).解决方案

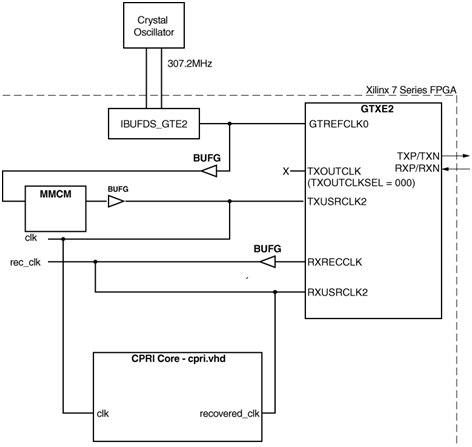

This article describes the restrictions on the TXOUTCLK and RXOUTCLK ports of the transceiver. To cope with these restrictions, the MMCM transmitter input now comes from the reference clock, IBUFDS_GTE2. And, the transceiver TXOUTCLK port is disabled. The receiver side clocking remains unchanged. You must also set the TXOUTCLKSEL input to the GTXE2_CHANNEL instance to "000".

- Change the input to the k7_bufg_gen BUFG component in the <component_name>/example_design/gtx_and_clocks/gt_and_clocks.vhd file: k7_bufg_gen : BUFG port map (I => refclk, O => txoutclk_bufg);

- Route the BUFG output to the refclk input of the tx_clk_gen instance.

- Leave the GT0_TXOUTCLK_OUT port of the GTWIZARD instance open:

GT0_TXOUTCLK_OUT => open,

Figure 1 shows the revised clocking scheme.

<

For the LogiCORE CPRI Release Notes and Known Issues, see (Xilinx Answer 36969).

本答复记录是否对您有帮助?

链接问答记录

主要问答记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 36969 | LogiCORE IP CPRI - Release Notes and Known Issues | N/A | N/A |

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 44215 | 7 Series Integrated Wrapper for LogiCORE CPRI - v4.1- Should the transceiver transmit and receive elastic buffers be enabled? | N/A | N/A |

| 44011 | 7 Series Integrated Wrapper for LogiCORE CPRI - IBUFDS_GTE2 Use Model Change | N/A | N/A |

| 43339 | 7 Series FPGA GTX Transceiver - Software Use Model Changes | N/A | N/A |

| 43244 | 面向 Kintex-7 和 Virtex-7 FPGA GTX 收发器的设计咨询 - 用于初始工程样片 (ES) 芯片的属性更新、问题和解决方案 | N/A | N/A |

| AR# 44012 | |

|---|---|

| 日期 | 05/22/2012 |

| 状态 | Archive |

| Type | 已知问题 |

| IP | |

People Also Viewed