AR# 43667

|MIG Spartan-6 MCB - DQS Centering

描述

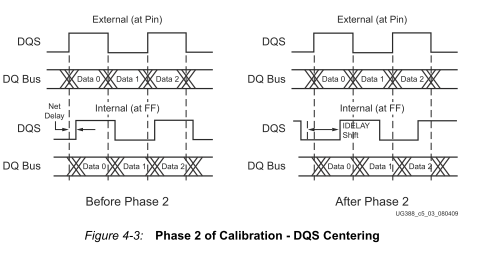

For optimal performance and maximum timing margin, the DQS strobe edges must be centered in the Read Data capture window with respect to the input capture flip-flop. Phase 2 of calibration is responsible for this DQS centering operation.

Note:This Answer Record is a part of the Xilinx MIG Solution Center (Xilinx Answer 34243). The Xilinx MIG Solution Center is available to address all questions related to MIG. Whether you are starting a new design with MIG or troubleshooting a problem, use the MIG Solution Center to guide you tothe right information.

解决方案

The DDR memory device output pins transmit the Read Data (DQ) and DQS strobes edge-aligned to the FPGA input pins as shown in Figure 4-3. For reliable operation, the DQS strobe must be delayed with respect to the DQ bits so that it captures the Read Data away from the transition region of the data bus.

During this phase, the tap delay count of the IDELAY block in the DQS strobe input path is incremented to shift the internal DQS signal at the capture flip-flop into the center of what will become the Read Data capture window as shown in Figure 4-3.

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 43662 | MIG Spartan-6 MCB - Soft Calibration | N/A | N/A |

| AR# 43667 | |

|---|---|

| 日期 | 12/15/2012 |

| 状态 | Active |

| Type | 综合文章 |

| 器件 | |

| IP | |