AR# 36291

|MIG, MPMC, Spartan-6 MCB - 在初始配置时出现存储器故障

描述

当使用 Spartan-6 FPGA 中的 MIG 或 MPMC 存储器控制器时,配置完成后会出现存储器故障(数据错误),或者功耗高于预期。随后对系统进行复位(无需重新配置)会正常工作,并(或)减少器件的功耗。

这个情况会在 Spartan-6 SP601 开发板或基于 SP601 的客户开发板上出现。

只有系统内具备以下所有条件时才会出现这种情况:

- 所提供的校正输入端接选项被启用。

该选项通过 MIG GUI 来设置,而且只针对 DDR、DDR2 和 DDR3 存储器接口提供。

- 在配置之前,通过将 HSWAPEN 接地可在所有 I/O 引脚上提供内部上拉电阻。

- 利用电阻分压器网络产生 Vref 电压轨。

- 在 Vref 电压轨上放置一个(或几个)解耦电容。

因此,LPDDR 不会出现这种情况。

所有其它 MCB 存储器标准都会基于以上具体条件出现这种情况。

解决方案

概览导致该问题的原因是在器件完成配置之前电路板上的 Vref 电压轨拉高至预期 Vcco/2 的 Vref 级别以上,在配置完成后这个更高的电压值仍出现在 Vref 电压轨上。

当 HSWAPEN 引脚接地时会出现这种情况,因为这样会打开所有 I/O 引脚中的内部上拉电阻 - 包括多功能 Vref 引脚。

如果 Vref 电源来自 Vcco 与接地之间简单的电阻分压器,而非来自具有电流吸入能力的稳压器,那么每个 Vref 引脚中的内部上拉电阻将增加另外一个并联的上拉电阻,从而把 Vref 电压轨拉高至接近 Vcco 的级别。

在 Spartan-6 配置完成后,所有 I/O 引脚(包括 Vref 引脚)内的 HSWAPEN 上拉电阻都被关闭,但是 Vref 电压轨上的所有电容都会起到延续这一更高电压的作用,直到有机会放电为止。

放电时间的长短取决于电阻分压器和电压轨电容确定的 RC 时间常数 - 电容主要是所用的解耦电容。

当 Spartan-6 设计开始操作 MCB 控制器时出现这种高的 Vref 电压,这会导致校准输入端接电路无法正确工作。

最终结果导致在所有的 DQ 和 DQS 引脚上使用错误的输入端接值。

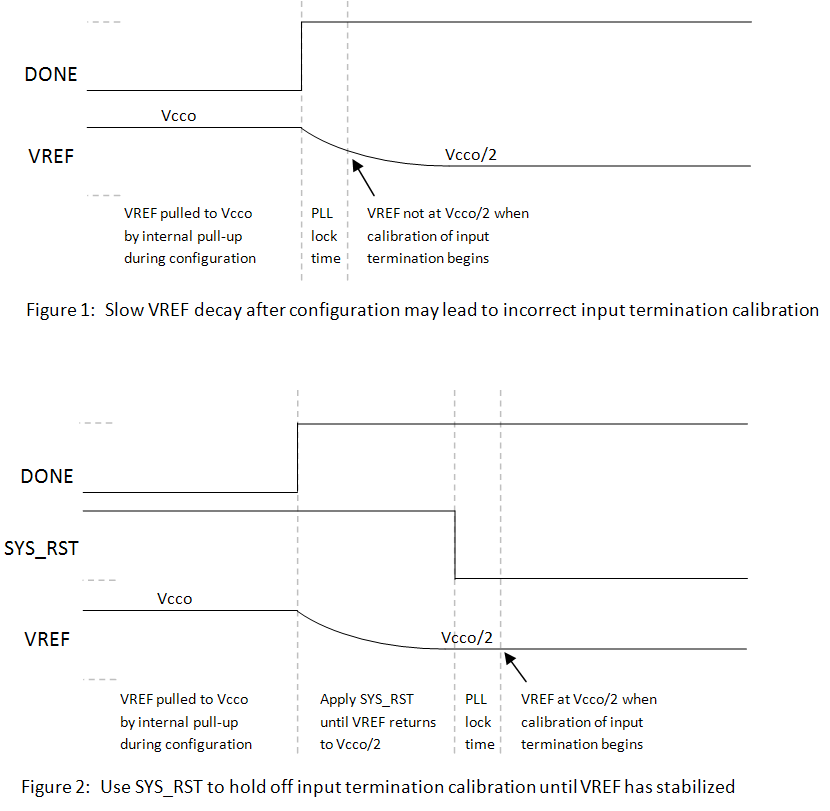

下图给出了配置完成后(断言DONE)Vref 的衰减情况,以及保持 sys_rst 的推荐解决办法(图下注释):

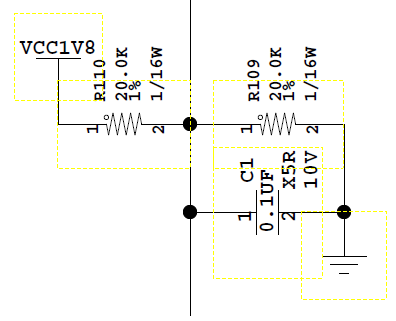

以下是 SP601 开发板上 Vref 电阻分压器的电路图:

配置完成后,当电容器放电时, RZQ/ZIO 引脚上 SSTL I/O 标准使用该 Vref 电压时会导致 MCB 校正产生歪斜。

软逻辑复位后不会出现这种情况,因为 VREF 已经放电并达到稳定。

SP605 不受影响,因为它采用的是稳压器而非电阻网络。

解决办法

在配置完成后保持复位,直到 Vref 达到稳定,这样可以解决该问题。

对于 SP601 开发板上的有些设计而言,如果通过修改代码来保持复位的这种方法并不理想,那么在配置完成后进行手动复位也能获得成功的校正输入端接和 MCB 操作。

本答复记录是否对您有帮助?

链接问答记录

相关答复记录

| Answer Number | 问答标题 | 问题版本 | 已解决问题的版本 |

|---|---|---|---|

| 43769 | Design Advisory Master Answer Record for Spartan-6 FPGA SP601 Evaluation Kit | N/A | N/A |

| 37498 | MIG Design Assistant - Spartan-6 Core Functionality | N/A | N/A |

| 33566 | Design Advisory Master Answer Record for Programmable Logic Based External Memory Interface Solutions for Virtex-6, Spartan-6, all 7 Series Devices, and all UltraScale based Devices | N/A | N/A |

| 42024 | MIG 7 系列 DDR3 – FPGA 和 DDR3 SDRAM 之间的推荐迹线阻抗是什么? | N/A | N/A |