Zynq UltraScale+ RFSoC ZCU1285 特性描述套件

by: Xilinx, Inc

Zynq® UltraScale+™ RFSoC ZCU1285 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ XCZU39DR RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。

or buy from:

Authorized Distributors

概述

产品描述

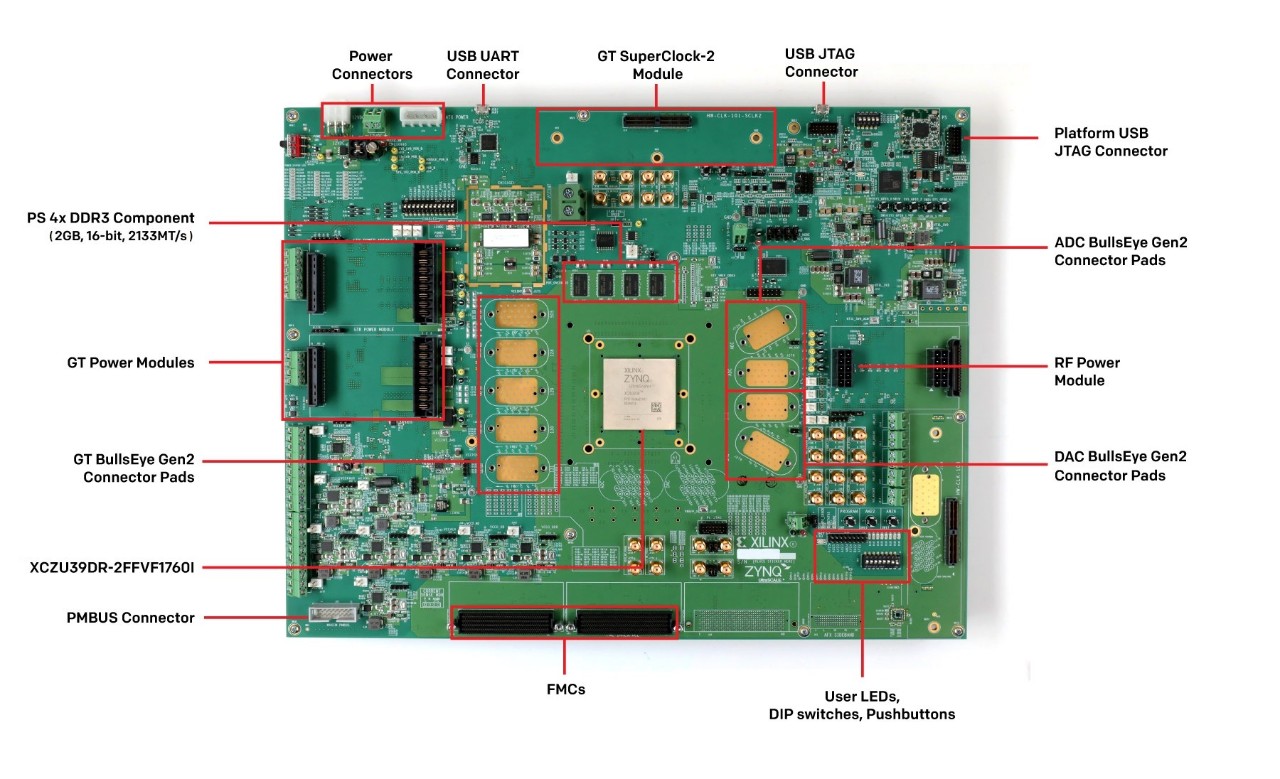

Zynq® UltraScale+™ RFSoC ZCU1285 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ Gen 2 XCZU39DR RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。所有 16 个 12 位 2.220GSPS ADC、所有 16 个 14 位 6.554GSPS DAC、所有 16 个 GTY 收发器以及所有 4 个 GTR 收发器都可通过 Samtec BullsEye 连接器访问。BullsEye 连接器允许您连接至定制换衡器和测试设备,在测试定制应用中实现最高的灵活性。了解更多信息,查看套件所含配件。

主要性能和优势

- 用于对 Zynq UltraScale+ XCZU39DR-2FFVF1760I RFSoC 上集成的 ADC、DAC 和收发器进行特性描述和评估的硬件环境

- 集成 16x16 ADC、DAC 设计实例

- 集成式误码率测试器 (IBERT) 参考设计

- 支持全部 ADC、DAC、GTY 收发器和 GTR 收发器的 BullsEye 连接器

- 所有 ADC/DAC 电轨、所有 GTY/GTR 电轨和 VCCINT/VCCO_HP/VCCO_HD 电轨的 SMA 功率探针通道

- 支持所有 ADC/DAC 时钟要求的模拟 RF SuperClock 模块

- 支持 GTY/GTR 参考时钟要求的 GT SuperClock 模块

- 一个高引脚数 (HPC) FPGA 夹层卡 (FMC) 连接器

- 一个低引脚数 (LPC) FMC 连接器

特色 Xilinx 器件

包含 Zynq UltraScale+ XCZU39DR-2FFVF1760I RFSoC

| 12 位 2.220GSPS RF-ADC | 16 |

|---|---|

| 14 位 6.554GSPS RF-DAC | 16 |

| 系统逻辑单元 (K) | 930 |

| DSP slice |

4,272 |

| 内存 (Mb) | 60.5 |

| 33G 收发器 | 16 |

| 最大 I/O 引脚数 | 408 |

产品信息

开发板特性

包含 Zynq® UltraScale+™ XCZU39DR-2FFVF1760I RFSoC

| 开发板规范 | 值 |

|---|---|

| 长度 | 16 英寸(40.6 厘米) |

| 高度 | 12.6 英寸(30.0 厘米) |

| 厚度 (+/-5%) | 0.13456 英寸(0.3418 厘米) |

| 工作环境温度 | 0◦C to +45◦C |

| 存储环境温度 | -25◦C to +60◦C |

| 存储器 | |

| PS DDR3 原件 | 4x2GB |

| 通信与网络 | |

| 面向 ADC 的 Samtec BullsEye 连接器 | 2 |

| 面向 DAC 的 Samtec BullsEye 连接器 | 2 |

| 面向 GTY 的 Samtec BullsEye 连接器 | 4 |

| 1 | |

| USB UART | 有 |

| 显示 | |

| DIP 开关 | ✓ |

| LED | 有 |

| 按钮 | ✓ |

| 扩展连接器 | |

| FMC-HPC 连接器 | 1 |

| FMC-LPC 连接器 | 1 |

| 时钟 | |

| GT SuperClock-2 模块 | 有 |

| 模拟 SuperClock-RF2 模块 | 有 |

| 控制 & I/O | |

| IIC | 有 |

| PMBUS | 有 |

| 功耗 | |

| 12V 墙上适配器 | ✓ |

| ATX 电源兼容 | ✓ |

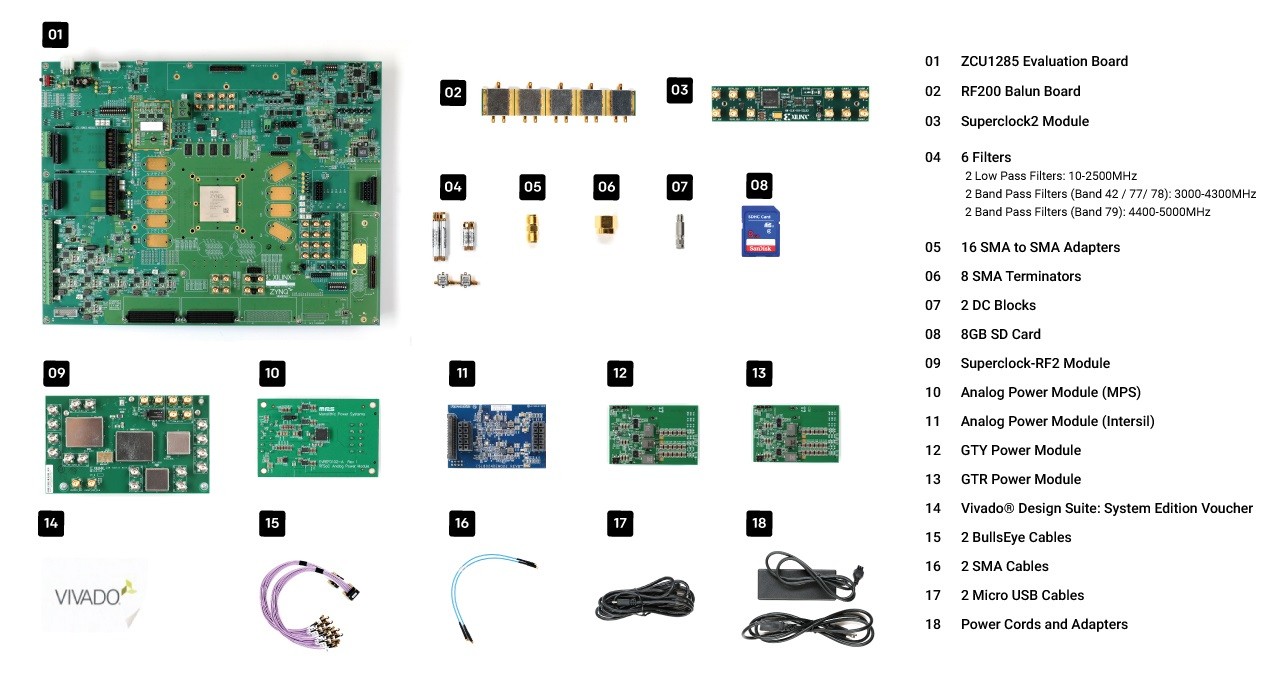

盒内组件

包含 Zynq® UltraScale+™ XCZU39DR-2FFVF1760I RFSoC

资源

设计工具

| 名称 | 说明 | 许可证类型 |

|---|---|---|

| Vivado Design Suite: System Edition | Xilinx Vivado® Design Suite 是一款以 IP 核及系统为中心的设计环境,这一全新构建的环境具有革新意义,能够显著加速全面可编程型器件的设计效率。 | 节点锁定及器件锁定至 Zynq® UltraScale+™ XCZU39DR RFSoC,包含 1 年更新服务 |

| Xilinx SDK | 针对 Xilinx 平台提供全面的嵌入式软件开发及调试工具套件 | 包含 |

| PetaLinux 工具 | 将 Linux 操作系统配置、构建和部署至 Xilinx 平台。 | 包含 |

| 板级支持包 (BSP) | 预配置的引导加载程序、系统映像和比特流 | 包含 |

IP 核

| 名称 | 描述 | 许可证类型 |

|---|---|---|

| 存储接口生成器 (MIG) | 存储器接口发生器 (MIG) 是一款用于为 Xilinx 器件生成存储器控制器和接口的免费软件工具。 | 包含 |