联想、中国移动、赛灵思、Napatech、锐德世联合推出业界首个硬件加速、软硬解耦的 5G 接入网云化方案

Jul 02, 2018

2018年7月3日,中国北京 —— 在6月27日开幕的世界移动大会MWC上海展会上,联想集团、中国移动、赛灵思(Xilinx)、Napatech、锐德世(Radisys)五家公司联合推出了业界首个支持多形态加速硬件、软硬件充分解耦的移动接入网云化方案 。

联想集团副总裁、联想研究院企业服务云计算实验室和5G实验室负责人黄莹博士表示:“无线网基站云化与虚拟化是5G时代的重要技术方向,对运营商优化网络效率、促进业务创新、提升用户体验等方面,均具有深远意义。联想致力打造基于NFV技术的端到端产品与服务,在硬件加速与整体软、硬件解决方案等方面持续创新,助力运营商网络云化、虚拟化与智能化的转型。”

今年二月,中国移动联合全球多家运营商,在C-RAN理念的基础上进一步发起了开放智能无线网络(O-RAN)联盟,首次提出“智能管控、开放接口、开源白盒”无线接入网的核心理念,将进一步推进无线网基站的云化和虚拟化,最终实现软硬件解耦的开放设备。NFV虚拟化平台需要通过引入加速硬件设备进一步提升性能、优化能效、节省成本,这已在业界形成了共识。而目前加速器方案存在功能专一、接口不统一等问题,造成软硬件无法解耦。在这一背景下,中国移动从运营商实际需求出发,提出引入硬件可编程、且接口统一封装的硬件加速解决思路。与联想集团联合行业伙伴积极探索这一理念下的NFVI解决方案,取得了阶段性成果。

中国移动研究院首席科学家易芝玲博士表示:“中国移动致力于推进统一的硬件加速器封装接口方案的研究,感谢联想公司及合作伙伴的支持。这一方案是在保证软硬件解耦的基础上,利用可编程通用硬件加速器提升NFV平台的整体能效,降低综合成本。无线云平台是支撑O-RAN整体方案的基础,欢迎业界更多的合作伙伴加入到我们的研究中来,为实现开放、智能的无线接入网而努力。”

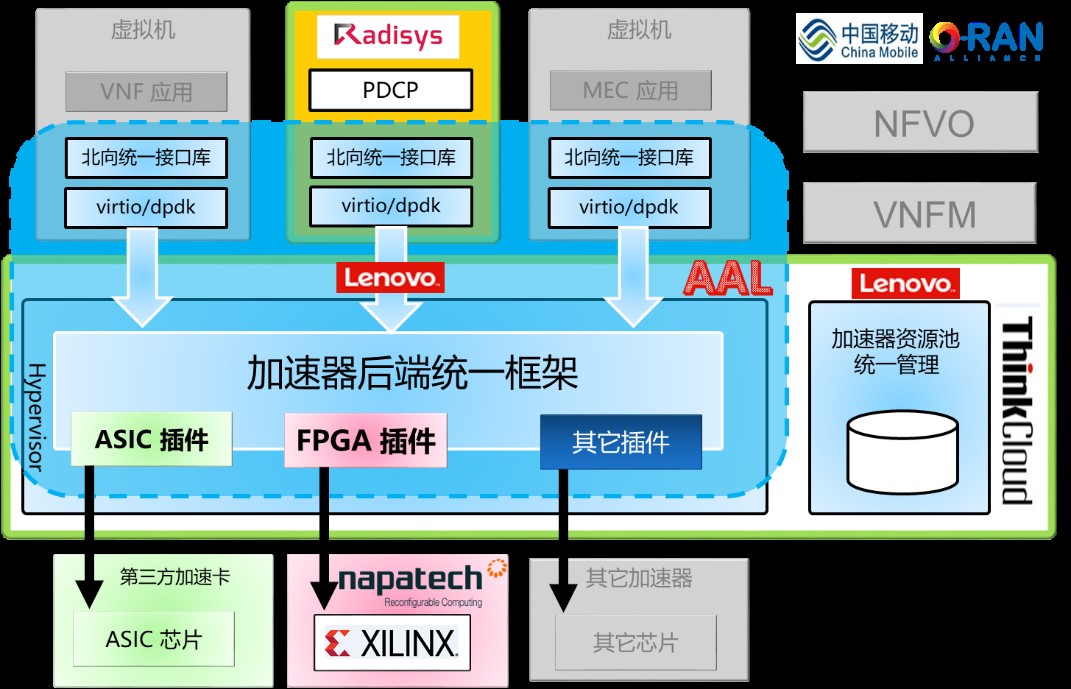

本次联合展示采用联想ThinkCloud Accelerator云加速器方案,包括联想ThinkCloud NFVI电信级云平台软件,以及x86服务器与交换机硬件;其中ThinkCloud NFVI可自动适配不同厂商、不同形态的加速硬件设备,并通过对加速硬件的抽象与虚拟化,向网元应用提供一套统一的API接口,降低应用开发与移植复杂度,促进应用软件与加速硬件的充分解耦。

联合展示中的加速硬件设备包括基于赛灵思FPGA可编程芯片的Napatech智能网卡和基于ASIC专有芯片的第三方板卡。赛灵思FPGA可编程芯片提供了灵活的硬件逻辑编程和可重配置能力与强大的计算性能和能效,可以适用从边缘到核心的众多NFV应用场景。基于赛灵思FPGA芯片,Napatech智能网卡方案实现了对Open vSwitch (OVS)虚拟交换机与无线基站PDCP加解密等转发与计算密集型运算的加速,大幅降低CPU负载,提升性能,节约成本。

赛灵思通信市场部副总裁Farhad Shafai表示:“为了满足迅速演进的5G C-RAN对敏捷性,可扩展性及灵活性的需求, 在Napatech 智能网卡上利用赛灵思自适应平台展示了标准开放API加速。该智能网卡解决方案通过硬件抽象层API为运营商提供了易管理、易部署的解决方案, 并可利用灵活经济的方式满足性能需求。利用运行在联想服务器与云平台软件上的锐德世Radisys PDCP协议栈部署基于C-RAN加速平台的加速器抽象层API,展示了电信云中基于FPGA的加速所带来的灵活、保证时延及性能收益等优势!”

Napatech首席市场官Jarrod J.S. Siket表示:“目前NFV用于虚拟化RAN的部署模式是使用x86服务器,但实际上碰到了主要的性能瓶颈。 若是将复杂的网络与安全任务卸载到基于FPGA的SmartNIC,运营商可以使用通用服务器的架构维持NFV模式来进行VNF处理,而不会影响LTE和5G应用所需的性能、延迟成本和功耗目标。”

面向O-RAN无线网基站的云化和虚拟化,锐德世Radisys提供高性能、高扩展性的4G与5G协议栈。此次合作中锐德世Radisys提供了PDCP协议栈虚拟化网元,该网元支持在单一虚拟机中运行,并可灵活扩容多虚拟机,满足不同负载情况下处理能力的弹性伸缩。

锐德世Radisys副总裁、软件及服务解决方案总经理Neeraj Patel表示:“锐德世Radisys非常高兴能与各方合作伙伴持续协作,共同推动本次面向真实场景部署的5G vRAN重要展示。在本次联合展示中,我们的高性能PDCP软件协议组,包括UE模拟器和网络打流器,与我们生态合作伙伴的软、硬件平台相集成,推动了本次中国移动RAN加速展示的成功。”

在本次大会上,五家合作公司现场展示了PDCP虚拟化网元与NFVI软、硬件平台的充分解耦——同样一套PDCP网元应用,无需修改,即可自动适配基于FPGA和ASIC不同形态的加速设备,实现对ZUC编解码算法的硬件加速;当系统中不具备加速硬件时,网元应用也可自动采用基于CPU的纯软件实现。在性能方面,与CPU纯软实现相比,采用赛灵思FPGA的Napatech智能网卡方案可提升ZUC编码吞吐量10倍、PDCP整体吞吐量3倍,并且实现时延的20倍降低。

展望下一阶段工作,五家合作公司计划将进一步优化方案、提升性能;同时也期望业界有更多合作伙伴加入联合研发,促进开源社区接纳可编程通用加速器的方案,以及统一的封装接口方案,最终促进NFVI高能效解决方案的成熟,加速NFV在无线侧的应用产业落地。

关于赛灵思

赛灵思致力于通过开发高度灵活和自适应的处理平台,为从端点到边缘再到云端的多种不同技术的快速创新提供支持。赛灵思是 FPGA、硬件可编程 SoC 及 ACAP 的发明者,旨在提供业界最具活力的处理器技术,实现自适应、智能且互连的未来世界。如需了解更多信息,敬请访问赛灵思中文网站://m.akhomesold.com/。

追随赛灵思:

赛灵思-优酷:http://i.youku.com/xilinx

赛灵思新浪微博:http://weibo.com/xilinxchina

赛灵思中文用户社区论坛:http://forums.xilinx.com/cn

赛灵思公司

张俊伟

电话:(86-10) 5651 7406