Alveo™ U45N 网络加速器

- 状态: Available

- 产品编号: A-U45N-P08G-PQ-G

Alveo™ U45N 网络加速器是一款基于 FPGA 的平台,可为数据中心的基础架构工作负载提供低时延、2x100G 的线路速率性能,因此可将宝贵的服务器 CPU 周期从基础架构任务中解放出来,运行业务极为重要的应用。超大规模企业、云服务提供商和电信运营商可通过定制虚拟交换(例如 OVS)、安全工作负载(例如 IPsec)和存储协议来满足其自己的基础架构需求。与 Vivado™ 工具流程以及全面的 OpenNIC 参考设计相结合,Alveo U45N 卡可为 FPGA 开发人员提供硬件平台、工具和 IP,帮助他们构建自己的网络加速解决方案并为其实现差异化。

主要特性与优势

2x100G 线路速率的硬件加速

- 2x100G 以太网线路速率性能,可随网络流量扩展

- 确定性低时延,可实现可靠的性能和 QoS

- 为数据中心工作负载提供冗余

可适应不断发展的自定义工作负载

- 100 万个可完全定制的 FPGA 架构 LUT

- 加速自定义的网络、安全及存储工作负载

- 支持可选控制层功能的分立式 Arm® Cortex®-A72 处理器

可用于简化开发的 Vivado™ 工具和参考设计

- 用于 RTL 设计和硬件定制的 Vivado® 设计套件

- 用于构建网络的庞大构建块 IP 目录

- 支持 DPDK 驱动程序的综合 OpenNIC 参考设计

定制网络解决方案的开放式平台

Alveo™ U45N 网络加速器是一款开放式 FPGA 平台,适用于数据中心的加速卸载。开发人员可根据自己的基础架构需求,通过 FPGA 架构上的硬件执行方案,为自定义协议、安全策略和计算存储执行一系列应用和工作负载。以下提供一些实例。

支持自定义数据包处理的 Open vSwitch

开发人员可设计实施 Open vSwitch (OVS),因此允许将帧和数据包处理从主机 CPU 转移至 Alveo U45N 加速卡完成。此外,开发人员还可实施 VXLAN 和 Geneve 等标准覆盖,或者集成他们自己的特性执行包帧封装、监控和管理等。

自定义安全策略的虚拟防火墙

有了 Alveo U45N 平台,设计人员可集成自己的 IP,帮助防止内部服务器、虚拟机、容器及客户端服务免受外部威胁。开发人员可为 IPsec 及其它工作负载加速,实现状态防火墙、无状态防火墙、流程跟踪和连接跟踪等。

存储卸载:NVMe-oF、NVMe/TCP

对于新一代存储系统,Alveo U45N 是开发 NVMe over Fabric (NVMe-oF) 或 over TCP/IP (NVMe/TCP) 应用的理想解决方案。作为一款开放式 FPGA 平台,Alveo U45N 网络加速器可支持自定义数据包报头和自定义拥塞控制,从而可提高整体吞吐量、缩短时延。此外,FPGA 架构还可提供加速各种存储工作负载的灵活性,其中包括数据压缩、加密、去重和虚拟化,并可优化整体存储利用率。

卡规格

参阅产品简介,查看完整的产品概览。

| 开发板规格 | Alveo U45N 网络加速器 |

|---|---|

| FPGA 器件 |

|

| 板载处理器1 |

|

| 性能 |

|

| 网络接口 |

|

| 主机接口 |

|

| 板载内存 |

|

| 尺寸 |

|

| 电源与散热 |

|

| 工具流 |

|

1:Arm 处理器只能使用 AMD OpenNIC 参考设计提供支持

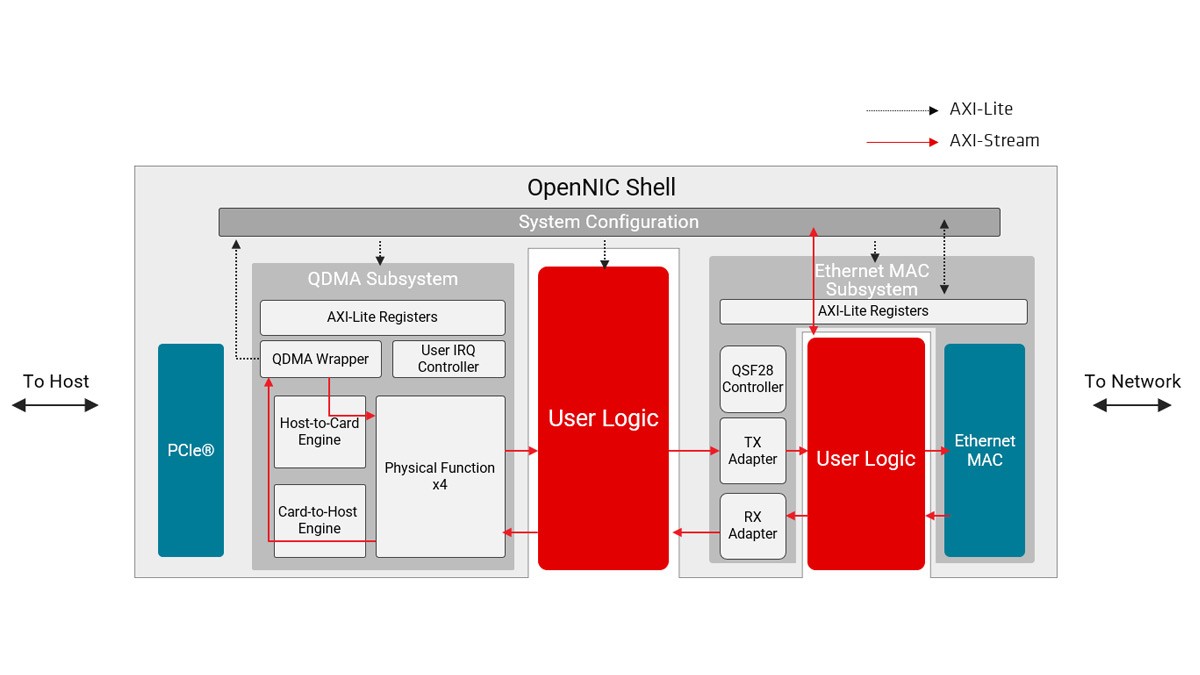

AMD OpenNIC 项目

AMD 提供综合开源 NIC 参考设计 OpenNIC,简化数据中心内联网络应用的 FPGA 开发。OpenNIC 得到了 Alveo 灵活应变的各种加速卡(包括 Alveo U45N 网络加速器)的支持,围绕“shell”和“角色”概念安排组织,其中 shell 可为外部接口提供一系列标准的硬件 IP 块,而角色则允许集成自定义 IP。开源参考设计包括

- 带多种配置选项的以太网及 QDMA IP 子系统

- 支持多达 4 个 PCIe 物理功能 (PF)

- 用户逻辑盒集成自定义 IP

- shell 和角色之间基于 AXI 的通信可实现轻松集成

- DPDK 软件在主机 CPU 上运行

OpenNIC 现在在 GitHub上开源提供。

Alveo U45N 下载

U45N Alveo 数据中心加速卡支持 Vivado 设计输入。对于想要使用传统设计流程(例如 RTL 或 HLx)的 FPGA 设计人员,建议使用 Vivado 流程。使用下面的选项卡开始使用 Vivado 并下载 Xbflash2 实用程序。

在 Vivado 中开发您自己的 Alveo U45N 加速应用

使用 RTL和 HLx 进行开发,请按照下列步骤操作:

Xbflash2 实用程序

您可以使用 Xbflash 实用程序将自定义图像刷新到特定 Alveo 卡。有关更多详情,请参阅用户指南 https://xilinx.github.io/XRT/master/html/xbflash2.html。

| 描述 | 链接 |

|---|---|

| RHEL/CentOS 7.8, 7.9 | xrt_202210.2.13.466_7.8.2003-x86_64-xbflash2.rpm (zip) |

| RHEL 8.1, 8.2, 8.3, 8.4, 8.5 | xrt_202210.2.13.466_8.1.1911-x86_64-xbflash2.rpm (zip) |

| Ubuntu 18.04.4 LTS, 18.04.5 LTS | xrt_202210.2.13.466_18.04-amd64-xbflash2.deb |

| Ubuntu 20.04 LTS, 20.04.1 LTS, 20.04.2 LTS, 20.04.3 LTS | xrt_202210.2.13.466_20.04-amd64-xbflash2.deb |