High Level Design

High Level Design Features

Here's a quick overview of Vivado® ML features for Accelerating High-Level Design. Click the other tabs for complete feature details.

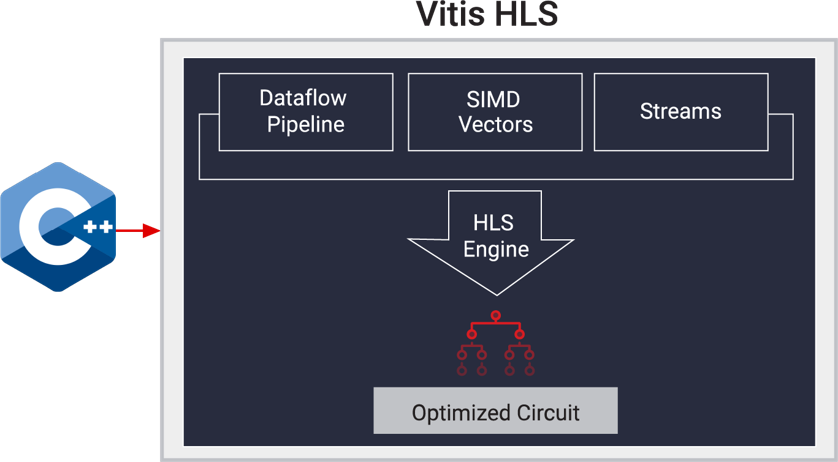

Vitis High-Level Synthesis

Advanced algorithms used today in AI, wireless, medical, defense, and consumer applications are more sophisticated than ever before. Vitis™ High-Level Synthesis included as a no cost upgrade in all Vivado Editions, accelerates IP creation by enabling C++ specifications to be directly targeted into Xilinx programmable devices without the need to manually create equivalent RTL designs. Supporting both the Vitis and Vivado design environments Vitis HLS provides software and hardware designers alike with a faster path to kernel or IP creation through:

- Abstraction of algorithmic description, data type specification with integer, fixed-point or floating-point and interfaces (FIFO, Memories, AXI4)

- Extensive libraries for including built-in support for arbitrary precision data types, streams and vectorized data types

- Directives driven architecture-aware synthesis that delivers the best possible QoR

- Fast time to QoR that rivals hand-coded RTL

- Accelerated verification using C/C++ test bench simulation, automatic VHDL or Verilog simulation and test bench generation

- Automatic use of Xilinx on-chip memories, DSP elements including for floating-point types

Libraries

The following built-in libraries are included with Vitis HLS:

| Name | Description |

|---|---|

Arbitrary Precision Data Types |

Integer and fixed-point (ap_int.h) |

HLS Streams |

Models for streaming data structures. Designed to obtain best performance and area (hls_stream.h) |

Vector types |

Vectorized types and operations (hls_vector.h) including for arbitrary precision types |

HLS Math |

Extensive support for the synthesis of the standard C (math.h) and C++ (cmath.h) math libraries. The support includes floating point and fixed-point functions: abs, atan, atanf, atan2, atan2, ceil, ceilf, copysign, copysignf, cos, cosf, coshf, expf, fabs, fabsf, floorf, fmax, fmin, logf, fpclassify, isfinite, isinf, isnan, isnormal, log, log10, modf, modff, recip, recipf, round, rsqrt, rsqrtf, 1/sqrt, signbit, sin, sincos, sincosf, sinf, sinhf, sqrt, tan, tanf, trunc |

The Vitis high-level synthesis tool also supports the Vitis performance-optimized libraries available on Github with out-of-the-box acceleration with minimal to zero-code changes to your existing applications. These common Vitis accelerated-libraries include advanced Math, Statistics, Linear Algebra, and DSP to offer core functionalities for a wide range of applications. These libraries offer acceleration for workloads like Vision and Image Processing with OpenCV, Quantitative Finance, Database, and Data Analytics, Data Compression and more...

IP Integrator

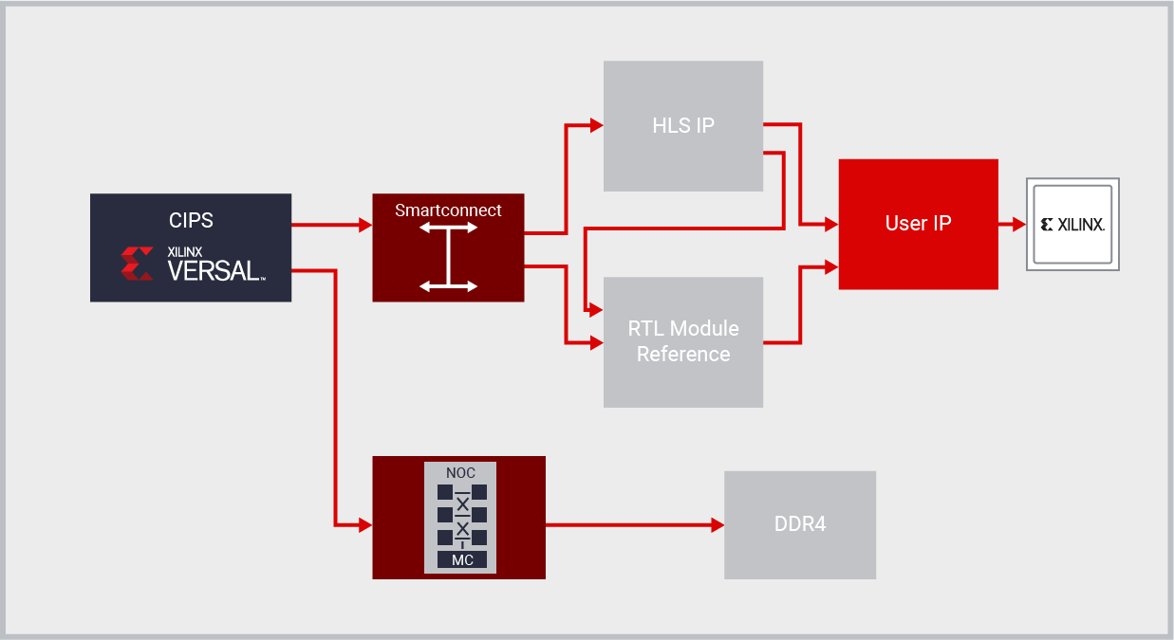

The Vivado® ML Edition shatters the RTL design productivity plateau by providing the industry’s first plug-and-play IP integration design environment, with its IP Integrator feature.

Vivado IP Integrator provides a graphical and Tcl-based, correct-by-construction design development flow. It provides a device and platform aware, interactive environment that supports intelligent auto-connection of key IP interfaces, one-click IP subsystem generation, real-time DRCs, and interface change propagation, combined with a powerful debug capability.

Designers work at the “interface” and not “signal” level of abstraction when making connections between IP, greatly increasing productivity. Often times this is using industry standard AXI4 interfaces, but dozens of other interfaces are also supported by IP integrator.

Working at the interface level, design teams can rapidly assemble complex systems that leverages IP created with Vitis HLS, Model Composer, Xilinx SmartCore™ and LogiCORE™ IP, Alliance Member IP as well as your own IP. By leveraging the combination of Vivado IPI and HLS customers are saving up to 15X in development costs versus an RTL approach.

Vivado IP Integrator Key Features and Benefits

- Seamless inclusion of IP Integrator hierarchical subsystems into the overall design

- Rapid capture and packaging of IP Integrator designs for reuse

- Support for both graphical and Tcl-based design flows

- Rapid simulation and cross-probing between multiple design views

- Support for processor or processor-less designs

- Integration of algorithmic (Vitis HLS and Model Composer) and RTL-level IP

- Combination of DSP, video, analog, embedded, connectivity, and logic

- Support for Project based DFX Flow

- DRCs on complex interface level connections during design assembly

- Recognition and correction of common design errors

- Automatic IP parameter propagation to interconnected IP

- System-level optimizations

- Automated designer assistance

- Team Based designs using Block Design Container enables reusability and modular designs

- Revision control improvements separating source files from generated files

- Block Design Diff tool to compare two Block Designs

C-based IP Generation with Vitis High-Level Synthesis & Vitis Model Composer

As the leading provider of Electronic System Level Design tools for programmable solutions, Vivado provides Vitis™ High-Level Synthesis for C, C++ and SystemC, and you can buy an add-on Vitis model composer for DSP. These solutions enable high-level IP specifications to be directly synthesized into VHDL and Verilog, accelerating IP verification over 100X and RTL creation by up to 4X. The highly integrated tools can be used individually or in combination with the result being reusable IP for use in the Vivado ML Suite.

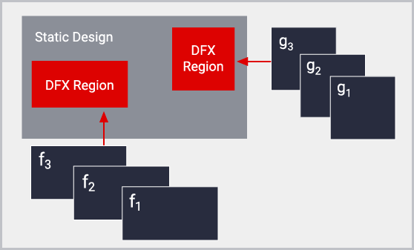

Dynamic Function eXchange (DFX)

Dynamic Function eXchange is the ability to dynamically modify blocks of logic by downloading partial bit files while the remaining logic continues to operate without interruption. Xilinx DFX technology allows designers to change functionality on the fly, eliminating the need to fully reconfigure and re-establish links, dramatically enhancing the flexibility that FPGAs and SoCs offer; it is a key capability for platform-based design flows, most notably for Alveo accelerator cards. The use of Dynamic Function eXchange can allow designers to move to fewer or smaller devices, reduce power, and improve system upgradability. Make more efficient use of the silicon by only loading in functionality that is needed at any point in time.

Dynamic Function eXchange Software

The Vivado® ML Design Suite software tools unlock the capability to reconfigure a portion of a Xilinx FPGA or SoC while the rest of the device remains operational. The current solution leverages the impressive implementation capabilities of the Vivado ML Design Suite, reducing the overhead necessary to create reconfigurable designs. Users can implement designs using the Tcl-based non-project flow or the RTL- or IP-based project flows. IP Integrator (IPI) design support was introduced in version 2021.1 through the use of Block Design Containers. RTL and IP project modes are supported within the Vivado IDE, with many underlying flow details automatically managed. Entry points to the design flow include high level languages processed via Vitis and HLS. Advanced flow features such as Nested DFX, which enables users to subdivide a dynamic region into lower-order dynamic regions, and Abstract Shell, which streamlines the implementation tool flow, greatly improving runtime, are available in non-project mode.

Four pieces of intellectual property are available to help designers complete DFX designs more quickly and easily. The Dynamic Function eXchange Controller is a hardware-based configuration controller that can help manage all aspects of reconfiguration events, from triggering and arbitration to bitstream delivery and error handling. The Dynamic Function eXchange Decoupler can be used with the DFX Controller or with any customer controller to safely isolate the dynamic region as it is being reconfigured. The Dynamic Function eXchange AXI Shutdown Manager helps users cease activity on AXI interfaces so Reconfigurable Partitions can be safely reconfigured. The Dynamic Function eXchange Bitstream Monitor allows users to debug and monitor partial bitstreams, ensuring version and target compatibility.

Most 7 series and Zynq®-7000 devices support Dynamic Function eXchange, with the only exceptions being the smallest devices within these families; some Artix-7 and all Spartan-7 are not supported. UltraScale™ support is complete, with all devices supported through bitstream generation in the current Vivado Design Suite version. UltraScale+™ device support covers all devices in production. Versal support was added with production status in Vivado 2021.1. See the DFX Reconfiguration User Guide (UG909), Appendix A, for the most up-to-date list.

UltraScale represented a new breakthrough in Dynamic Function eXchange technology, enabling reconfiguration of nearly all FPGA resource types, including I/O, Gigabit Transceivers, and clocking networks. UltraScale+ improved upon this capable family by streamlining bitstream delivery and expanding reconfiguration modes. Most recently, Versal support is a tremendous step forward in efficiency with software-based reconfiguration management, a reconfigurable network-on-chip, shared memory access, and floorplan granularity efficiencies.

Professors and researchers associated with universities may receive licenses for older versions of Vivado software through the Xilinx University Program (XUP). Learn more about access requirements and procedures for obtaining licenses here.

Key Features and Benefits

- Tcl-based non-project flow from HDL to bitstream, and RTL and IPI project modes in the Vivado IDE

- Efficient management of databases for static and reconfigurable modules

- Black box bitstream support, allowing incomplete modules to be omitted

- User decides how to manage reconfigurable module variants

- Keep the static design open in memory while modules are swapped in and out

- Floorplan determines what resources are reconfigured

- Tools manage Partition interfaces automatically, with no overhead

- Design Rule Checks (DRCs) validate design structure and configurations

- Standard timing closure techniques applied

- DFX is included at no additional cost within all Vivado® ML Design Suite editions. (Automatic inclusion in Vivado WebPack Edition began with version 2019.1.)

- Versal is now supported

- Not all devices in 7 series are covered

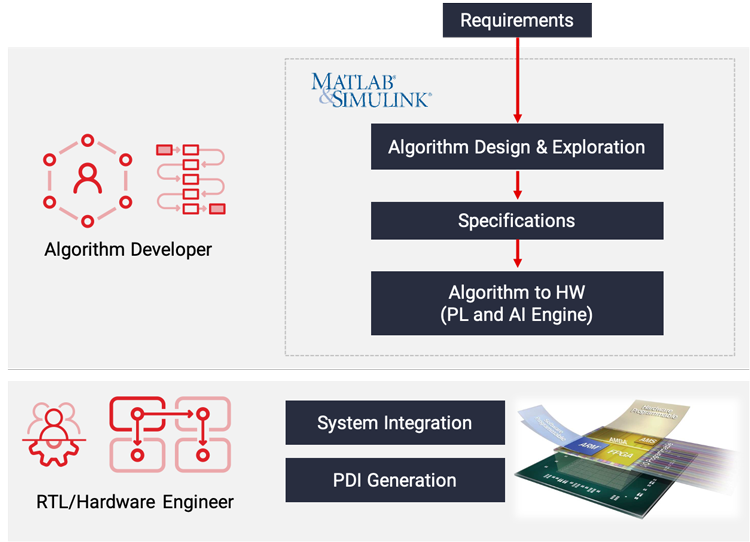

Vitis Model Composer

Vitis™ Model Composer is a Model-Based Design tool that enables rapid design exploration within the MathWorks MATLAB® and Simulink® environment and accelerates the path to production on Xilinx devices through automatic code generation. You can design your algorithms and iterate through them using high-level performance-optimized blocks and validate functional correctness through system-level simulations. Vitis Model Composer transforms your design to production-quality implementation through automatic optimizations. The tool provides a library of more than 200 HDL, HLS, and AI Engine blocks for the design and implementation of algorithms on Xilinx devices. It also enables importing custom HDL, HLS, and AI Engine code as blocks into the tool. Vitis Model Composer includes all the functionality of Xilinx System Generator for DSP which is no longer shipped as a standalone tool since 2020.2.

In Vitis Model Composer you can:

- Create a design using optimized blocks targeting AI Engines and Programmable Logic.

- Visualize and analyze simulation results and compare the output to golden references generated using MALTAB® and Simulink®.

- Seamlessly co-simulate AI Engine and Programmable Logic (HLS, HDL) blocks.

- Automatically generate code (AI Engines dataflow graph, RTL, HLS C++) and testbench for a design.

- Import custom HLS, AI Engines, and RTL code as blocks.

*Note:

Vitis Model composer can be purchased as an add-on license to any Vivado ML Edition.

For more information on how to download and buy please visit the Vitis Model Composer page.

Key Features

- High-Level of Abstraction: Algorithm-centric building blocks, with a focus on functionality, provide ease-of-use essential for domain experts to accelerate design exploration.

- Support for Vectors and Matrices: Enables frame-based algorithm design that saves you the time and effort to move to an intermediate low-level model for implementation.

- Application-Specific Libraries: Performance-optimized DSP, Computer Vision, Math, and Linear Algebra libraries available as blocks for simulation and high-performance implementation on Xilinx devices.

- Import synthesizable C/C++ as Custom Blocks: The ability to create your own custom blocks for simulation and code generation provides greater flexibility to design your differentiated algorithms.

- Seamless Integration with Simulink: Direct connection with blocks from the Simulink product family enables system-level modeling and simulation and the ability to fully leverage the stimulus generation and data visualization capabilities of Simulink's graphical environment.

- Integer, Floating and Fixed-point Support: Supports the native floating and integer data types in Simulink and the fixed-point and half data types supported by Vitis HLS.

- Automatic optimizations: Analyses your algorithmic specification within Simulink and performs automatic optimizations to steer towards a micro-architecture that optimizes for throughput, reduces Block RAM utilization, and enables concurrent execution of blocks.

- Accelerate IP Creation: Transform your simulated-able designs into an RTL IP package that you can use within the Vivado IP Integrator and leverage all the benefits of its plug-and-play IP Integration design environment for complex designs.

- Extend to System Generator for DSP: Leverage the benefits of Model Composer's ease-of-use and simulation speed, for portions of your design and export the synthesized RTL into your existing System Generator for DSP designs as new custom blocks.

- Export to Vitis HLS: Advanced feature that provides a link between Simulink's graphical environment to design, simulate and validate your algorithms and Vitis HLS, by automatically generating everything you would need to further optimize your algorithm, including test vectors logged from simulation.

- User Interface to Map RTL Interfaces: Easy to use the graphical interface to map the inputs and outputs in your design to supported RTL interfaces (AXI4-Lite, AXI4-Stream, AXI4-Stream Video, FIFO, Block RAM) and video formats (AXI4-Stream Video) for implementation.

- Automatic Test Bench Generation: Automatic logging of test vectors from simulation and generation of a test bench to verify functional equivalence between the executable design and generated code.