# System Generator for DSP

User Guide

UG640 (v 14.2) July 25, 2012

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2006 - 2012. Xilinx, Inc. XILINX, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

# Table of Contents

## Chapter 1: Hardware Design Using System Generator

| A Brief Introduction to FPGAs                                     |        |

|-------------------------------------------------------------------|--------|

| Note to the DSP Engineer                                          |        |

| Note to the Hardware Engineer                                     | 15     |

| Design Flows using System Generator.                              | 15     |

| Algorithm Exploration                                             |        |

| Implementing Part of a Larger Design                              | 15     |

| Implementing a Complete Design                                    |        |

| System-Level Modeling in System Generator                         |        |

| System Generator Blocksets                                        |        |

| Signal Types                                                      |        |

| Floating-Point Data Type                                          |        |

| AXI Signal Groups                                                 |        |

| Bit-True and Cycle-True Modeling                                  | · · 24 |

| Timing and Clocking                                               |        |

|                                                                   |        |

| Synchronization Mechanisms                                        |        |

| Block Masks and Parameter Passing                                 |        |

|                                                                   |        |

| Automatic Code Generation                                         |        |

| Compiling and Simulating Using the System Generator Token         |        |

| Viewing ISE Reports                                               |        |

| Compilation Results                                               |        |

| HDL Testbench                                                     |        |

| Compiling MATLAB into an FPGA                                     | 51     |

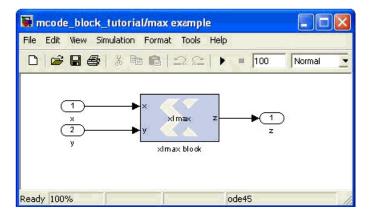

| Simple Selector                                                   |        |

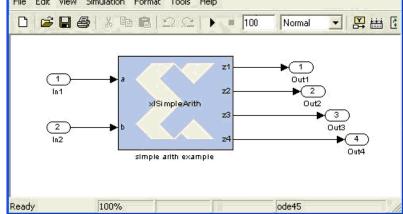

| Simple Arithmetic Operations                                      |        |

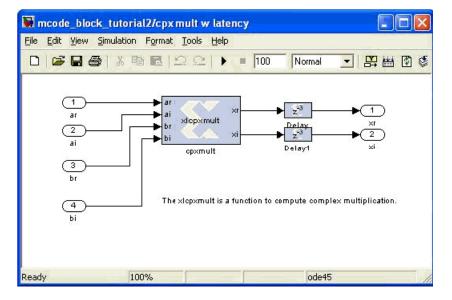

| Complex Multiplier with Latency                                   | 55     |

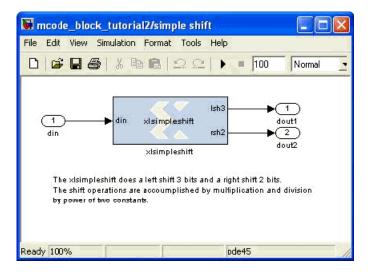

| Shift Operations                                                  | 56     |

| Passing Parameters into the MCode Block                           |        |

| Optional Input Ports                                              |        |

| Finite State Machines                                             |        |

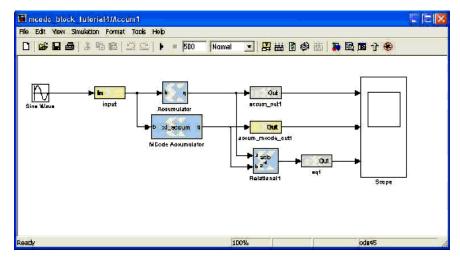

| Parameterizable Accumulator                                       |        |

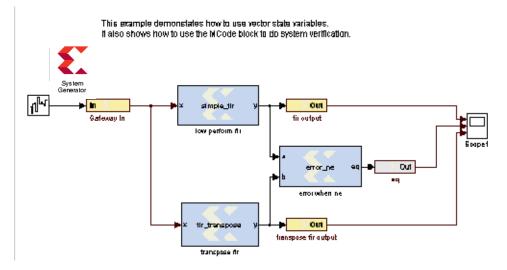

| FIR Example and System Verification                               |        |

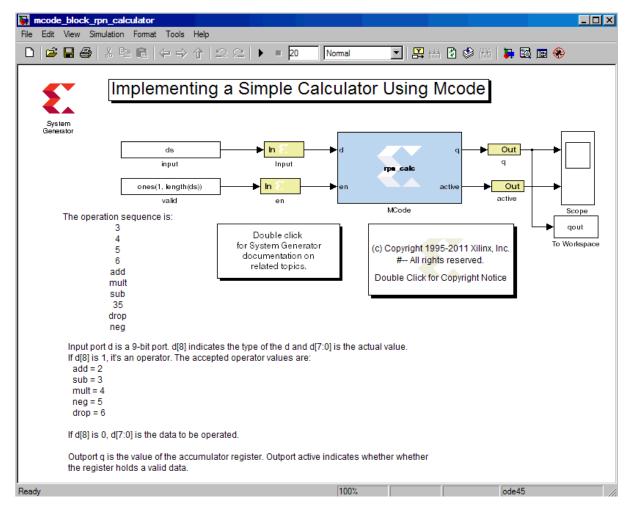

| RPN Calculator                                                    |        |

| Example of disp Function                                          | 71     |

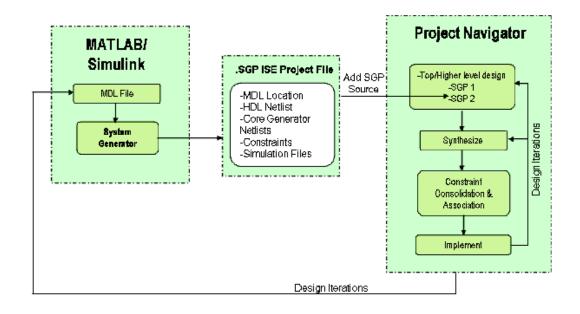

| Importing a System Generator Design into a Bigger System          | 73     |

| HDL Netlist Compilation                                           | 73     |

| Integration Design Rules                                          | 73     |

| New Integration Flow between System Generator & Project Navigator | 74     |

| A Step-by-Step Example                                            | 75     |

| Generating a PlanAhead Project File from System Generator         | 82     |

| Step-by-Step Example for Generating a PlanAhead Project File      |        |

| Importing a System Generator Design into PlanAhead                |        |

| Steps to Import a System Generator Design as a Sub-Module         |        |

| Creating a New System Generator Design from within PlanAhead      |        |

|                                                                   |        |

| Configurable Subsystems and System Generator                      | 88     |

www.xilinx.com

| Defining a Configurable Subsystem                                          | . 88 |

|----------------------------------------------------------------------------|------|

| Using a Configurable Subsystem                                             | . 90 |

| Deleting a Block from a Configurable Subsystem                             | . 91 |

| Adding a Block to a Configurable Subsystem                                 | . 91 |

| Generating Hardware from Configurable Subsystems                           |      |

| Notes for Higher Performance FPGA Design                                   |      |

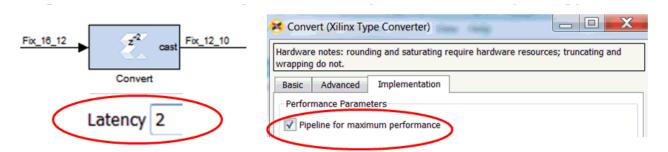

| Review the Hardware Notes Included with Each Block Dialog Box              |      |

|                                                                            |      |

| Register the Inputs and Outputs of Your Design                             |      |

| Insert Pipeline Registers                                                  |      |

| Use Saturation Arithmetic and Rounding Only When Necessary                 |      |

| Use the System Generator Timing and Power Analysis Tools                   |      |

| Set the Data Rate Option on All Gateway Blocks                             |      |

| Reduce the Clock Enable (CE) Fanout                                        | . 97 |

| Experiment with Different Synthesis Settings                               | . 98 |

| Other Things to Try                                                        | . 98 |

| Processing a System Generator Design with FPGA Physical Design Tools       | . 99 |

| HDL Simulation                                                             |      |

| Generating an FPGA Bitstream                                               |      |

| 0                                                                          |      |

| Resetting Auto-Generated Clock Enable Logic                                | 105  |

| ce_clr and Rate Changing Blocks                                            |      |

| ce_clr Usage Recommendations                                               |      |

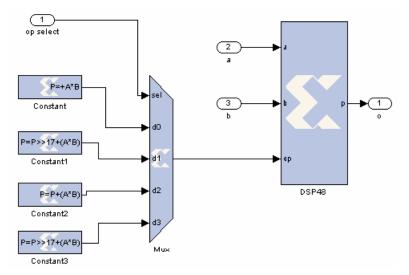

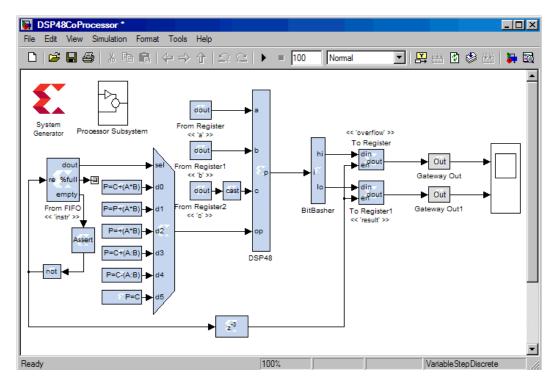

| Design Styles for the DSP48                                                | 108  |

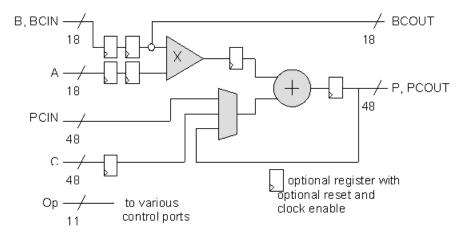

| About the DSP48                                                            |      |

| Designs Using Standard Components                                          |      |

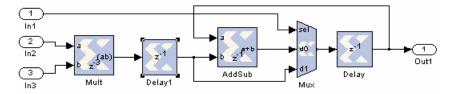

| Designs Using Synthesizable Mult, Mux and AddSub Blocks                    |      |

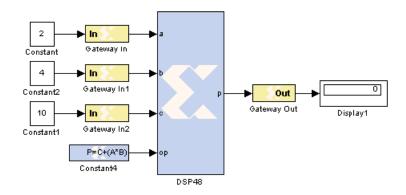

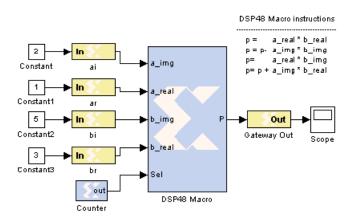

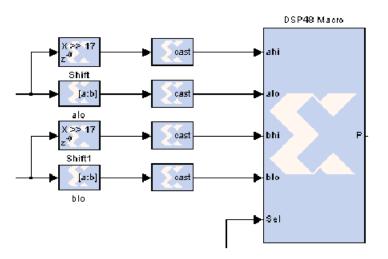

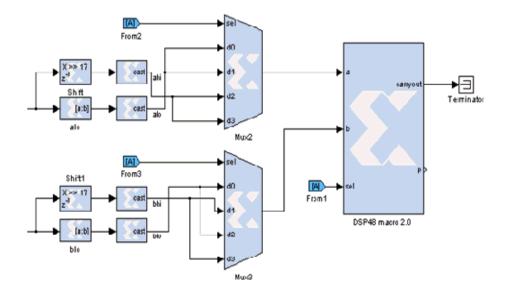

| Designs that Use DSP48 and DSP48 Macro Blocks                              | 110  |

| DSP48 Design Techniques                                                    | 115  |

| ů i                                                                        |      |

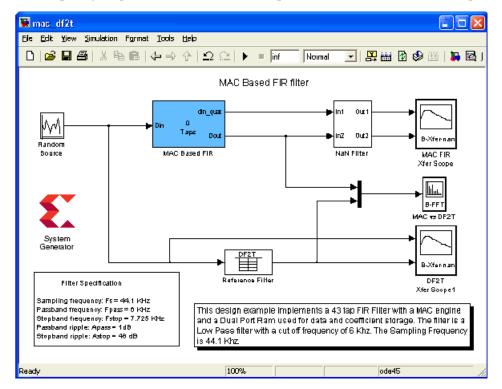

| Using FDATool in Digital Filter Applications                               | 118  |

| Design Overview                                                            | 119  |

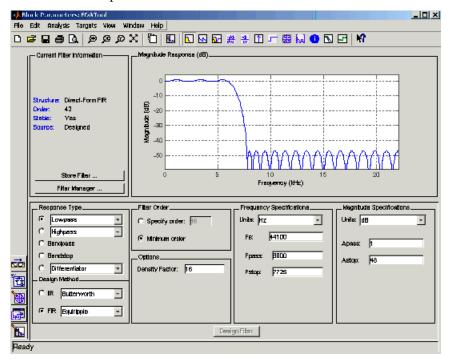

| Open and Generate the Coefficients for this FIR Filter                     |      |

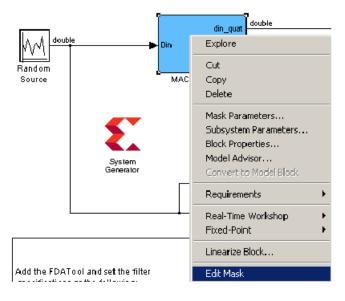

| Parameterize the MAC-Based FIR Block                                       |      |

| Generate and Assign Coefficients for the FIR Filter                        | 121  |

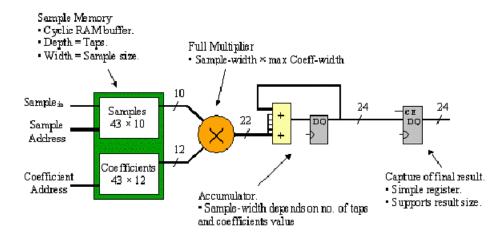

| Browse Through and Understand the Xilinx Filter Block                      | 123  |

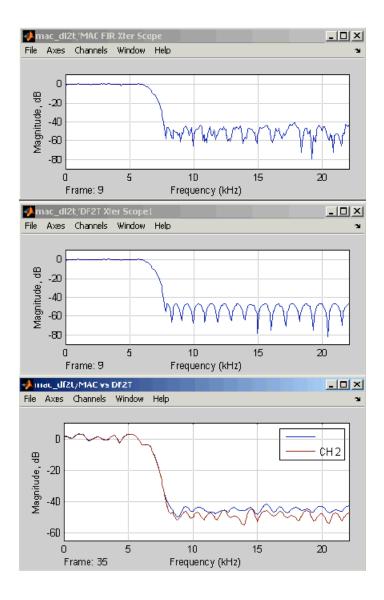

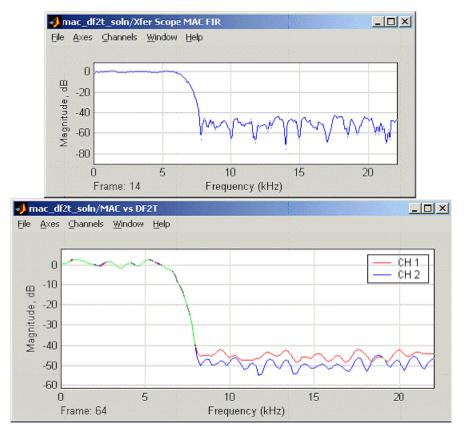

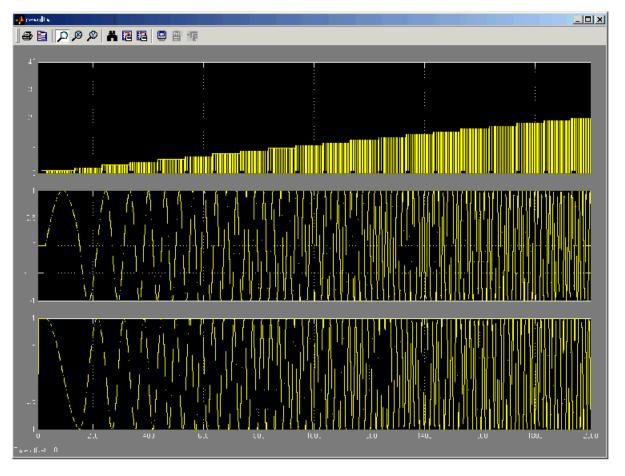

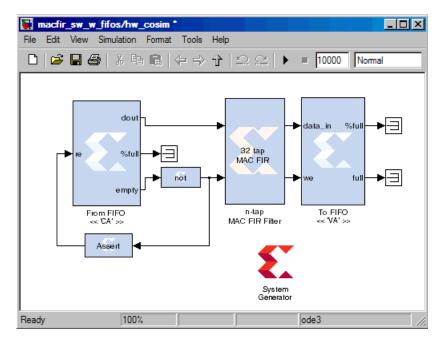

| Run the Simulation                                                         |      |

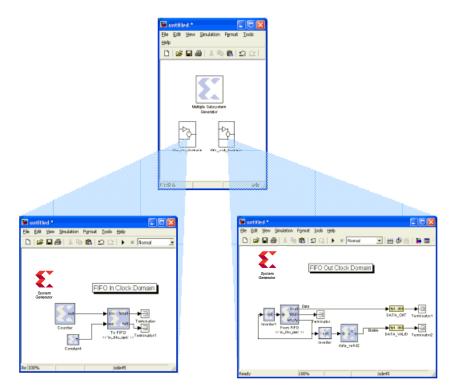

| Generating Multiple Cycle-True Islands for Distinct Clocks                 | 127  |

| Multiple Clock Applications                                                |      |

| Clock Domain Partitioning                                                  |      |

| Crossing Clock Domains                                                     |      |

|                                                                            |      |

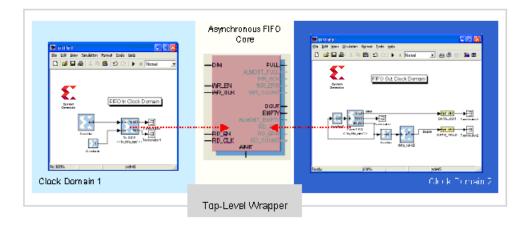

| Netlisting Multiple Clock Designs                                          |      |

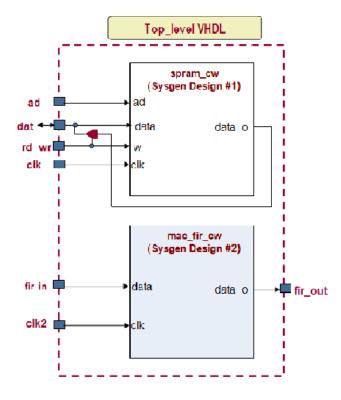

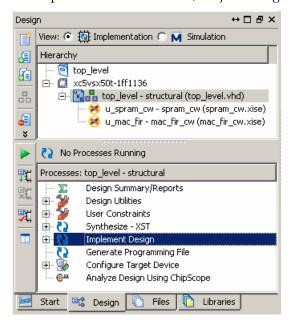

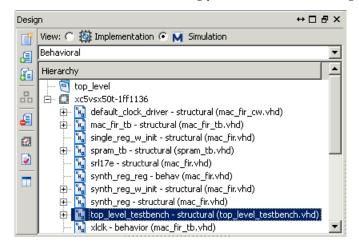

| Step-by-Step Example                                                       | 131  |

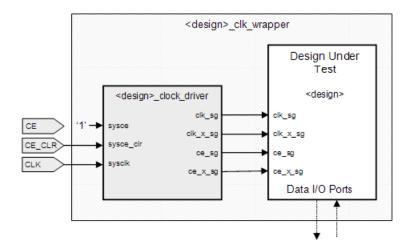

| Creating a Top-Level Wrapper                                               |      |

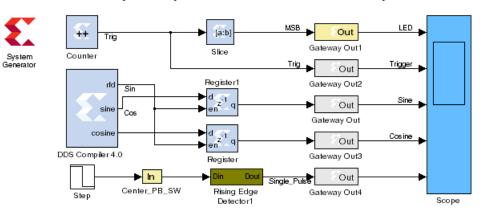

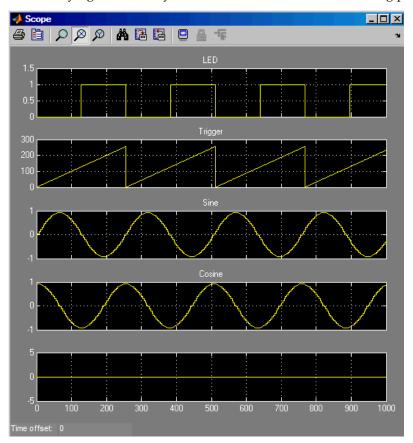

| Using ChipScope Pro Analyzer for Real-Time Hardware Debugging              | 139  |

| ChipScope Pro Overview                                                     | 139  |

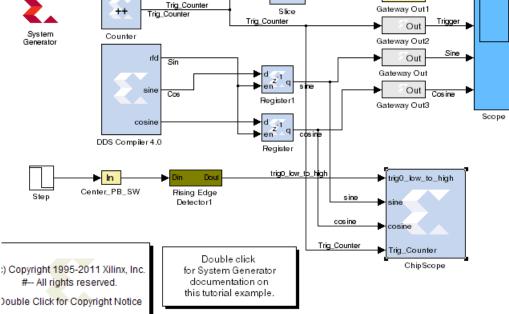

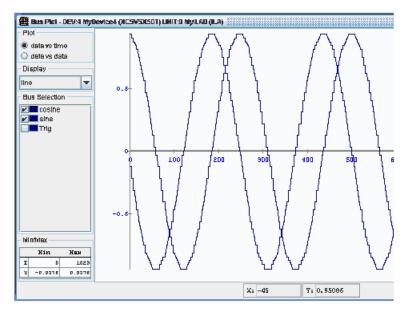

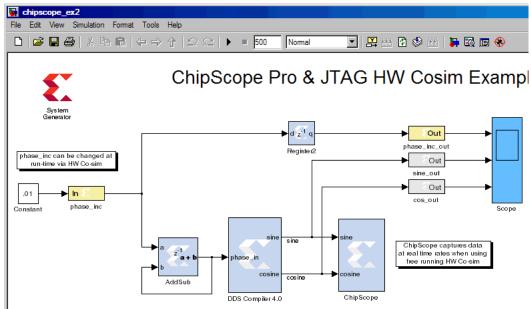

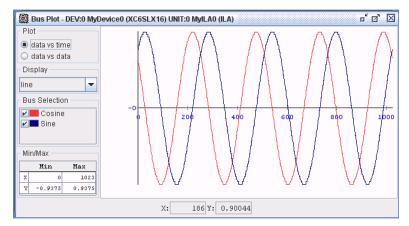

| Tutorial Example: Using ChipScope in System Generator                      | 139  |

| Real-Time Debug                                                            | 145  |

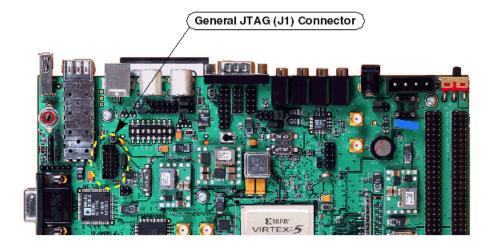

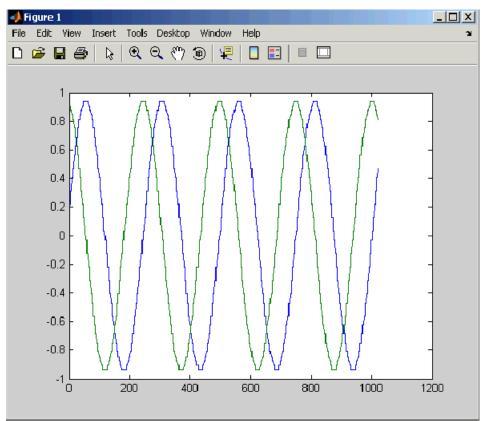

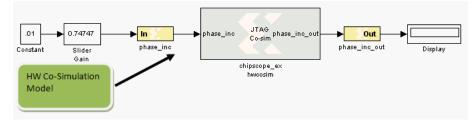

| Tutorial Example: Using ChipScope Pro Analyzer with JTAG Hardware Co-Simul |      |

| AXI Interface                                                              |      |

| Introduction                                                               |      |

|                                                                            |      |

| AXI4 Support in System Generator                                           |      |

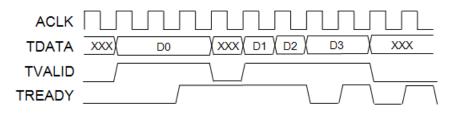

| AXI4-Stream Support in System Generator                                    |      |

| AXI-Stream Blocks in System Generator                                      | 153  |

## : Hardware/Software Co-Design

| Hardware/Software Co-Design in System Generator                                      |

|--------------------------------------------------------------------------------------|

| Black Box Block 156                                                                  |

| PicoBlaze Block                                                                      |

| EDK Processor Block 156                                                              |

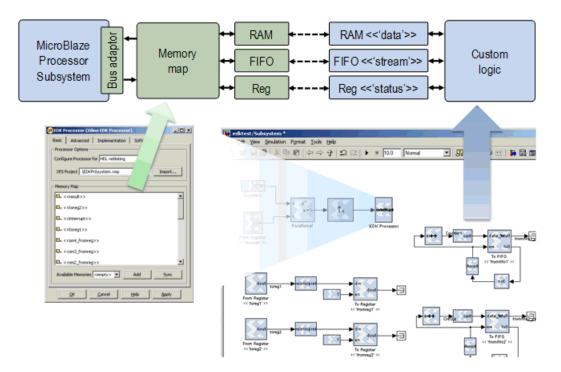

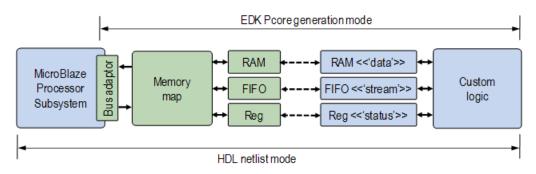

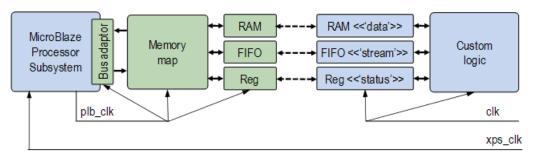

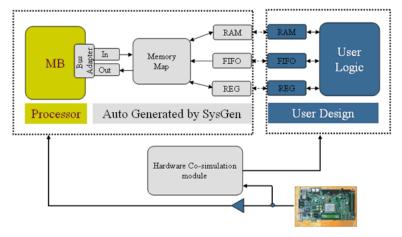

| Integrating a Processor with Custom Logic                                            |

| Memory Map Creation 158                                                              |

| Hardware Generation                                                                  |

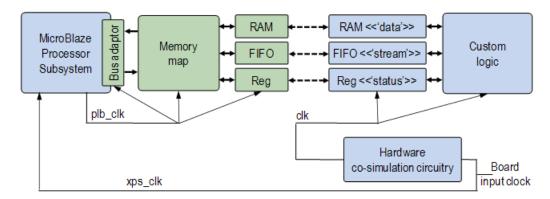

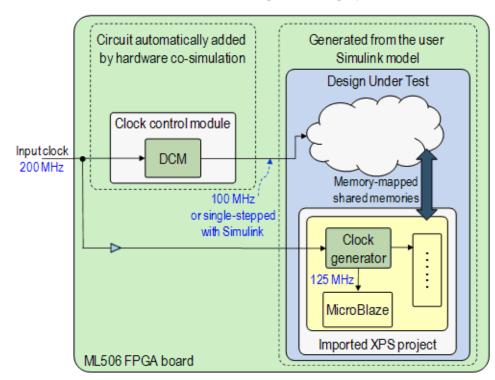

| Hardware Co-Simulation                                                               |

| The Software Driver                                                                  |

| Writing a Software Program 163                                                       |

| Asynchronous Support                                                                 |

| Clock Wiring in the Hardware Co-Simulation Flow                                      |

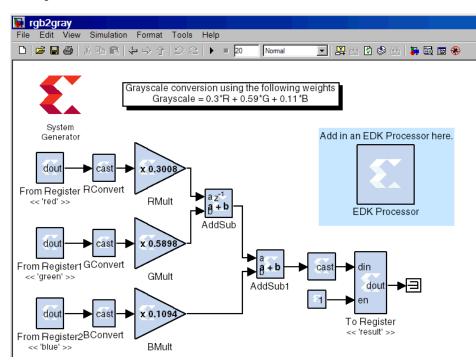

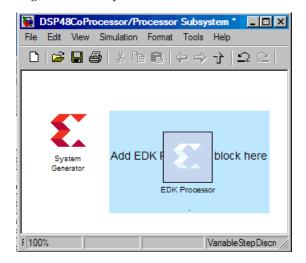

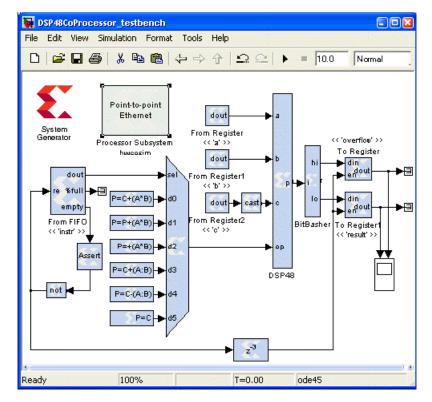

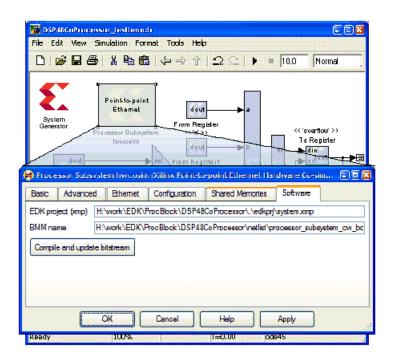

| <b>EDK Support</b>                                                                   |

| Importing an EDK Processor 175                                                       |

| Exposing Processor Ports to System Generator                                         |

| Exporting a pcore 178                                                                |

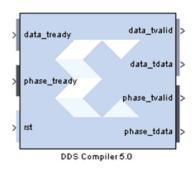

| Designing with Embedded Processors and Microcontrollers 178                          |

| Designing PicoBlaze Microcontroller Applications 178                                 |

| Designing and Exporting MicroBlaze Processor Peripherals                             |

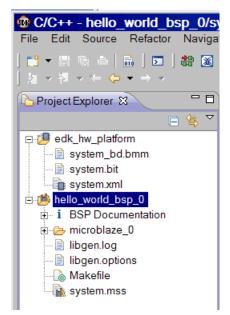

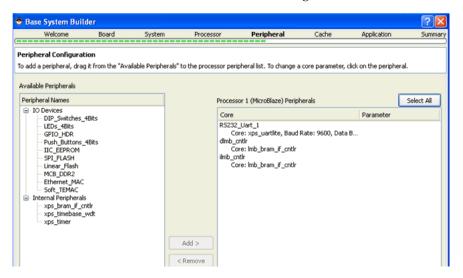

| Using XPS                                                                            |

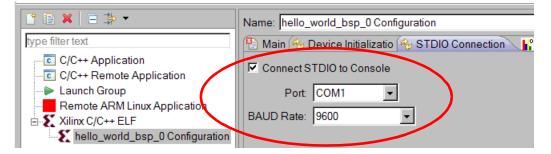

| Using Platform Studio SDK                                                            |

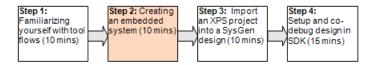

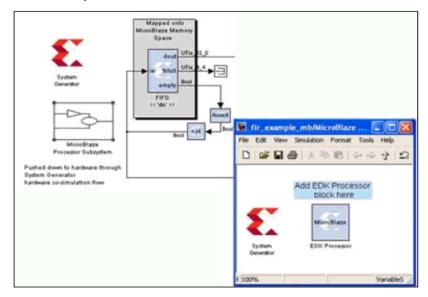

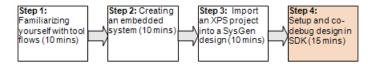

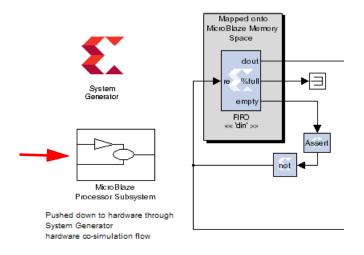

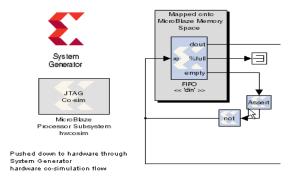

| Tutorial Example - Using System Generator and SDK to Co-Debug an Embedded DSP Desigr |

| 214                                                                                  |

| Summary                                                                              |

## Chapter 3: Using Hardware Co-Simulation

| Introduction                                         |

|------------------------------------------------------|

| M-Code Access to Hardware Co-Simulation              |

| Installing Your Hardware Board 239                   |

| Ethernet-Based Hardware Co-Simulation                |

| JTAG-Based Hardware Co-Simulation                    |

| Third-Party Hardware Co-Simulation    240            |

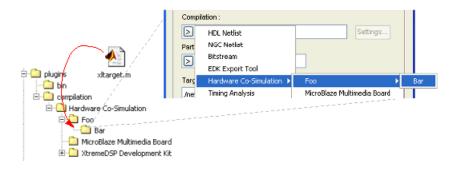

| Compiling a Model for Hardware Co-Simulation         |

| Choosing a Compilation Target                        |

| Invoking the Code Generator                          |

| Hardware Co-Simulation Blocks 242                    |

| Hardware Co-Simulation Clocking                      |

| Selecting the Target Clock Frequency 245             |

| Clocking Modes                                       |

| Selecting the Clock Mode                             |

| Board-Specific I/O Ports                             |

| I/O Ports in Hardware Co-simulation                  |

| Ethernet Hardware Co-Simulation                      |

| Point-to-Point Ethernet Hardware Co-Simulation       |

| Network-Based Ethernet Hardware Co-Simulation        |

| Remote JTAG Cable Support in JTAG Co-Simulation      |

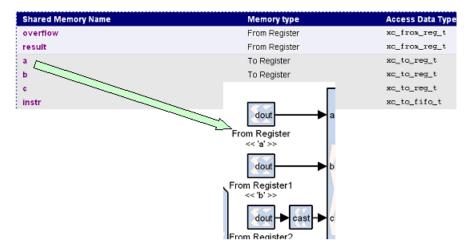

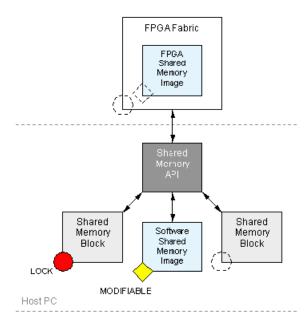

| Shared Memory Support                                |

| Compiling Shared Memories for Hardware Co-Simulation |

| Co-Simulating Unprotected Shared Memories            |

|                                                      |

| Co-Simulating Lockable Shared Memories                                                                           |     |

|------------------------------------------------------------------------------------------------------------------|-----|

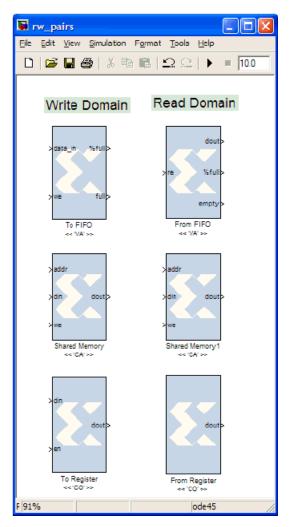

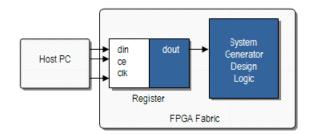

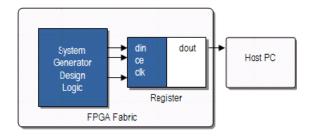

| Co-Simulating Shared Registers                                                                                   |     |

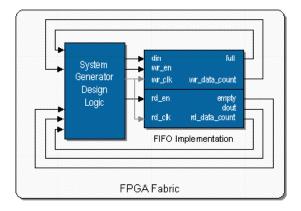

| Co-Simulating Shared FIFOs                                                                                       |     |

| Restrictions on Shared Memories                                                                                  |     |

| Specifying Xilinx Tool Flow Settings                                                                             | 266 |

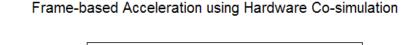

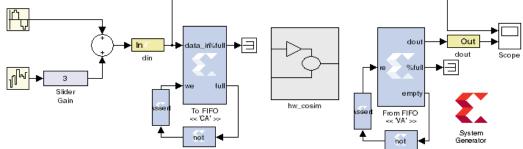

| Frame-Based Acceleration using Hardware Co-Simulation                                                            |     |

| Shared Memories                                                                                                  |     |

| Adding Buffers to a Design                                                                                       |     |

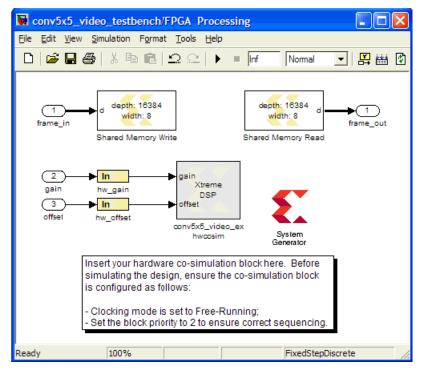

| Compiling for Hardware Co-simulation                                                                             |     |

| Using Vector Transfers                                                                                           |     |

| Real-Time Signal Processing using Hardware Co-Simulation                                                         |     |

| Shared Memory I/O Buffering Example                                                                              |     |

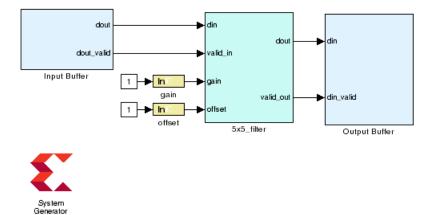

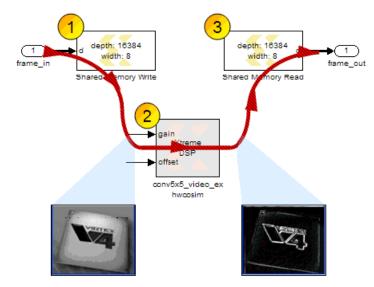

| Applying a 5x5 Filter Kernel Data Path                                                                           |     |

| 5x5 Filter Kernel Test Bench                                                                                     |     |

| Reloading the Kernel                                                                                             |     |

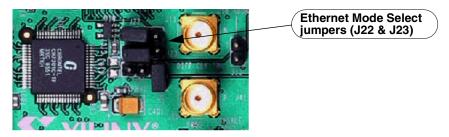

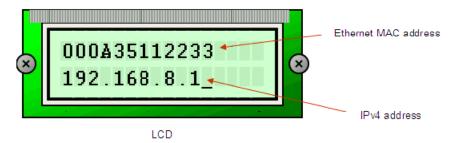

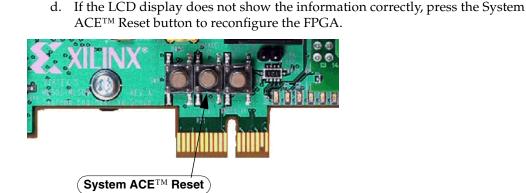

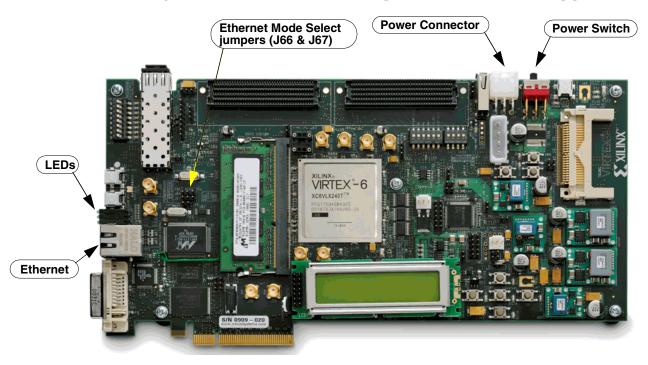

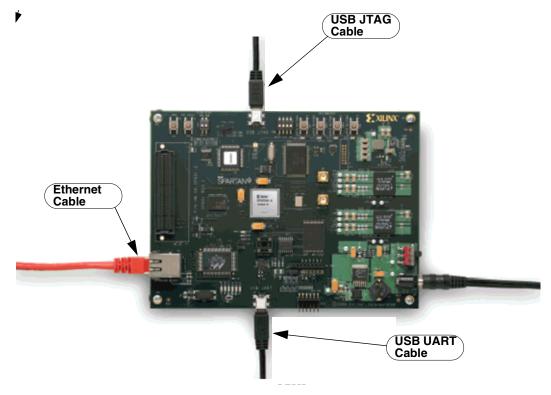

| Installing Your Board for Ethernet Hardware Co-Simulation                                                        |     |

| Installing Software on the Host PC                                                                               |     |

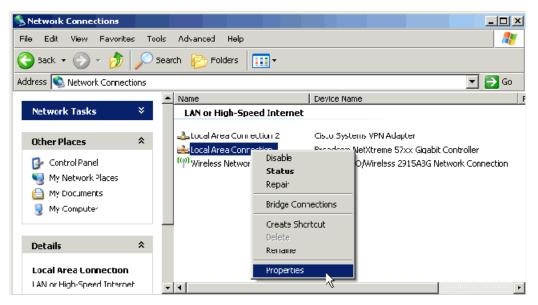

| Setting Up the Local Area Network on the PC                                                                      |     |

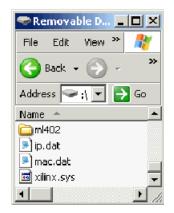

| Loading the Sysgen HW Co-Sim Configuration Files                                                                 |     |

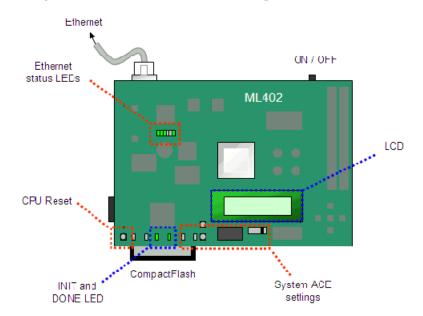

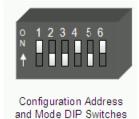

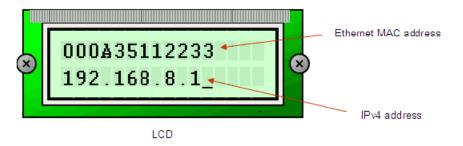

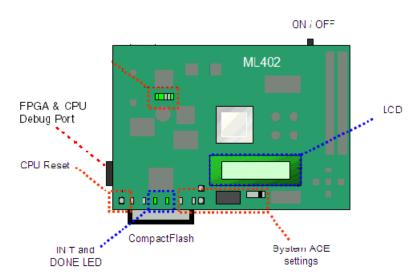

| Installing the Proxy Executable for Linux Users<br>Installing an ML402 Board for Ethernet Hardware Co-Simulation |     |

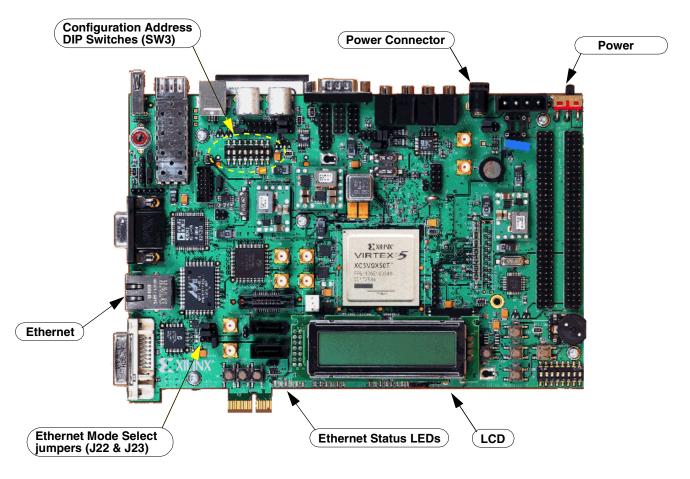

| Installing an ML506 Board for Ethernet Hardware Co-Simulation                                                    |     |

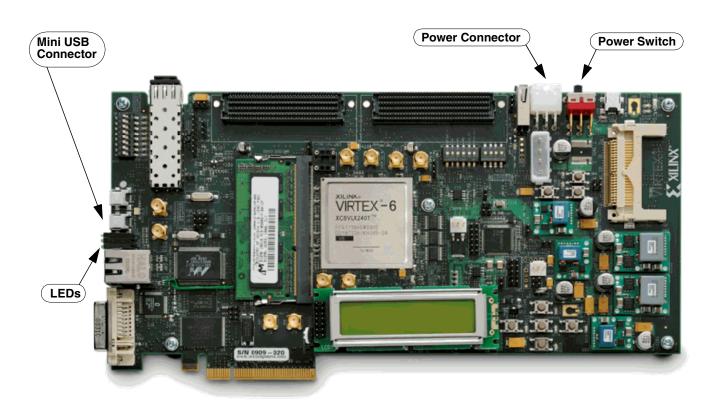

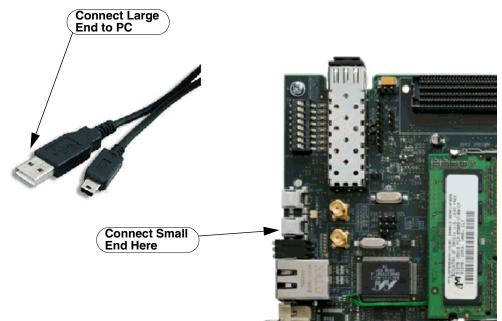

| Installing an ML605 Board for Ethernet Hardware Co-Simulation                                                    |     |

| Installing a Spartan-3A DSP 1800A Starter Board for Ethernet Hardware Co-Simul                                   |     |

| Installing a Spartan-3A DSP 3400A Board for Ethernet Hardware Co-Simulation .                                    | 308 |

| Installing an SP601/SP605 Board for Ethernet Hardware Co-Simulation                                              |     |

| Installing Your Board for JTAG Hardware Co-Simulation                                                            | 315 |

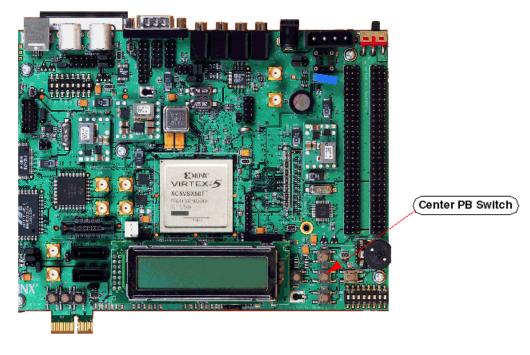

| Installing an ML402 Board for JTAG Hardware Co-Simulation                                                        | 315 |

| Installing an ML605 Board for JTAG Hardware Co-Simulation                                                        |     |

| Installing an SP601/SP605 Board for JTAG Hardware Co-Simulation                                                  |     |

| Installing a KC705 Board for JTAG Hardware Co-Simulation                                                         |     |

| Supporting New Boards through JTAG Hardware Co-Simulation                                                        |     |

| Hardware Requirements                                                                                            |     |

| Supporting New Boards                                                                                            | 323 |

## Chapter 4: Importing HDL Modules

| Black Box HDL Requirements and Restrictions 3 | 338 |

|-----------------------------------------------|-----|

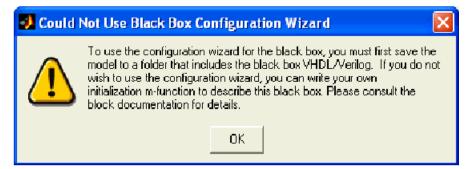

| Black Box Configuration Wizard 3              | 339 |

| Black Box Configuration M-Function 3          | 340 |

| HDL Co-Simulation                             | 354 |

| Introduction                                  | 354 |

| Configuring the HDL Simulator                 | 354 |

| Co-Simulating Multiple Black Boxes 3          |     |

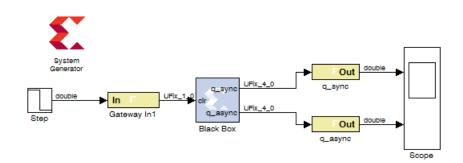

| Black Box Examples                            | 357 |

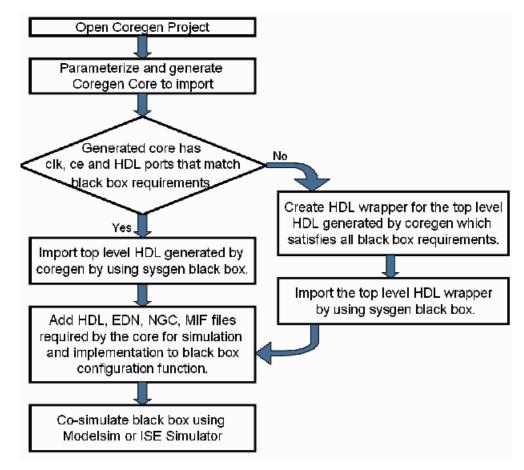

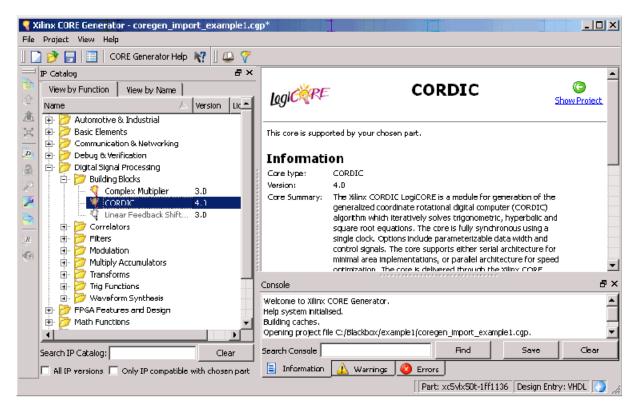

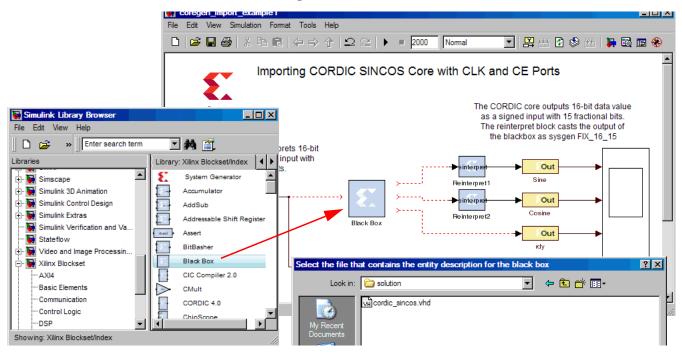

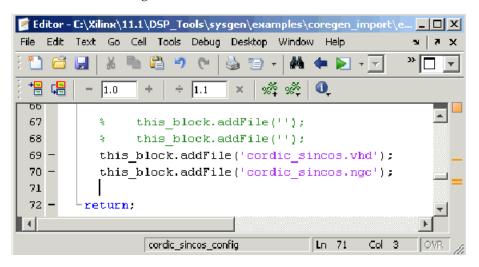

| Importing a Xilinx Core Generator Module      | 357 |

| Importing a VHDL Module 3                     |     |

| Importing a Verilog Module                    | 378 |

| Dynamic Black Boxes 3                         | 380 |

| Simulating Several Black Boxes Simultaneously | 382 |

| Advanced Black Box Example Using ModelSim     | 384 |

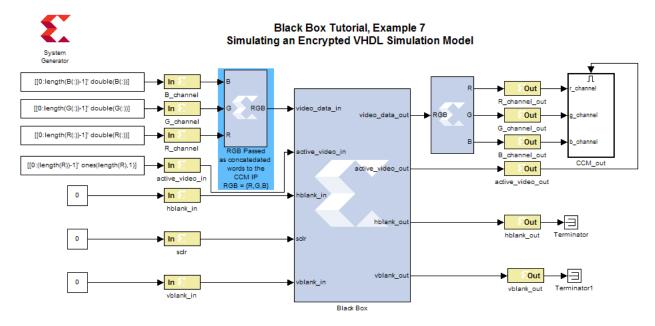

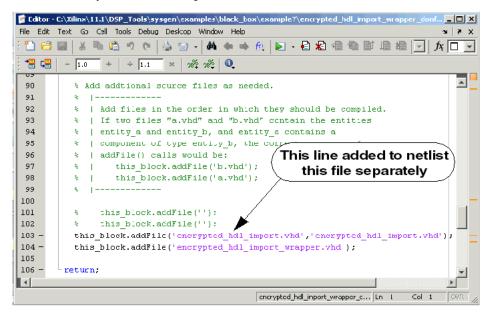

| Importing, Simulating, and Exporting an Encrypted VHDL File                      | 389     |

|----------------------------------------------------------------------------------|---------|

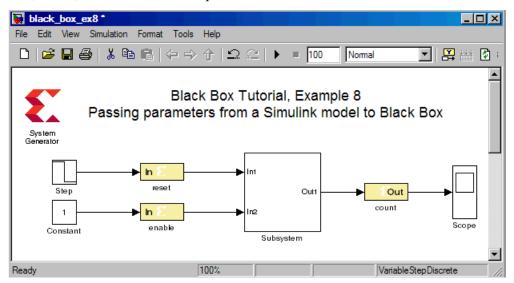

| Black Box Tutorial Exercise 9: Prompting a User for Parameters in a Simulink Mod | lel and |

| Passing Them to a Black Box                                                      | 394     |

## Chapter 5: System Generator Compilation Types

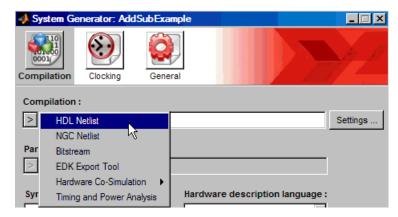

| HDL Netlist Compilation 398                                      |

|------------------------------------------------------------------|

| NGC Netlist Compilation 398                                      |

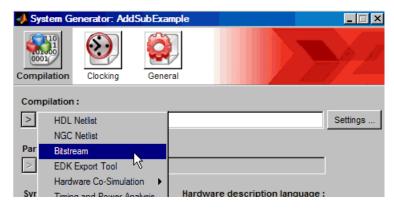

| Bitstream Compilation 399                                        |

| XFLOW Option Files 400                                           |

| Additional Settings 401                                          |

| Re-Compiling EDK Processor Block Software Programs in Bitstreams |

| <b>EDK Export Tool</b>                                           |

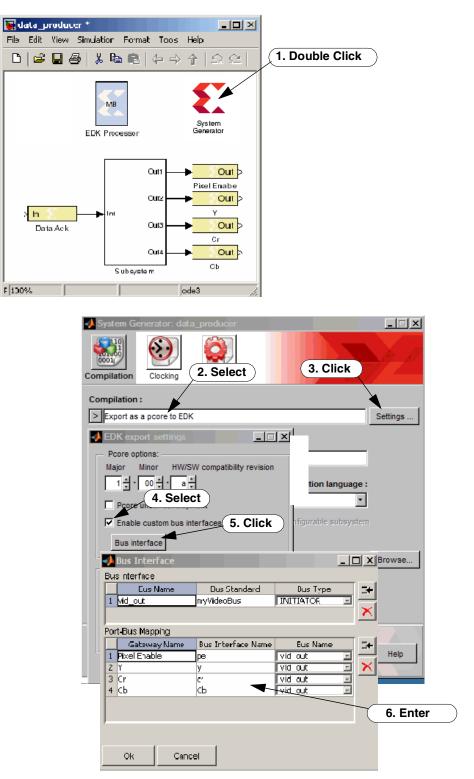

| Creating a Custom Bus Interface for Pcore Export                 |

| Export as Pcore to EDK 405                                       |

| System Generator Ports as Top-Level Ports in EDK                 |

| Supported Processors and Current Limitations                     |

| See Also:                                                        |

| Hardware Co-Simulation Compilation                               |

| Timing and Power Analysis Compilation                            |

| Timing Analysis Concepts Review    409                           |

| Timing Analyzer Features    410                                  |

| Creating Compilation Targets                                     |

| Defining New Compilation Targets                                 |

|                                                                  |

| Index                                                            |

www.xilinx.com

## Chapter 1

## Hardware Design Using System Generator

System Generator is a system-level modeling tool that facilitates FPGA hardware design. It extends Simulink in many ways to provide a modeling environment that is well suited to hardware design. The tool provides high-level abstractions that are automatically compiled into an FPGA at the push of a button. The tool also provides access to underlying FPGA resources through low-level abstractions, allowing the construction of highly efficient FPGA designs.

| A Brief Introduction to FPGAs                                | Provides background on FPGAs, and discusses compilation, programming, and architectural considerations in the context of System Generator.                                                                                                                                                   |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Flows using System<br>Generator                       | Describes several settings in which constructing designs in System Generator is useful.                                                                                                                                                                                                      |

| System-Level Modeling in<br>System Generator                 | Discusses System Generator's ability to implement<br>device-specific hardware designs directly from a<br>flexible, high-level, system modeling environment.                                                                                                                                  |

| Automatic Code Generation                                    | Discusses automatic code generation for System Generator designs.                                                                                                                                                                                                                            |

| Compiling MATLAB into an FPGA                                | Describes how to use a subset of the MATLAB<br>programming language to write functions that<br>describe state machines and arithmetic operators.<br>Functions written in this way can be attached to<br>blocks in System Generator and can be automatically<br>compiled into equivalent HDL. |

| Importing a System Generator<br>Design into a Bigger System  | Discusses how to take the VHDL netlist from a System<br>Generator design and synthesize it in order to embed<br>it into a larger design. Also shows how VHDL created<br>by System Generator can be incorporated into a<br>simulation model of the overall system.                            |

| Generating a PlanAhead Project<br>File from System Generator | Provides an example of how to generate a PlanAhead<br>project file (with design strategies) and invoke<br>PlanAhead from within System Generator.                                                                                                                                            |

| Configurable Subsystems and<br>System Generator                            | Explains how to use configurable subsystems in<br>System Generator. Describes common tasks such as<br>defining configurable subsystems, deleting and<br>adding blocks, and using configurable subsystems to<br>import compilation results into System Generator<br>designs. |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Notes for Higher Performance<br>FPGA Design                                | Suggests design practices in System Generator that<br>lead to an efficient and high-performance<br>implementation in an FPGA.                                                                                                                                               |

| Processing a System Generator<br>Design with FPGA Physical<br>Design Tools | Describes how to take the low-level HDL produced by<br>System Generator and use it in tools like Xilinx's<br>Project Navigator, ModelSim, and Synplicity's<br>Synplify.                                                                                                     |

| Resetting Auto-Generated Clock<br>Enable Logic                             | Describes the behavior of rate changing blocks from the System Generator library when the ce_clr signal is used for re-synchronization.                                                                                                                                     |

| Design Styles for the DSP48                                                | Describes three ways to implement and configure a DSP48 (Xtreme DSP Slice) in System Generator                                                                                                                                                                              |

| Using FDATool in Digital Filter<br>Applications                            | Demonstrates one way to specify, implement and simulate a FIR filter using the FDATool block.                                                                                                                                                                               |

| Generating Multiple Cycle-True<br>Islands for Distinct Clocks              | Describes how to implement multi-clock designs in<br>System Generator                                                                                                                                                                                                       |

| Using ChipScope Pro Analyzer<br>for Real-Time Hardware<br>Debugging        | Demonstrates how to connect and use the Xilinx<br>Debug Tool called ChipScope <sup>™</sup> Pro within System<br>Generator                                                                                                                                                   |

| AXI Interface                                                              | Provides an introduction to AMBA AXI4 and draws attention to AMBA AXI4 details with respect to System Generator.                                                                                                                                                            |

## A Brief Introduction to FPGAs

A field programmable gate array (FPGA) is a general-purpose integrated circuit that is "programmed" by the designer rather than the device manufacturer. Unlike an application-specific integrated circuit (ASIC), which can perform a similar function in an electronic system, an FPGA can be reprogrammed, even after it has been deployed into a system.

An FPGA is programmed by downloading a configuration program called a bitstream into static on-chip random-access memory. Much like the object code for a microprocessor, this bitstream is the product of compilation tools that translate the high-level abstractions produced by a designer into something equivalent but low-level and executable. Xilinx System Generator pioneered the idea of compiling an FPGA program from a high-level Simulink model.

An FPGA provides you with a two-dimensional array of configurable resources that can implement a wide range of arithmetic and logic functions. These resources include dedicated DSP blocks, multipliers, dual port memories, lookup tables (LUTs), registers, tristate buffers, multiplexers, and digital clock managers. In addition, Xilinx FPGAs contain sophisticated I/O mechanisms that can handle a wide range of bandwidth and voltage requirements. The Virtex®-4 FPGAs include embedded microcontrollers (IBM PowerPC®)

405), and multi-gigabit serial transceivers. The compute and I/O resources are linked under the control of the bitstream by a programmable interconnect architecture that allows them to be wired together into systems.

FPGAs are high performance data processing devices. DSP performance is derived from the FPGA's ability to construct highly parallel architectures for processing data. In contrast with a microprocessor or DSP processor, where performance is tied to the clock rate at which the processor can run, FPGA performance is tied to the amount of parallelism that can be brought to bear in the algorithms that make up a signal processing system. A combination of increasingly high system clock rates (current system frequencies of 100-200 MHz are common today) and a highly-distributed memory architecture gives the system designer an ability to exploit parallelism in DSP (and other) applications that operate on data streams. For example, the raw memory bandwidth of a large FPGA running at a clock rate of 150 MHz can be hundreds of terabytes per second.

There are many DSP applications (e.g., digital up/down converters) that can be implemented only in custom integrated circuits (ICs) or in an FPGA; a von Neumann processor lacks both the compute capability and the memory bandwidth required. Advantages of using an FPGA include significantly lower non-recurring engineering costs than those associated with a custom IC (FPGAs are commercial off-the-shelf devices), shorter time to market, and the configurability of an FPGA, which allows a design to be modified, even after deployment in an end application.

When working in System Generator, it is important to keep in mind that an FPGA has many degrees of freedom in implementing signal processing functions. You have, for example, the freedom to define data path widths throughout your system and to employ many individual data processors (e.g., multiply-accumulate engines), depending on system requirements. System Generator provides abstractions that allow you to design for an FPGA largely by thinking about the algorithm you want to implement. However, the more you know about the underlying FPGA, the more likely you are to exploit the unique capabilities an FPGA provides in achieving high performance.

The remainder of this topic is a brief introduction to some of the logic resources available in the FPGA, so that you gain some appreciation for the abstractions provided in System Generator.

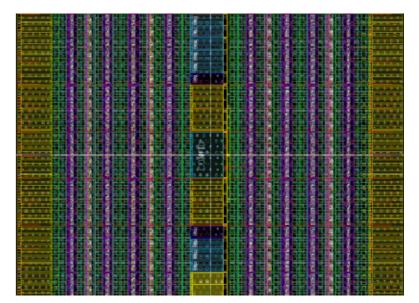

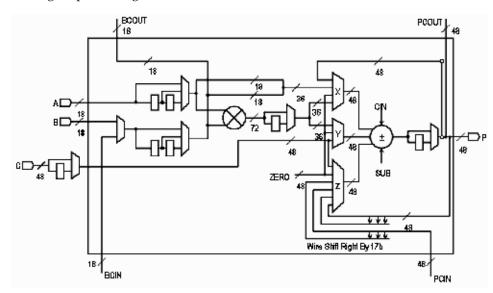

The figure above shows a physical view of a Virtex®-4 FPGA. To a signal DSP engineer, an FPGA can be thought of as a 2-D array of logic slices striped with columns of hard macro blocks (block memory and arithmetic blocks) suitable for implementing DSP functions, embedded within a configurable interconnect mesh. In a Virtex®-4 FPGA, the DSP blocks (shown in the next figure) can run in excess of 450 MHz, and are pitch-matched to dual port memory blocks (BRAMs) whose ports can be configured to a wide range of word sizes (18 Kb total per BRAM). The Virtex®-4 SX55 device contains 512 such DSP blocks and BRAMs. In System Generator, you can access all of these resources through arithmetic and logic abstractions to build very high performance digital filters, FFTs, and other arithmetic and signal processing functions.

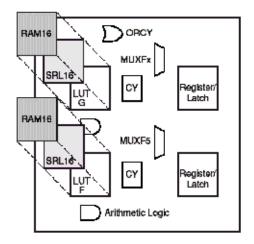

While the multiply-accumulate function supported by a Virtex®-4 DSP block is familiar to a DSP engineer, it is instructive to take a closer look at the Virtex® FPGA family logic slice (shown below), which is the fundamental unit of the logic fabric array.

Each logic slice contains two 4-input lookup tables (LUTs), two configurable D-flip flops, multiplexers, dedicated carry logic, and gates used for creating slice-based multipliers. Each LUT can implement an arbitrary 4-input Boolean function. Coupled with dedicated logic for implementing fast carry circuits, the LUTs can also be used to build fast adder/subtractors and multipliers of essentially any word size. In addition to implementing Boolean functions, each LUT can also be configured as a 16x1 bit RAM or as

a shift register (SRL16). An SRL16 shift register is a synchronously clocked 16x1 bit delay line with a dynamically addressable tap point.

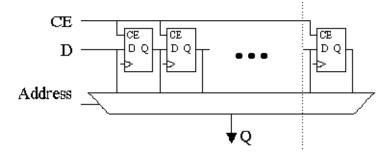

In System Generator, these different memory options are represented with higher-level abstractions. Instead of providing a D-flip flop primitive, System Generator provides a register of arbitrary size. There are two blocks that provide abstractions of arbitrary width, arbitrary depth delay lines that map directly onto the SRL16 configuration. The delay block can be used for pipeline balancing, and can also be used as storage for time-division multiplexed (TDM) data streams. The addressable shift register (ASR) block, with a function depicted in the figure below, provides an arbitrary width, arbitrary depth tapped delay line. This block is of particular interest to the DSP engineer, since it can be used to implement tapped delay lines as well as sweeping through TDM data streams.

Although random access memories can be constructed either out of the BRAM or LUT (RAM16x1) primitives, doing so can require considerable care to ensure most efficient mappings, and considerable clerical attention to detail to correctly assemble the primitives into larger structures. System Generator removes the need for such tasks.

For example, the dual port RAM (DPRAM) block shown in the figure below maps efficiently onto as many BRAM or RAM16x1 components on the device as are necessary to implement the desired memory. As can be seen from the mask dialog box for the DPRAM, the interface allows you to specify a type of memory (BRAM or RAM16x1), depth (data

😝 Dual Port RAM (Xilinx Dual Port Random Access Me... 🗖 🗖 🗙 Basic Advanced Implementation 16 Depth Initial value vector sin(pi\*(0:15)/16) Memory Type: C Distributed memory

Block RAM addra Initial value for port A output register 0 dina Initial value for port B output register 0 wea Optional Ports addrb Provide synchronous reset port for port A output register в dinb Provide synchronous reset port for port B output register ne b Dual Port RAM Provide enable port for port A Provide enable port for port E Latency 1 OK Cancel Help Apply

width is inferred from the Simulink signal driving a particular input port), initial memory contents, and other characteristics.

In general, System Generator maps abstractions onto device primitives efficiently, freeing you from worrying about interconnections between the primitives. System Generator employs libraries of intellectual property (IP) when appropriate to provide efficient implementations of functions in the block libraries. In this way, you don't always have to have detailed knowledge of the underlying FPGA details. However, when it makes sense to implement an algorithm using basic functions (e.g., adder, register, memory), System Generator allows you to exploit your FPGA knowledge while reducing the clerical tasks of managing all signals explicitly.

System Generator library blocks and the mapping from Simulink to hardware are described in detail in subsequent topics of this documentation. There is a wealth of detailed information about FPGAs that can be found online at <a href="http://support.xilinx.com">http://support.xilinx.com</a>, including data books, application notes, white papers, and technical articles.

#### Note to the DSP Engineer

System Generator extends Simulink to enable hardware design, providing high-level abstractions that can be automatically compiled into an FPGA. Although the arithmetic abstractions are suitable to Simulink (discrete time and space dynamical system simulation), System Generator also provides access to features in the underlying FPGA.

The more you know about a hardware realization (e.g., how to exploit parallelism and pipelining), the better the implementation you'll obtain. Using IP cores makes it possible to have efficient FPGA designs that include complex functions like FFTs. System Generator also makes it possible to refine a model to more accurately fit the application.

Scattered throughout the System Generator documentation are notes that explain ways in which system parameters can be used to exploit hardware capabilities.

## Note to the Hardware Engineer

System Generator does not replace hardware description language (HDL)-based design, but does makes it possible to focus your attention only on the critical parts. By analogy, most DSP programmers do not program exclusively in assembler; they start in a higher-level language like C, and write assembly code only where it is required to meet performance requirements.

A good rule of thumb is this: in the parts of the design where you must manage internal hardware clocks (e.g., using the DDR or phased clocking), you should implement using HDL. The less critical portions of the design can be implemented in System Generator, and then the HDL and System Generator portions can be connected. Usually, most portions of a signal processing system do not need this level of control, except at external interfaces. System Generator provides mechanisms to import HDL code into a design (see Importing HDL Modules) that are of particular interest to the HDL designer.

Another aspect of System Generator that is of interest to the engineer who designs using HDL is its ability to automatically generate an HDL testbench, including test vectors. This aspect is described in the topic HDL Testbench.

Finally, the hardware co-simulation interfaces described in the topic Using Hardware Co-Simulation allow you to run a design in hardware under the control of Simulink, bringing the full power of MATLAB and Simulink to bear for data analysis and visualization.

## **Design Flows using System Generator**

System Generator can be useful in many settings. Sometimes you may want to explore an algorithm without translating the design into hardware. Other times you might plan to use a System Generator design as part of something bigger. A third possibility is that a System Generator design is complete in its own right, and is to be used in FPGA hardware. This topic describes all three possibilities.

## Algorithm Exploration

System Generator is particularly useful for algorithm exploration, design prototyping, and model analysis. When these are the goals, you can use the tool to flesh out an algorithm in order to get a feel for the design problems that are likely to be faced, and perhaps to estimate the cost and performance of an implementation in hardware. The work is preparatory, and there is little need to translate the design into hardware.

In this setting, you assemble key portions of the design without worrying about fine points or detailed implementation. Simulink blocks and MATLAB M-code provide stimuli for simulations, and for analyzing results. Resource estimation gives a rough idea of the cost of the design in hardware. Experiments using hardware generation can suggest the hardware speeds that are possible.

Once a promising approach has been identified, the design can be fleshed out. System Generator allows refinements to be done in steps, so some portions of the design can be made ready for implementation in hardware, while others remain high-level and abstract. System Generator's facilities for hardware co-simulation are particularly useful when portions of a design are being refined.

## Implementing Part of a Larger Design

Often System Generator is used to implement a portion of a larger design. For example, System Generator is a good setting in which to implement data paths and control, but is

less well suited for sophisticated external interfaces that have strict timing requirements. In this case, it may be useful to implement parts of the design using System Generator, implement other parts outside, and then combine the parts into a working whole.

A typical approach to this flow is to create an HDL wrapper that represents the entire design, and to use the System Generator portion as a component. The non-System Generator portions of the design can also be components in the wrapper, or can be instantiated directly in the wrapper.

#### Implementing a Complete Design

Many times, everything needed for a design is available inside System Generator. For such a design, pressing the **Generate** button instructs System Generator to translate the design into HDL, and to write the files needed to process the HDL using downstream tools. The files written include the following:

- HDL that implements the design itself;

- A clock wrapper that encloses the design. This clock wrapper produces the clock and clock enable signals that the design needs.

- A HDL testbench that encloses the clock wrapper. The testbench allows results from Simulink simulations to be compared against ones produced by a logic simulator.

- Project files and scripts that allow various synthesis tools, such as XST and Synplify Pro to operate on System Generator HDL

- Files that allow the System Generator HDL to be used as a project in Project Navigator.

For details concerning the files that System Generator writes, see the topic <u>Compilation</u> <u>Results</u>.

## System-Level Modeling in System Generator

System Generator allows device-specific hardware designs to be constructed directly in a flexible high-level system modeling environment. In a System Generator design, signals are not just bits. They can be signed and unsigned fixed-point numbers, and changes to the design automatically translate into appropriate changes in signal types. Blocks are not just stand-ins for hardware. They respond to their surroundings, automatically adjusting the results they produce and the hardware they become.

System Generator allows designs to be composed from a variety of ingredients. Data flow models, traditional hardware design languages (VHDL, Verilog, and EDIF), and functions derived from the MATLAB programming language, can be used side-by-side, simulated together, and synthesized into working hardware. System Generator simulation results are bit and cycle-accurate. This means results seen in simulation exactly match the results that are seen in hardware. System Generator simulations are considerably faster than those from traditional HDL simulators, and results are easier to analyze.

| System Generator Blocksets           | Describes how System Generator's blocks are organized in libraries, and how the blocks can be parameterized and used.                                                                                                                          |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Types                         | Describes the data types used by System Generator<br>and ways in which data types can be automatically<br>assigned by the tool.                                                                                                                |

| Bit-True and Cycle-True<br>Modeling  | Specifies the relationship between the Simulink-based simulation of a System Generator model and the behavior of the hardware that can be generated from it.                                                                                   |

| Timing and Clocking                  | Describes how clocks are implemented in hardware,<br>and how their implementation is controlled inside<br>System Generator. Explains how System Generator<br>translates a multirate Simulink model into working<br>clock-synchronous hardware. |

| Synchronization Mechanisms           | Describes mechanisms that can be used to<br>synchronize data flow across the data path elements<br>in a high-level System Generator design, and<br>describes how control path functions can be<br>implemented.                                 |

| Block Masks and Parameter<br>Passing | Explains how parameterized systems and subsystems are created in Simulink.                                                                                                                                                                     |

| Resource Estimation                  | Describes how to generate estimates of the hardware needed to implement a System Generator design.                                                                                                                                             |

## System Generator Blocksets

A *Simulink blockset* is a library of blocks that can be connected in the Simulink block editor to create functional models of a dynamical system. For system modeling, System Generator blocksets are used like other Simulink blocksets. The blocks provide abstractions of mathematical, logic, memory, and DSP functions that can be used to build sophisticated signal processing (and other) systems. There are also blocks that provide interfaces to other software tools (e.g., FDATool, ModelSim) as well as the System Generator code generation software.

System Generator blocks are *bit-accurate* and *cycle-accurate*. Bit-accurate blocks produce values in Simulink that match corresponding values produced in hardware; cycle-accurate blocks produce corresponding values at corresponding times.

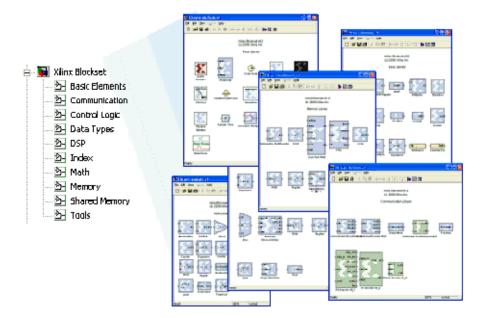

#### Xilinx Blockset

The Xilinx Blockset is a family of libraries that contain basic System Generator blocks. Some blocks are low-level, providing access to device-specific hardware. Others are highlevel, implementing (for example) signal processing and advanced communications algorithms. For convenience, blocks with broad applicability (e.g., the Gateway I/O blocks) are members of several libraries. Every block is contained in the Index library. The libraries are described below.

| Library        | Description                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------------------|

| AXI4           | Blocks with interfaces that conform to the AXI <sup>TM</sup> 4 specification                                     |

| Basic Elements | ElementsStandard building blocks for digital logic                                                               |

| Communication  | Forward error correction and modulator blocks, commonly used in digital communications systems                   |

| Control Logic  | Blocks for control circuitry and state machines                                                                  |

| DSP            | Digital signal processing (DSP) blocks                                                                           |

| Data Types     | Blocks that convert data types (includes gateways)                                                               |

| Floating-Point | Blocks that support the Floating-Point data type                                                                 |

| Index          | Every block in the Xilinx Blockset.                                                                              |

| Math           | Blocks that implement mathematical functions                                                                     |

| Memory         | Blocks that implement and access memories                                                                        |

| Shared Memory  | Blocks that implement and access Xilinx shared memories                                                          |

| Tools          | "Utility" blocks, e.g., code generation (System Generator token),<br>resource estimation, HDL co-simulation, etc |

Note: More information concerning blocks can be found in the topic Xilinx Blockset.

#### Xilinx Reference Blockset

The Xilinx Reference Blockset contains composite System Generator blocks that implement a wide range of functions. Blocks in this blockset are organized by function into different libraries. The libraries are described below.

| Library                                                                 | Description                                  |

|-------------------------------------------------------------------------|----------------------------------------------|

| Communication Blocks commonly used in digital communications systems    |                                              |

| Control Logic LogicBlocks used for control circuitry and state machines |                                              |

| DSP Digital signal processing (DSP) blocks                              |                                              |

| Imaging                                                                 | Image processing blocks                      |

| Math                                                                    | Blocks that implement mathematical functions |

Each block in this blockset is a composite, i.e., is implemented as a masked subsystem, with parameters that configure the block.

You can use blocks from the Reference Blockset libraries as is, or as starting points when constructing designs that have similar characteristics. Each reference block has a description of its implementation and hardware resource requirements. Individual documentation for each block is also provided in the topic Xilinx Reference Blockset.

#### Signal Types

In order to provide bit-accurate simulation of hardware, System Generator blocks operate on Boolean, floating-point, and arbitrary precision fixed-point values. By contrast, the fundamental scalar signal type in Simulink is double precision floating point. The connection between Xilinx blocks and non-Xilinx blocks is provided by *gateway blocks*. The *gateway in* converts a double precision signal into a Xilinx signal, and the *gateway out* converts a Xilinx signal into double precision. Simulink continuous time signals must be sampled by the Gateway In block.

Most Xilinx blocks are polymorphic, i.e., they are able to deduce appropriate output types based on their input types. When *full precision* is specified for a block in its parameters dialog box, System Generator chooses the output type to ensure no precision is lost. Sign extension and zero padding occur automatically as necessary. *User-specified precision* is usually also available. This allows you to set the output type for a block and to specify how quantization and overflow should be handled. Quantization possibilities include unbiased rounding towards plus or minus infinity, depending on sign, or truncation. Overflow options include saturation, truncation, and reporting overflow as an error.

**Note:** System Generator data types can be displayed by selecting **Format > Port Data Types** in Simulink. Displaying data types makes it easy to determine precision throughout a model. If, for example, the type for a port is Fix\_11\_9, then the signal is a two's complement signed 11-bit number

having nine fractional bits. Similarly, if the type is **Ufix\_5\_3**, then the signal is an unsigned 5-bit number having three fractional bits.

In the System Generator portion of a Simulink model, every signal must be sampled. Sample times may be inherited using Simulink's propagation rules, or set explicitly in a block customization dialog box. When there are feedback loops, System Generator is sometimes unable to deduce sample periods and/or signal types, in which case the tool issues an error message. *Assert blocks* must be inserted into loops to address this problem. It is not necessary to add assert blocks at every point in a loop; usually it suffices to add an assert block at one point to "break" the loop.

**Note:** Simulink can display a model by shading blocks and signals that run at different rates with different colors (**Format > Sample Time Colors** in the Simulink pulldown menus). This is often useful in understanding multirate designs.

## Floating-Point Data Type

System Generator blocks found in the Floating-Point library support the floating-point data type.

System Generator uses the Floating-Point Operator v6.0 IP core to leverage the implementation of operations such as addition/subtraction, multiplication, comparisons and data type conversion.

The floating-point data type support is in compliance with IEEE-754 Standard for Floating-Point Arithmetic. Single precision, Double precision and Custom precision floating-point data types are supported for design input, data type display and for data rate and type propagation (RTP) across the supported System Generator blocks.

#### IEEE-754 Standard for Floating-Point Data Type

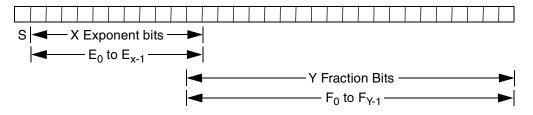

As shown below, floating-point data is represented using one Sign bit (S), X exponent bits and Y fraction bits. The Sign bit is always the most-significant bit (MSB).

According to the IEEE-754 standard, a floating-point value is represented and stored in the normalized form. In the normalized form the exponent value E is a biased/normalized value. The normalized exponent, E, equals the sum of the actual exponent value and the exponent bias. In the normalized form, Y-1 bits are used to store the fraction value. The F<sub>0</sub> fraction bit is always a hidden bit and its value is assumed to be 1.

S represents the value of the sign of the number. If S is 0 then the value is a positive floating-point number; otherwise it is negative. The X bits that follow are used to store the normalized exponent value E and the last Y-1 bits are used to store the fraction/mantissa value in the normalized form.

For the given exponent width, the exponent bias is calculated using the following equation:

Exponent\_bias =  $2^{(X-1)}$  - 1, where X is the exponent bit width.

www.xilinx.com

According to the IEEE standard, a single precision floating-point data is represented using 32 bits. The normalized exponent and fraction/mantissa are allocated 8 and 24 bits, respectively. The exponent bias for single precision is 127. Similarly, a double precision floating-point data is represented using a total of 64 bits where the exponent bit width is 11 and the fraction bit width is 53. The exponent bias value for double precision is 1023.

The normalized floating-point number in the equation form is represented as follows:

Normalized Floating-Point Value =  $(-1)^{S} \times F_0 \cdot F_1 F_2 \dots F_{Y-2} F_{Y-1} \times (2)^{E}$

The actual value of exponent (E\_actual) = E - Exponent\_bias. Considering 1 as the value for the hidden bit  $F_0$  and the E\_actual value, a floating-point number can be calculated as follows:

$FP_Value = (-1)^S \times 1.F_1F_2 \dots F_{Y-2}F_{Y-1} \times (2)^{(E_actual)}$

#### Floating-Point Data Representation in System Generator

The System Generator **Gateway In** block previously only supported the Boolean and Fixed-point data types. As shown below, the **Gateway In** block GUI and underlying mask parameters now support the Floating-point data type as well. You can select either a **Single, Double** or **Custom** precision type after specifying the floating-point data type.

For example, if Exponent width of 9 and Fraction width of 31 is specified then the floatingpoint data value will be stored in total 40 bits where the MSB bit will be used for sign representation, the following 9 bits will be used to store biased exponent value and the 30 LSB bits will be used to store the fractional value.

| ŧ      | Gateway In (Xilinx Gateway In) 💶 🗖 🗙                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d<br>t | Sateway in block. Converts inputs of type Simulink integer, single,<br>louble and fixed-point to Xilinx fixed-point or floating-point data<br>ype.<br>Hardware notes: In hardware these blocks become top level input |

| le     | ports.                                                                                                                                                                                                                |

|        | Basic Implementation                                                                                                                                                                                                  |

|        | Output Type                                                                                                                                                                                                           |

|        | C Boolean C Fixed-point C Floating-point                                                                                                                                                                              |

|        | Arithmetic type Floating-point                                                                                                                                                                                        |

|        | Fixed-point Precision                                                                                                                                                                                                 |

|        | Number of bits 16 Binary point 14                                                                                                                                                                                     |

| 7      | Floating-point Precision                                                                                                                                                                                              |

|        | © Single © Double © Custom                                                                                                                                                                                            |

|        | Exponent width 8 Fraction width 24                                                                                                                                                                                    |

In compliance with the IEEE-754 standard, if **Single** precision is selected then the total bit width is assumed to be 32; 8 bits for the exponent and 24 bits for the fraction. Similarly when **Double** precision is selected, the total bit width is assumed to be 64 bits; 11 bits for the exponent and 53 bits for the fraction part. When **Custom** precision is selected, the **Exponent width** and **Fraction width** fields are activated and you are free to specify values for these fields (8 and 24 are the default values). The total bit width for **Custom** precision data is the summation of the number of exponent bits and the number of fraction bits.

Similar to fraction bit width for **Single** precision and **Double** precision data types the fraction bit width for **Custom** precision data type must include the hidden bit  $F_0$

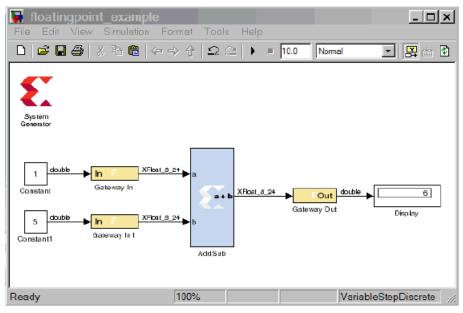

#### Displaying the Data Type on Output Signals

As shown below, after a successful rate and type propagation, the floating-point data type is displayed on the output of each System Generator block. To display the signal data type as shown in the diagram below, you select the pulldown menu item **Format > Port/Signal Displays > Port Data Types**.

A floating-point data type is displayed using the format:

XFloat\_<exponent\_bit\_width>\_<fraction\_bit\_width>. Single and Double precision data types are displayed using the string "XFloat\_8\_24" and "XFloat\_11\_53", respectively.

If for a Custom precision data type the exponent bit width 9 and the fraction bit width 31 are specified, then it will be displayed as "XFloat\_9\_31". A total of 40 bits will be used to store the floating-point data value. Since floating-point data is stored in a normalized form, the fractional value will be stored in 30 bits.

In System Generator the fixed-point data type is displayed using format XFix\_<total\_data\_width>\_<binary\_point\_width>. For example, a fixed-point data type with the data width of 40 and binary point width of 31 is displayed as XFix\_40\_31.

It is necessary to point out that in the fixed-point data type the actual number of bits used to store the fractional value is different from that used for floating-point data type. In the example above, all 31 bits are used to store the fractional bits of the fixed-point data type.

System Generator uses the exponent bit width and the fraction bit width to configure and generate an instance of the Floating-Point Operator core.

#### Rate and Type Propagation

During data rate and type propagation across a System Generator block that supports floating-point data, the following design rules are verified. The appropriate error is issued if one of the following violations is detected.

- 1. If a signal carrying floating-point data is connected to the port of a System Generator block that doesn't support the floating-point data type.

- 2. If the data input (both A and B data inputs, where applicable) and the data output of a System Generator block are not of the same floating-point data type. The DRC check will be made between the two inputs of a block as well as between an input and an output of the block.

If a Custom precision floating-point data type is specified, the exponent bit width and the fraction bit width of the two ports are compared to determine that they are of the same data type.

*Note:* The Convert and Relational blocks are excluded from this check. The Convert block supports Float-to-float data type conversion between two different floating-point data types. The Relational block output is always the Boolean data type because it gives a true or false result for a comparison operation.

3. If the data inputs are of the fixed-point data type and the data output is expected to be floating-point and vice versa.

*Note:* The Convert and Relational blocks are excluded from this check. The Convert block supports Fixed-to-float as well as Float-to-fixed data type conversion. The Relational block output is always the Boolean data type because it gives a true or false result for a comparison operation.

- 4. If User Defined precision is selected for the Output Type of blocks that support the floating-point data type. For example, for blocks such as AddSub, Mult, CMult, and MUX, only Full output precision is supported if the data inputs are of the floating-point data type.

- 5. If the Carry In port or Carry Out port is used for the AddSub block when the operation on a floating-point data type is specified.

- 6. If the Floating-Point Operator IP core gives an error for DRC rules defined for the IP.

#### **AXI Signal Groups**

System Generator blocks found in the AXI4 library contain interfaces that conform to the AXI<sup>TM</sup> 4 specification. Blocks with AXI interfaces are drawn such that ports relating to a particular AXI interface are grouped and colored in similarly. This makes it easier to identify data and control signals pertaining to the same interface. Grouping similar AXI ports together also make it possible to use the Simulink Bus Creator and Simulink Bus Selector blocks to connect groups of signals together. More information on AXI can be found in the section entitled AXI Interface. For more detailed information on the AMBA AXI4 specification, please refer to the Xilinx AMBA AXI4 documents found at the following location: <a href="http://www.xilinx.com/ipcenter/axi4">http://www.xilinx.com/ipcenter/axi4</a>

## Bit-True and Cycle-True Modeling

Simulations in System Generator are *bit-true* and *cycle-true*. To say a simulation is bit-true means that at the boundaries (i.e., interfaces between System Generator blocks and non-System Generator blocks), a value produced in simulation is bit-for-bit identical to the corresponding value produced in hardware. To say a simulation is cycle-true means that at the boundaries, corresponding values are produced at corresponding times. The

boundaries of the design are the points at which System Generator gateway blocks exist. When a design is translated into hardware, Gateway In (respectively, Gateway Out) blocks become top-level input (resp., output) ports.

## Timing and Clocking

#### **Discrete Time Systems**

Designs in System Generator are discrete time systems. In other words, the signals and the blocks that produce them have associated sample rates. A block's sample rate determines how often the block is awoken (allowing its state to be updated). System Generator sets most sample rates automatically. A few blocks, however, set sample rates explicitly or implicitly.

*Note:* For an in-depth explanation of Simulink discrete time systems and sample times, consult the Using Simulink reference manual from the MathWorks, Inc.

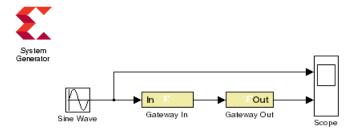

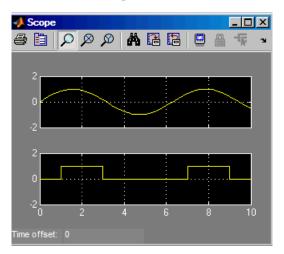

A simple System Generator model illustrates the behavior of discrete time systems. Consider the model shown below. It contains a gateway that is driven by a Simulink source (Sine Wave), and a second gateway that drives a Simulink sink (Scope).

The Gateway In block is configured with a sample period of one second. The Gateway Out block converts the Xilinx fixed-point signal back to a double (so it can analyzed in the Simulink scope), but does not alter sample rates. The scope output below shows the unaltered and sampled versions of the sine wave.

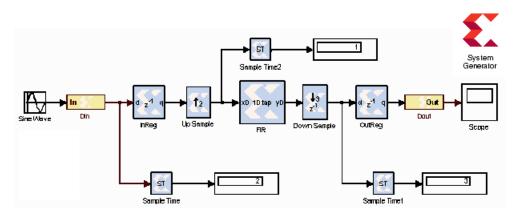

#### **Multirate Models**

System Generator supports *multirate* designs, i.e., designs having signals running at several sample rates. System Generator automatically compiles multirate models into

hardware. This allows multirate designs to be implemented in a way that is both natural and straightforward in Simulink.

#### Rate-Changing Blocks

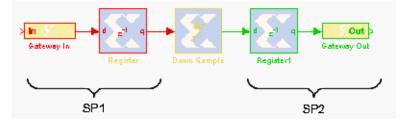

System Generator includes blocks that change sample rates. The most basic rate changers are the Up Sample and Down Sample blocks. As shown in the figure below, these blocks explicitly change the rate of a signal by a fixed multiple that is specified in the block's dialog box.

| Basis   | Implementation                                    |   |

|---------|---------------------------------------------------|---|

| Samplin | grate (rumber of output samples per input sample) | 2 |

Other blocks (e.g., the Parallel To Serial and Serial To Parallel converters) change rates implicitly in a way determined by block parameterization.

Consider the simple multirate example below. This model has two sample periods, SP1 and SP2. The Gateway In dialog box defines the sample period SP1. The Down Sample block causes a rate change in the model, creating a new rate SP2 which is half as fast as SP1.

#### Hardware Oversampling

Some System Generator blocks are oversampled, i.e., their internal processing is done at a rate that is faster than their data rates. In hardware, this means that the block requires more than one clock cycle to process a data sample. In Simulink such blocks do not have an observable effect on sample rates.

One block that can be oversampled is the DAFIR FIR filter. An oversampled DAFIR processes samples serially, thus running at a higher rate, but using less hardware.

Although blocks that are oversampled do not cause an explicit sample rate change in Simulink, System Generator considers the internal block rate along with all other sample rates when generating clocking logic for the hardware implementation. This means that you must consider the internal processing rates of oversampled blocks when you specify the Simulink system period value in the System Generator token dialog box.

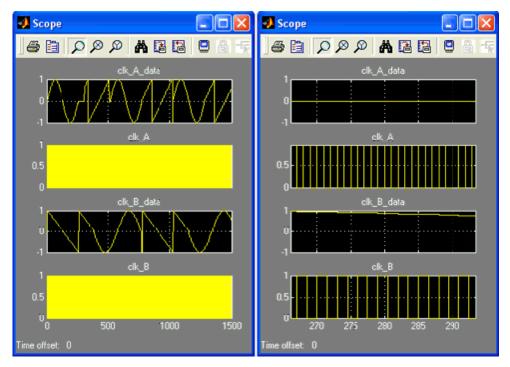

#### Asynchronous Clocking

System Generator focuses on the design of hardware that is synchronous to a single clock. It can, under some circumstances, be used to design systems that contain more than one clock. This is possible provided the design can be partitioned into individual clock domains with the exchange of information between domains being regulated by dual port memories and FIFOs. System Generator fully supports such multi-clock designs, including the ability to simulate them in Simulink and to generate complete hardware descriptions. Details are discussed in the topic <u>Generating Multiple Cycle-True Islands for Distinct</u> <u>Clocks</u>. The remainder of this topic focuses exclusively on the clock-synchronous aspects of System Generator. This discussion is relevant to both single-clock and multiple-clock designs.

#### Synchronous Clocking

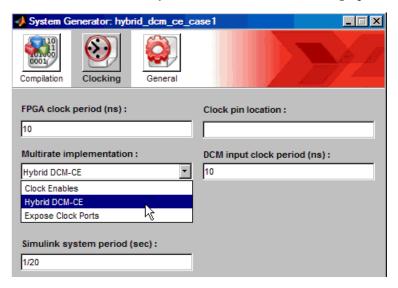

As shown in the figure below, when you use the System Generator token to compile a design into hardware, there are three clocking options for Multirate implementation: (1) Clock Enables (the default), (2) Hybrid DCM-CE, and (3) Expose Clock Ports.

| <b>4</b> System Generator: hybrid_dcm_ce_c | ase1                          |  |  |  |

|--------------------------------------------|-------------------------------|--|--|--|

| Compilation Clocking General               |                               |  |  |  |

| FPGA clock period (ns) :<br>10             | Clock pin location :          |  |  |  |

| Multirate implementation :                 | DCM input clock period (ns) : |  |  |  |

| Hybrid DCM-CE                              | 10                            |  |  |  |

| Clock Enables                              |                               |  |  |  |

| Hybrid DCM-CE                              |                               |  |  |  |

| Expose Clock Ports                         |                               |  |  |  |

| Simulink system period (sec) :             |                               |  |  |  |

#### The Clock Enables Option

When System Generator compiles a model into hardware with the Clock Enable option selected, System Generator preserves the sample rate information of the design in such a way that corresponding portions in hardware run at appropriate rates. In hardware, System Generator generates related rates by using a single clock in conjunction with clock enables, one enable per rate. The period of each clock enable is an integer multiple of the period of the system clock.

Inside Simulink, neither clocks nor clock enables are required as explicit signals in a System Generator design. When System Generator compiles a design into hardware, it uses the sample rates in the design to deduce what clock enables are needed. To do this, it employs two user-specified values from the System Generator token: the Simulink system period and FPGA clock period. These numbers define the scaling factor between time in a Simulink simulation, and time in the actual hardware implementation. The Simulink system period must be the greatest common divisor (gcd) of the sample periods that appear in the model, and the FPGA clock period is the period, in nanoseconds, of the system clock. If p represents the Simulink system period, and c represents the FPGA system clock period, then something that takes kp units of time in Simulink takes k ticks of the system clock (hence kc nanoseconds) in hardware.

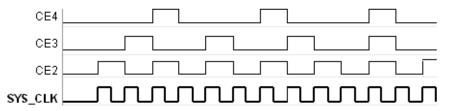

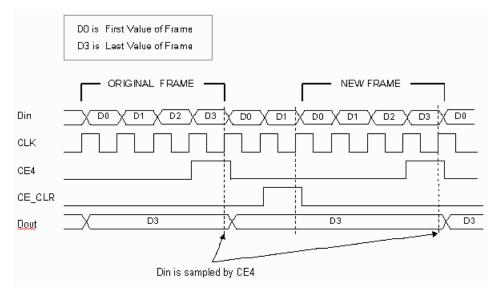

To illustrate this point, consider a model that has three Simulink sample periods 2, 3, and 4. The gcd of these sample periods is 1, and should be specified as such in the Simulink System Period field for the model. Assume the FPGA Clock Period is specified to be 10ns. With this information, the corresponding clock enable periods can be determined in hardware.

In hardware, we refer to the clock enables corresponding to the Simulink sample periods 2, 3, and 4 as CE2, CE3, and CE4, respectively. The relationship of each clock enable period to the system clock period can be determined by dividing the corresponding Simulink sample period by the Simulink System Period value. Thus, the periods for CE2, CE3, and

CE4 equal 2, 3, and 4 system clock periods, respectively. A timing diagram for the example clock enable signals is shown below:

#### The Hybrid DCM-CE Option

If the implementation target is an FPGA with a Digital Clock Manager (DCM), you can choose to drive the clock tree with a DCM. The DCM option is desirable when high fanout on clock enable nets make it difficult to achieve timing closure.

System Generator instantiates the DCM in a top-level HDL clock wrapper and configures the DCM to provide up to three clock ports at different rates for Virtex®-4 and Virtex®-5 and up to two clock ports for Spartan-3A DSP. If the design has more clock ports than the DCM can support, the remaining clocks are supported with the CE (clock enable) configuration. The mapping of rates to the DCM outputs is done according to the following priority scheme:

CLK0 > CLK2x > CLKdv > CLKfx. The DCM supports the higher clock rates first.

A dcm\_reset input port is exposed on the top-level wrapper to allow the external design to reset the DCM after bitstream configuration. A dcm\_locked output port is also exposed to help the external design synchronize the input data with the single clk input port.

**Known Limitations**: The following System Generator blocks are not supported by the Hybrid DCM-CE Option:

- Clock Enable Probe

- Clock Probe

- DAFIR

- Downsample when the Sample option First value of the frame is selected

- FIR Compiler when the core rate is not equal to the input sample rate

- Parallel to Serial- when the Latency option is specified as 0 (zero)

- Time Division De-Multiplexer

- Time Division Multiplexer

- Upsample when the **Copy samples (otherwise zeros are inserted)** option is *not* selected.

#### The Expose Clock Ports Option

When you select this option, System Generator creates a top-level wrapper that exposes a clock port for each rate. You can then manually instantiate a clock generator outside the design to drive the clock ports.

**Known Limitations**: The following System Generator blocks are not supported by the Expose Clock Ports Option:

- Clock Enable Probe

- Clock Probe

- DAFIR

- Downsample when the Sample option First value of the frame is selected

- FIR Compiler when the core rate is not equal to the input sample rate

- Parallel to Serial- when the Latency option is specified as 0 (zero)

- Time Division De-Multiplexer

- Time Division Multiplexer

- Upsample when the **Copy samples (otherwise zeros are inserted)** option is *not* selected.

#### Tutorial Example: Using the Hybrid DCM-CE Option

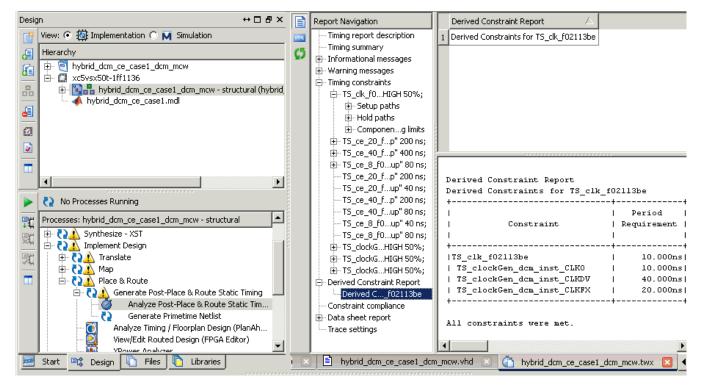

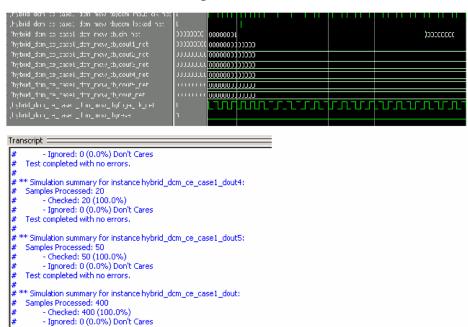

The following step-by-step example will show you how to select the Hybrid DCM-CE option, netlist the HDL design, implement the design in ISE®, simulate the design and examine the files and reports to verify that the DCM is properly instantiated and configured.

The **hybrid\_dcm\_ce\_case1.mdl** design example is located at the following pathname ...<ISE\_Design\_Suite\_tree>/sysgen>/examples/clocking\_options/hybrid\_dcm\_ce\_case1/hybrid\_dcm\_ce\_case1.mdl

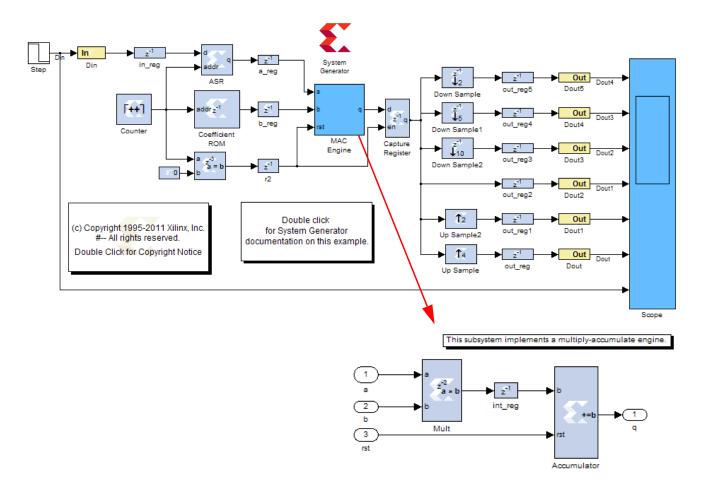

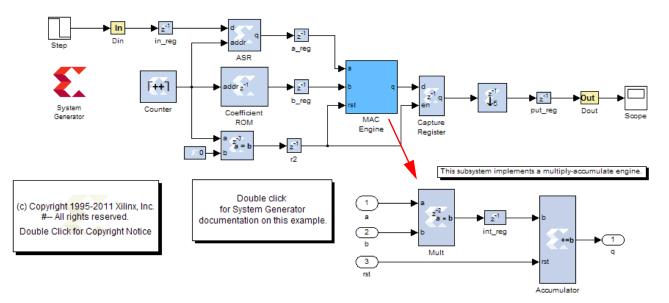

- 1. Open the model in MATLAB and observe the following blocks:

- Addressable Shift Register (ASR): used to implement the input delay buffer. The address port runs n times faster than the data port, where n is the number of the filter taps (5 for this example)

- Coefficient ROM: used to store the filter coefficients

- Counter: used to generate addresses for the ROM and ASR

- **Comparator**: used to generate the reset and enable signals

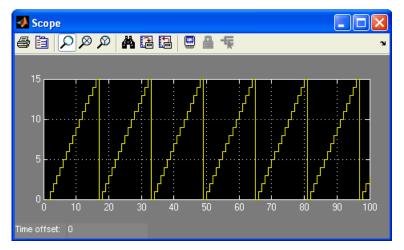

• MAC Engine: used as a Multiply-Accumulator operator for the filter

## Demonstration on Using the Hybrid DCM-CE Clocking Option

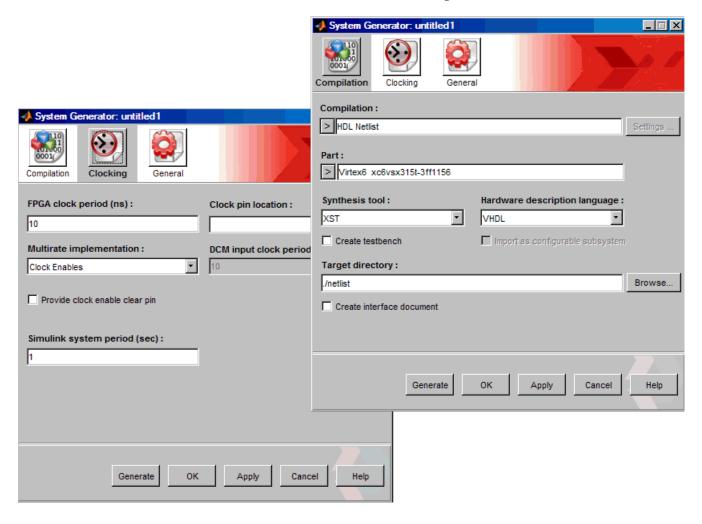

2. Double-click on the System Generator token to bring up the following dialog box:

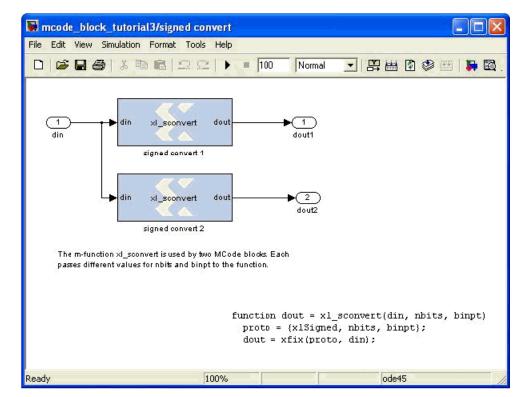

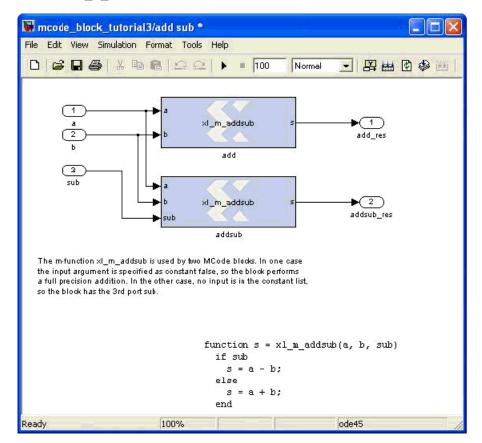

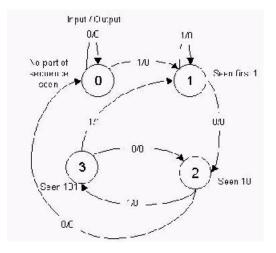

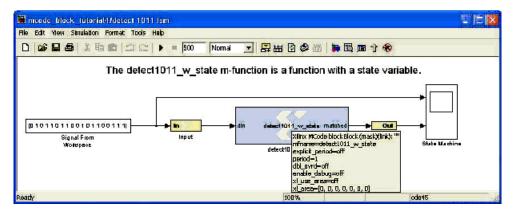

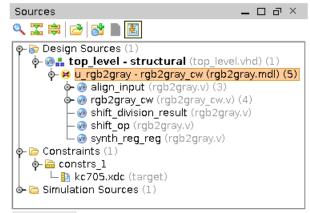

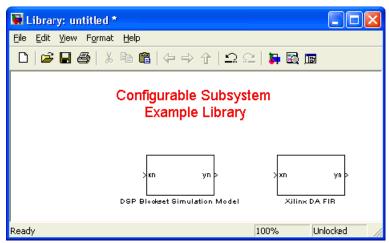

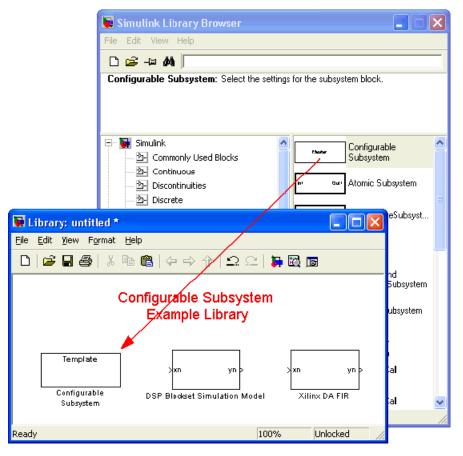

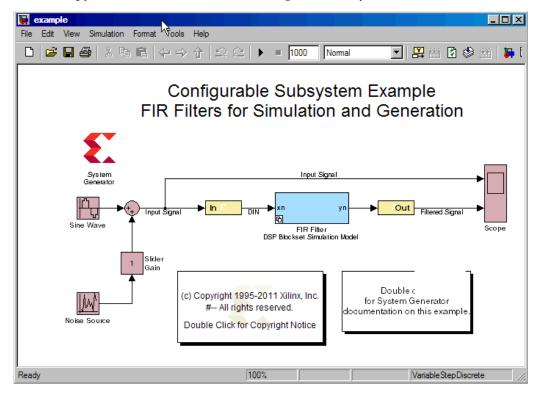

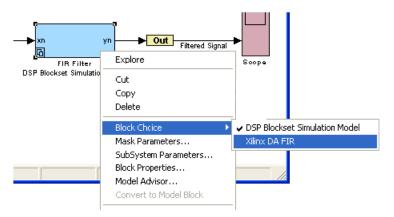

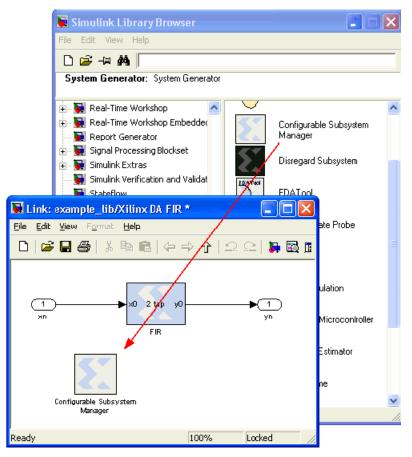

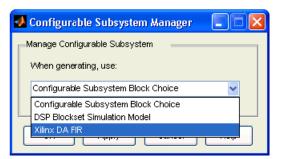

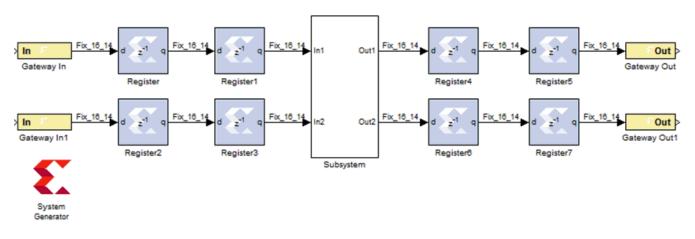

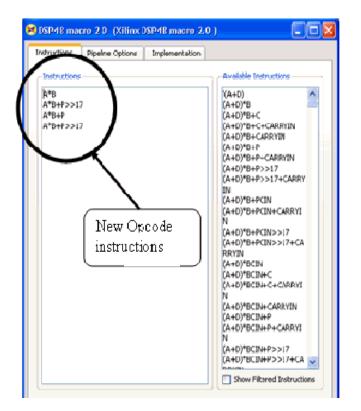

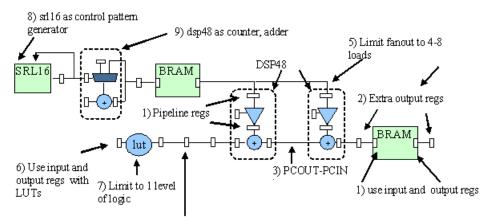

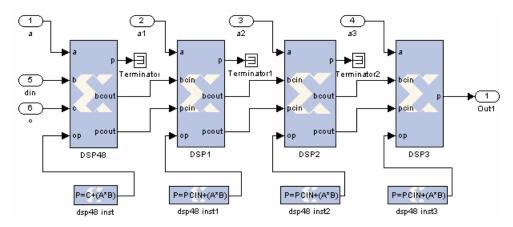

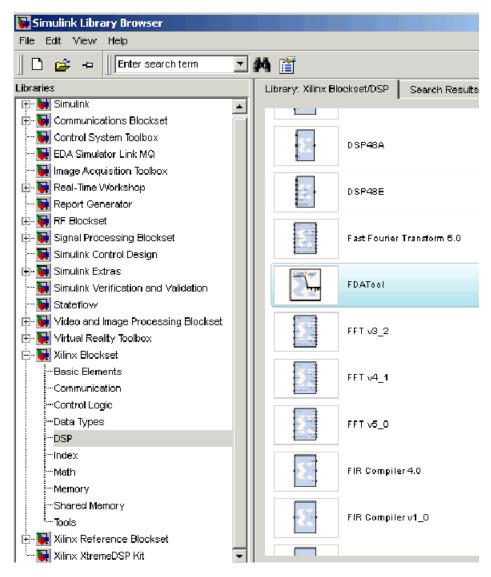

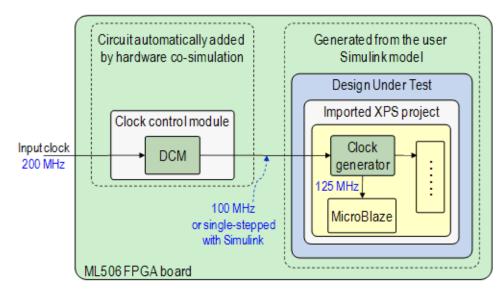

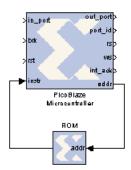

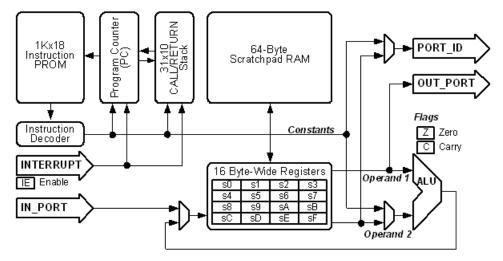

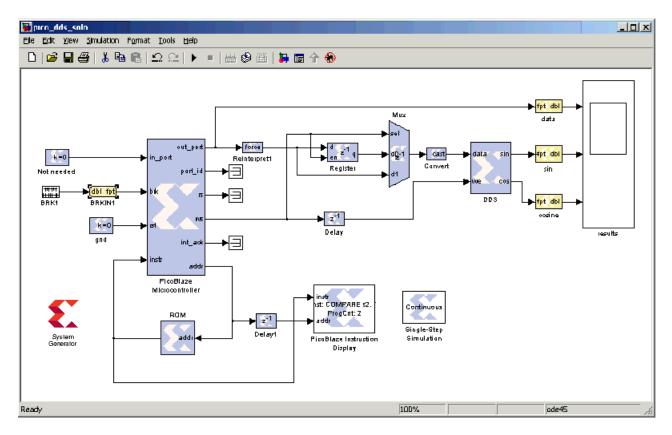

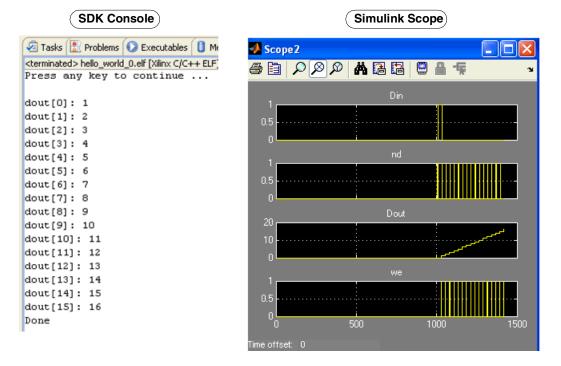

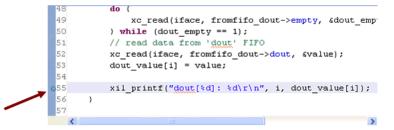

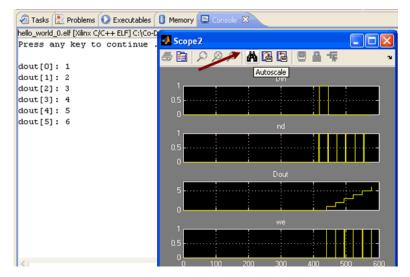

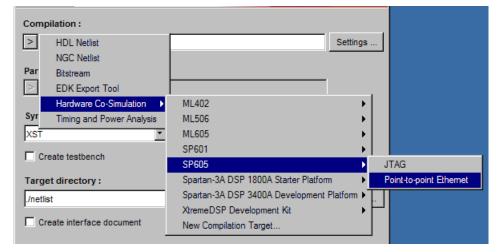

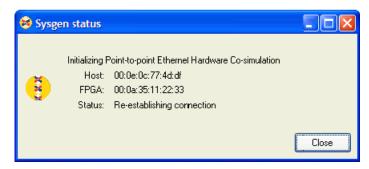

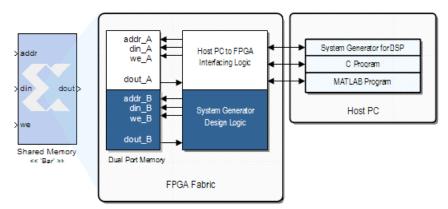

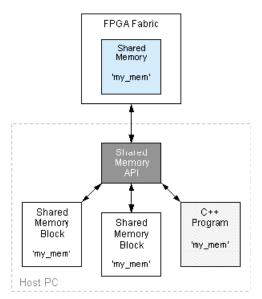

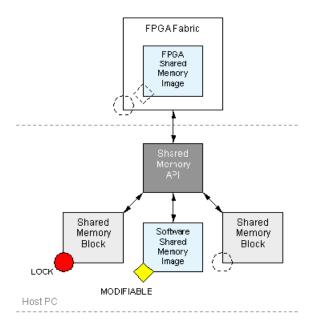

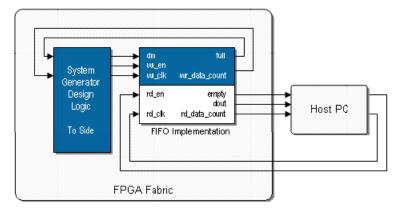

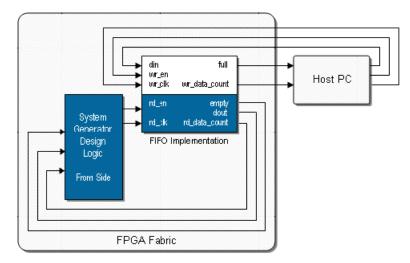

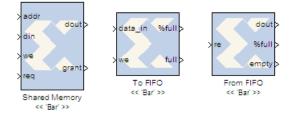

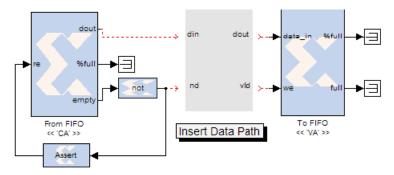

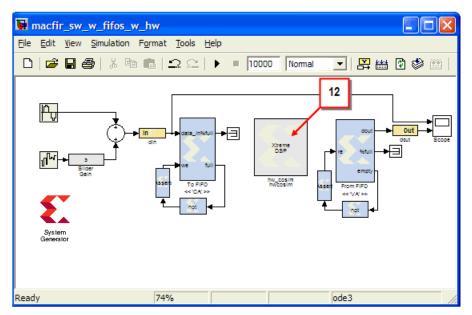

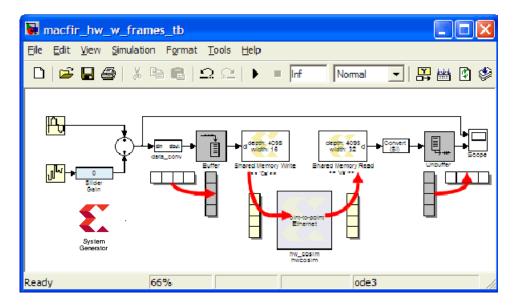

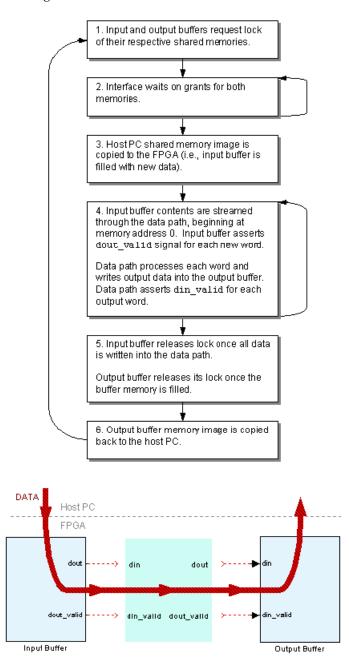

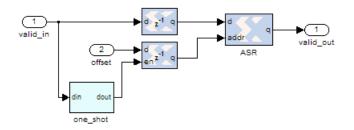

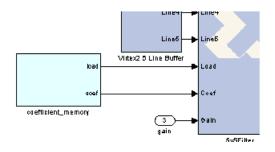

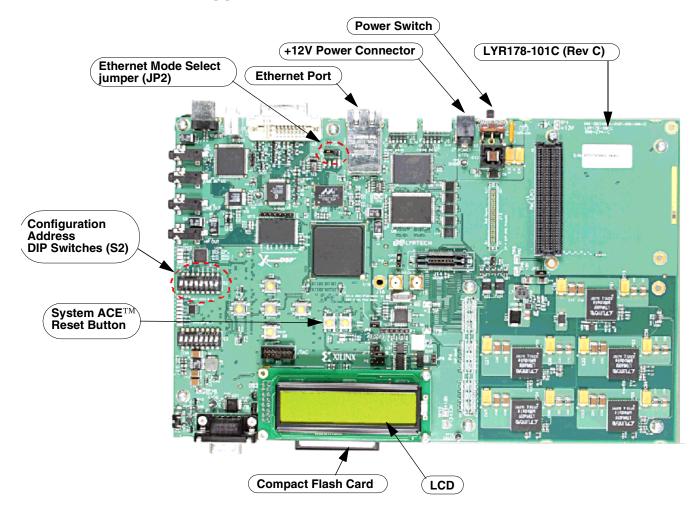

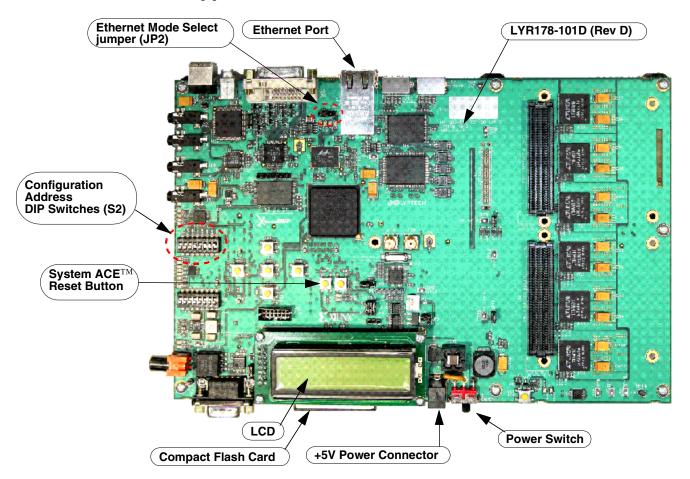

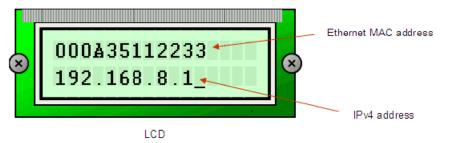

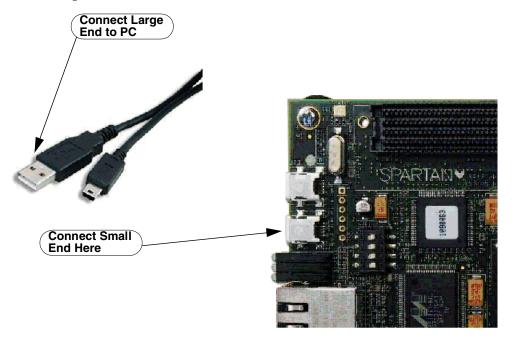

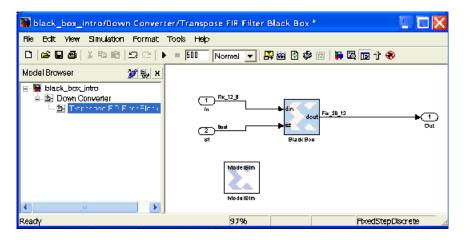

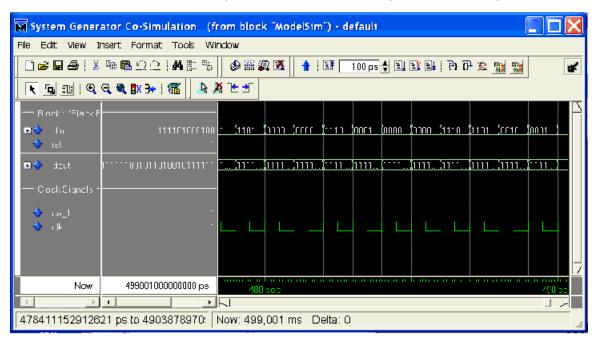

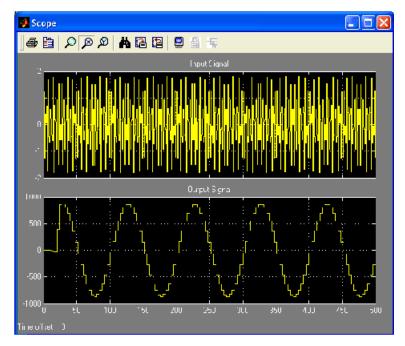

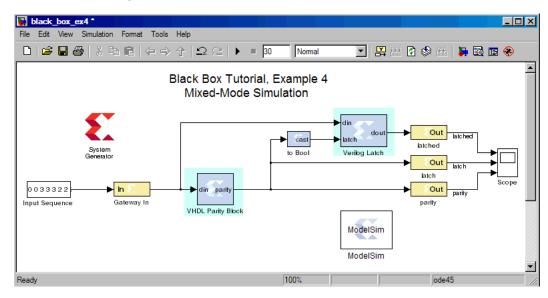

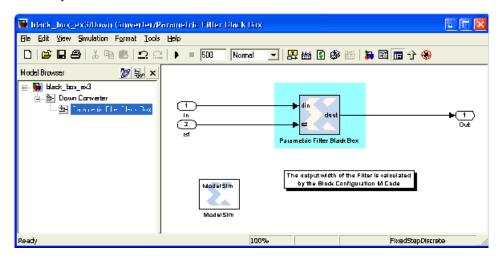

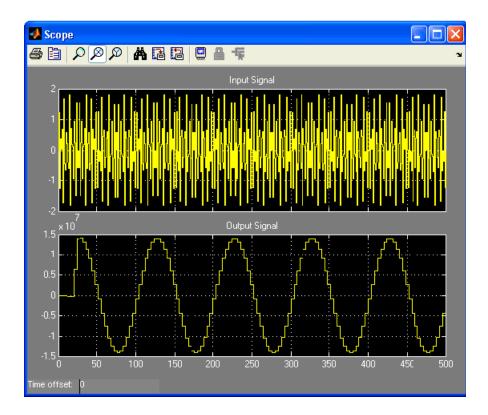

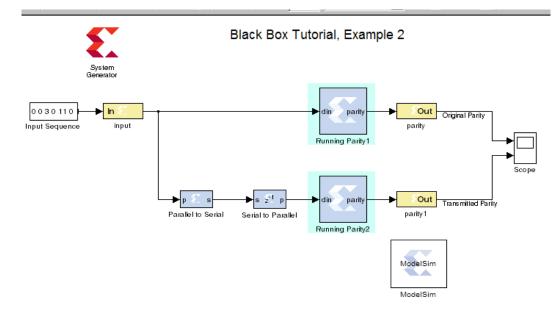

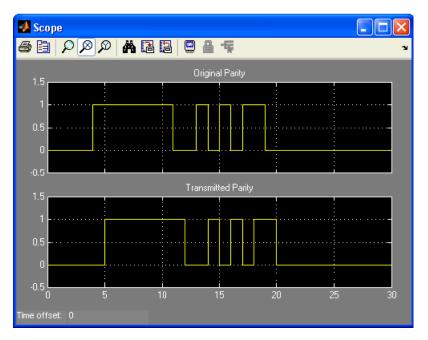

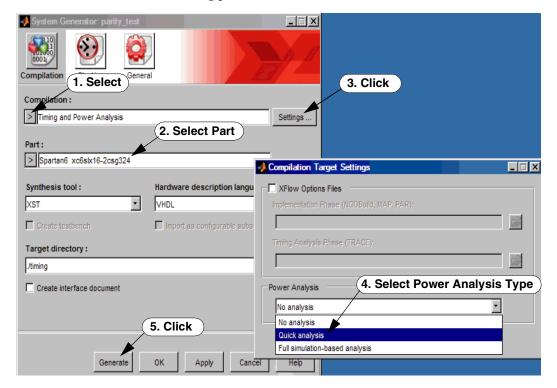

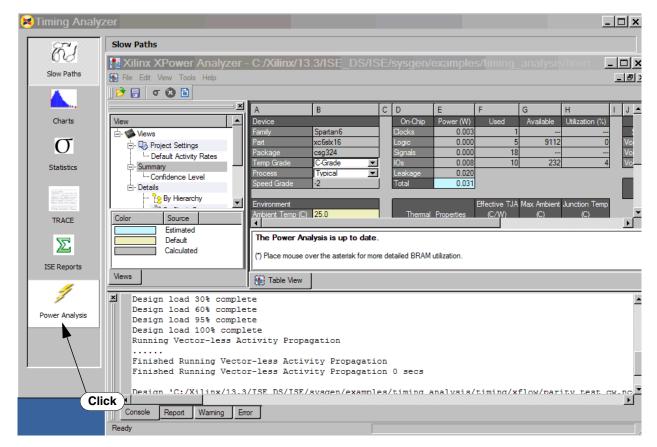

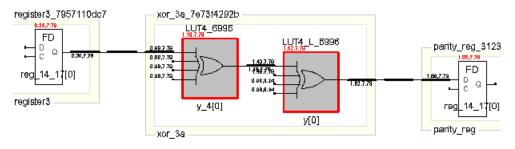

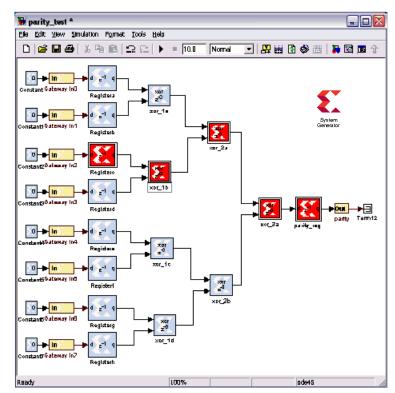

As shown, click on the the **Clocking** tab, select **Hybrid DCM-CE**, then click **Generate**. After a few moments, a sub-directory named **hdl\_netlist\_dcm** is created in the current working directory containing the generated files.