# LogiCORE IP Aurora 64B/66B v8.1

# Product Guide for Vivado Design Suite

PG074 June 19, 2013

# **Table of Contents**

## **IP Facts**

| Chapter 1: Overview                                                                      |    |

|------------------------------------------------------------------------------------------|----|

| Feature Summary                                                                          | 6  |

| Applications                                                                             | 7  |

| Unsupported Features                                                                     | 7  |

| Licensing and Ordering Information                                                       | 8  |

| Chapter 2: Product Specification                                                         |    |

| Standards                                                                                | LC |

| Performance                                                                              | LC |

| Resource Utilization                                                                     | 12 |

| Port Descriptions                                                                        | 13 |

| Detailed Functional Description                                                          | 25 |

| Chapter 3: Designing with the Core                                                       |    |

| General Design Guidelines                                                                | 52 |

| Clocking                                                                                 | 53 |

| Core Features                                                                            | 58 |

| Chapter 4: Customizing and Generating the Core                                           |    |

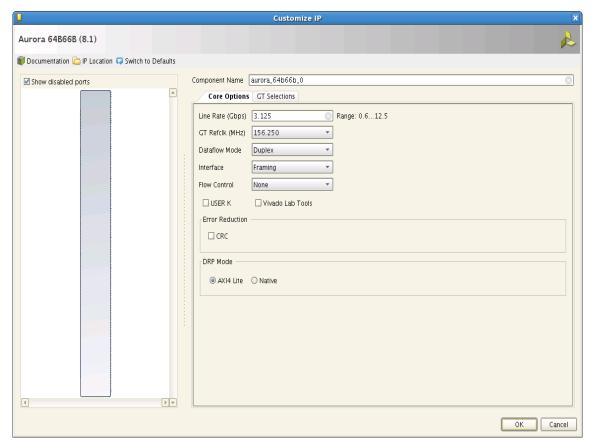

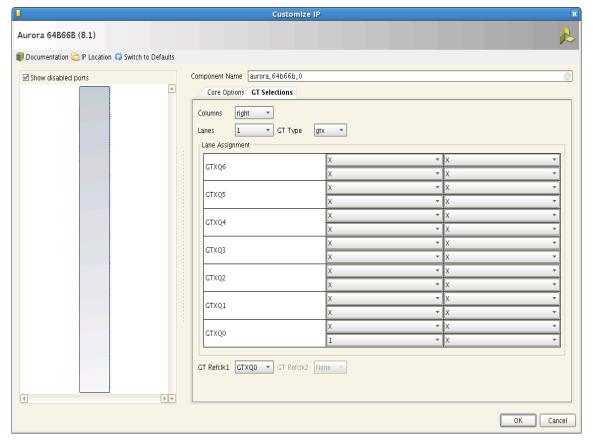

| Vivado Integrated Design Environment (IDE)                                               | 5( |

| Output Generation6                                                                       | 56 |

| <pre><pre><pre><pre><pre><pre><pre><pre></pre></pre></pre></pre></pre></pre></pre></pre> | 57 |

| Chapter 5: Constraining the Core                                                         |    |

| Device, Package, and Speed Grade Selections                                              | 71 |

| Clock Frequencies                                                                        | 71 |

| Clock Management                                                                         | 72 |

| Clock Placement                                                                          | 73 |

| Banking                                                                                  | 73 |

| Transceiver Placement                                                                    | 73 |

| I/O Standard and Placement                                                               | 73 |

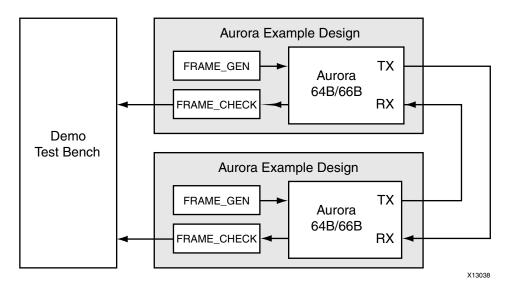

| Chapter 6: Detailed Example Design                                   |

|----------------------------------------------------------------------|

| Directory and File Contents 74                                       |

| Quick Start Example Design 74                                        |

| Detailed Example Design                                              |

| Generating the Core                                                  |

| Implementing the Example Design                                      |

| Appendix A: Verification, Compliance, and Interoperability           |

| Appendix B: Migrating                                                |

| Introduction                                                         |

| Prerequisites 92                                                     |

| Overview of Major Changes 93                                         |

| Block Diagrams94                                                     |

| Signal Changes                                                       |

| Migration Steps 96                                                   |

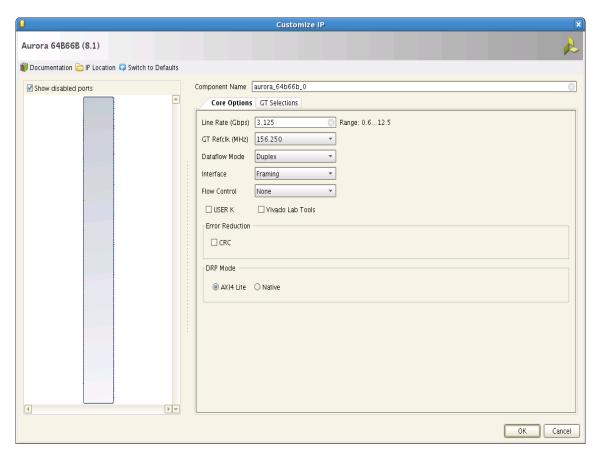

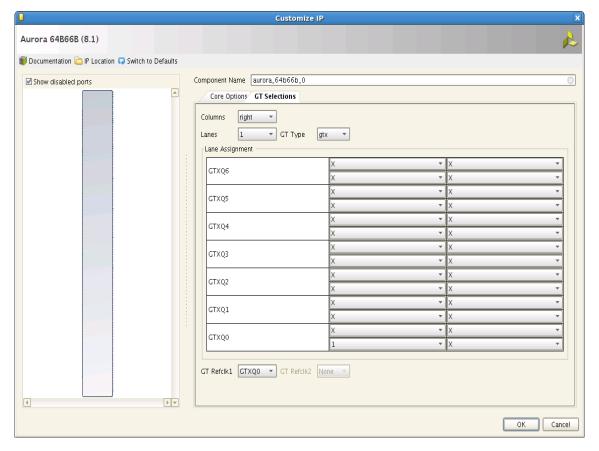

| GUI Changes                                                          |

| Limitations                                                          |

| Appendix C: Debugging                                                |

| Finding Help on Xilinx.com 99                                        |

| Debug Tools                                                          |

| Simulation Debug                                                     |

| Hardware Debug 104                                                   |

| Interface Debug                                                      |

| Appendix D: Generating a GT Wrapper File from the Transceiver Wizard |

| Appendix E: Additional Resources                                     |

| Xilinx Resources                                                     |

| References                                                           |

| Revision History                                                     |

| Notice of Disclaimer                                                 |

# Introduction

Aurora 64B/66B is a scalable, lightweight, high data rate, link-layer protocol for high-speed serial communication. The protocol is open and can be implemented using Xilinx FPGA technology.

The Vivado® Design Suite produces source code for Aurora 64B/66B cores. The cores can be simplex or full-duplex, and feature one of two simple user interfaces and optional flow control.

## **Features**

- Aurora 64B/66B cores supported on the Vivado Design Suite

- General-purpose data channels with throughput range from 600 Mb/s to over 200 Gb/s

- Supports up to 16 GTX transceivers or 16 Virtex®-7 FPGA GTH transceivers

- Aurora 64B/66B protocol specification v1.2 compliant (64B/66B encoding)

- Low resource cost with very low (3%) transmission overhead

- Easy-to-use AXI4-Stream (framing) or streaming interface and optional flow control

- Automatically initializes and maintains the channel

- Full-duplex or simplex operation

|                                              | LogiCORE IP Facts Table                            |  |  |  |  |

|----------------------------------------------|----------------------------------------------------|--|--|--|--|

|                                              | Core Specifics                                     |  |  |  |  |

| Supported<br>Device<br>Family <sup>(1)</sup> | Virtex-7 <sup>(2)</sup> , Kintex®-7 <sup>(2)</sup> |  |  |  |  |

| Supported<br>User Interfaces                 | AXI4-Stream                                        |  |  |  |  |

| Resources <sup>(3)</sup>                     | See Table 2-1 and Table 2-2.                       |  |  |  |  |

|                                              | Provided with Core                                 |  |  |  |  |

| Design Files                                 | RTL                                                |  |  |  |  |

| Example<br>Design                            | Verilog and VHDL                                   |  |  |  |  |

| Test Bench                                   | Verilog and VHDL                                   |  |  |  |  |

| Constraints<br>File                          | Xilinx Design Constraints (XDC)                    |  |  |  |  |

| Simulation<br>Model                          | Not Provided                                       |  |  |  |  |

| Supported<br>S/W Driver                      | N/A                                                |  |  |  |  |

|                                              | Tested Design Flows <sup>(4)</sup>                 |  |  |  |  |

| Design Entry                                 | Vivado Design Suite                                |  |  |  |  |

| Simulation                                   | Mentor Graphics Questa® SIM<br>Vivado Simulator    |  |  |  |  |

| Synthesis                                    | Vivado Synthesis                                   |  |  |  |  |

|                                              | Support                                            |  |  |  |  |

| Provided by Xilinx @ www.xilinx.com/support  |                                                    |  |  |  |  |

#### **Notes:**

- For a complete list of supported devices, see Vivado IP catalog.

- 2. For more information, see 7 Series FPGAs Overview (DS180).

- For more complete performance data, see Performance, page 10.

- 4. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

**Note:** This core release supports only Virtex®-7 and Kintex®-7 devices.

This product guide describes the function and operation of the LogiCORE™ IP Aurora 64B/66B v8.1 core and provides information about designing, customizing, and implementing the core.

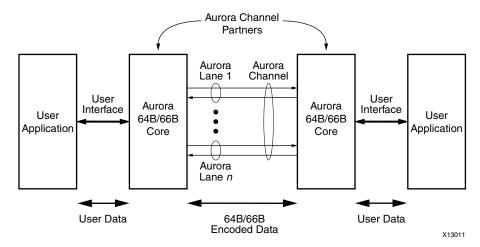

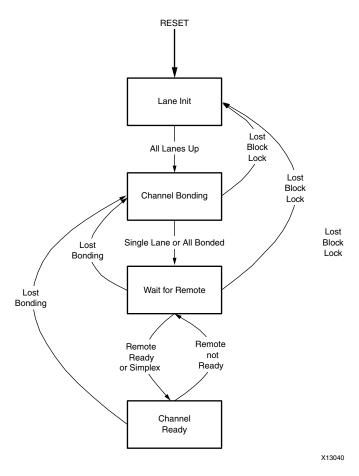

Aurora 64B/66B is a lightweight, serial communications protocol for multi-gigabit links (Figure 1-1). It is used to transfer data between devices using one or many GTX/GTH transceivers. Connections can be *full-duplex* (data in both directions) or *simplex* (data in either one of the directions).

The LogiCORE IP Aurora 64B/66B core supports the AMBA® protocol AXI4-Stream user interface. It implements the Aurora 64B/66B protocol using the high-speed serial GTX or GTH transceivers in applicable Virtex-7 and Kintex-7 devices. The core can use up to 16 Kintex-7 or Virtex-7 FPGA GTX or GTH transceivers running at any supported line rate to provide a low-cost, general-purpose, data channel with throughput from 600 Mb/s to over 200 Gb/s.

Aurora 64B/66B cores are verified for protocol compliance using an array of automated simulation tests.

Figure 1-1: Aurora 64B/66B Channel Overview

Aurora 64B/66B cores automatically initialize a channel when they are connected to an Aurora 64B/66B channel partner. After initialization, applications can pass data across the channel as *frames* or *streams* of data. Aurora 64B/66B *frames* can be of any size, and can be interrupted any time by high priority requests. Gaps between valid data bytes are automatically filled with *idles* to maintain lock and prevent excessive electromagnetic interference. *Flow control* is optional in Aurora 64B/66B, and can be used to throttle the link partner transmit data rate, or to send brief, high-priority messages through the channel.

Streams are implemented in Aurora 64B/66B as a single, unending frame. Whenever data is not being transmitted, idles are transmitted to keep the link alive. Excessive bit errors, disconnections, or equipment failures cause the core to reset and attempt to initialize a new channel. The Aurora 64B/66B core can support a maximum of two symbols skew in the receive of a multi-lane channel. The Aurora 64B/66B protocol uses 64B/66B encoding. The 64B/66B encoding offers improved performance because of its very low (3%) transmission overhead, compared to 25% overhead for 8B/10B encoding.

**RECOMMENDED:** Although the Aurora 64B/66B core is a fully-verified solution, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, previous experience building high-performance, pipelined FPGA designs using Xilinx implementation tools and user constraints files Xilinx Design Constraints (XDC) is recommended.

Read Status, Control, and the Transceiver Interface in Chapter 2 carefully.

Consult the PCB design requirements information in the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476)

Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Feature Summary**

The LogiCORE IP Aurora 64B/66B core implements the Aurora 64B/66B protocol using the high-speed serial transceivers on the Virtex-7/Kintex-7 FPGAs. The core supports the AMBA® protocol AXI4-Stream user interface.

The Aurora 64B/66B core is based on the *Aurora 64B/66B Protocol Specification* (SP011) and uses the high-speed serial GTX or GTH transceivers in applicable Virtex-7 and Kintex-7 FPGAs. The core is delivered as open-source code and supports Verilog and VHDL design environments. Each core comes with an example design and supporting modules.

# **Applications**

Aurora 64B/66B cores can be used in a wide variety of applications because of their low resource cost, scalable throughput, and flexible data interface. Examples of Aurora 64B/66B core applications include:

- Chip-to-chip links: Replacing parallel connections between chips with high-speed serial connections can significantly reduce the number of traces and layers required on a PCB. The Aurora 64B/66B core provides the logic needed to use GTX/GTH transceivers, with minimal FPGA resource cost.

- Board-to-board and backplane links: Aurora 64B/66B uses standard 64B/66B encoding, which is the preferred encoding scheme for 10-Gigabit Ethernet making it compatible with many existing hardware standards for cables and backplanes. Aurora 64B/66B can be scaled, both in line rate and channel width, to allow inexpensive legacy hardware to be used in new, high-performance systems.

- **Simplex connections (unidirectional):** In some applications there is no need for a high-speed back channel. The Aurora 64B/66B simplex protocol provides several ways to perform unidirectional channel initialization, making it possible to use the GTX/GTH transceivers when a back channel is not available, and to reduce costs due to unused full-duplex resources.

- ASIC applications: Aurora 64B/66B is not limited to FPGAs, and can be used to create scalable, high-performance links between programmable logic and high-performance ASICs. The simplicity of the Aurora 64B/66B protocol leads to low resource costs in ASICs as well as in FPGAs, and design resources like the Aurora 64B/66B bus functional model (BFM) with automated compliance testing make it easy to get an Aurora 64B/66B connection up and running. Contact Xilinx Sales or auroramkt@xilinx.com for information on licensing Aurora for ASIC applications.

# **Unsupported Features**

There are no unsupported features in Aurora 64B/66B.

# **Licensing and Ordering Information**

This Xilinx LogiCORE IP module is provided at no additional cost with the Xilinx Vivado® Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

To use the Aurora 64B/66B core with an application specific integrated circuit (ASIC), a separate paid license agreement is required under the terms of the <u>Xilinx Core License Agreement</u>. Contact Aurora Marketing at auroramkt@xilinx.com for more information.

For more information, visit the <u>Aurora 64B/66B product page</u>.

# **Product Specification**

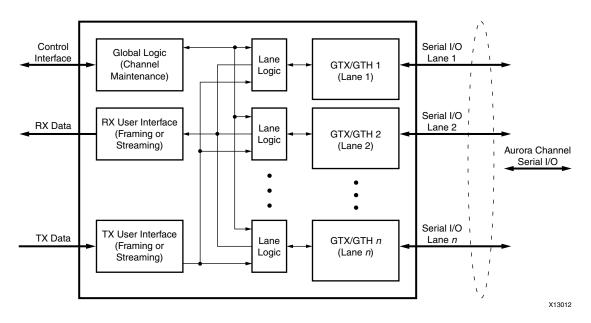

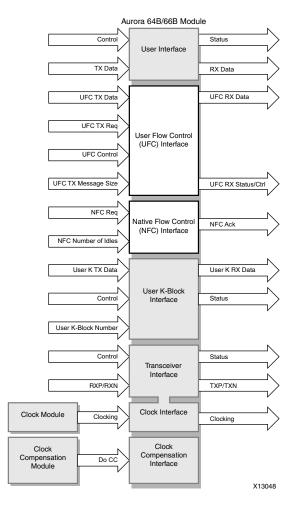

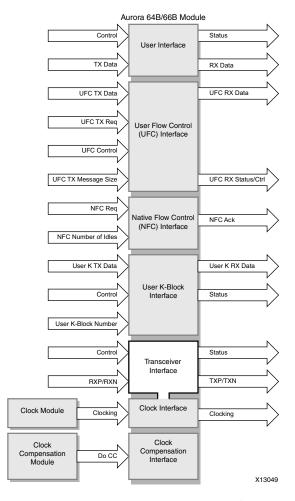

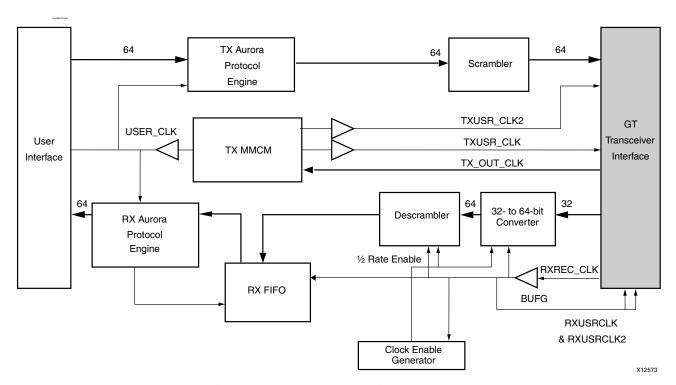

Figure 2-1 shows a block diagram of the implementation of the Aurora 64B/66B core.

Figure 2-1: Aurora 64B/66B Core Block Diagram

The major functional modules of the Aurora 64B/66B core are:

- **Lane logic:** Each GTX/GTH transceiver is driven by an instance of the lane logic module, which initializes each individual GTX/GTH transceiver and handles the encoding and decoding of control characters and error detection.

- **Global logic:** The global logic module in the Aurora 64B/66B core performs the channel bonding for channel initialization. While the channel is operating, it keeps track of the Not Ready idle characters defined by the Aurora 64B/66B protocol and monitors all the lane logic modules for errors.

- **RX user interface:** The receive (RX) user interface moves data from the channel to the application. Streaming data is presented using a simple stream interface equipped with a data bus and *valid* and *ready* signals for flow control operation. Frames are presented using a standard AXI4-Stream interface. This module also performs flow control functions.

• **TX user interface:** The transmit (TX) user interface moves data from the application to the channel. A stream interface with valid and ready signals are used for streaming data. A standard AXI4-Stream interface is used for data frames. The module also performs flow control TX functions. The module has an interface for controlling clock compensation (the periodic transmission of special characters to prevent errors due to small clock frequency differences between connected Aurora 64B/66B cores). Normally, this interface is driven by a standard clock compensation manager module provided with the Aurora 64B/66B core, but it can be turned off, or driven by custom logic to accommodate special needs.

# **Standards**

The Aurora 64B/66B core is compliant with the *Aurora 64B/66B Protocol Specification v1.2* (SP011).

# **Performance**

This section details the performance information for various core configurations.

## **Maximum Frequencies**

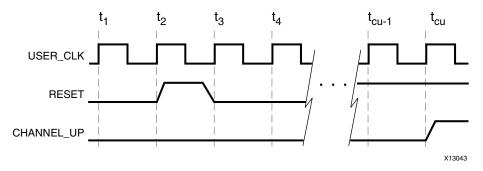

The Aurora 64B/66B cores listed in Table 2-1, page 12 and Table 2-2, page 12 were run at 156.25 MHz in devices with speed grades ranging from -1 to -3.

## Latency

Latency through an Aurora 64B/66B core is caused by pipeline delays through the protocol engine (PE) and through the GTX/GTH transceivers. The PE pipeline delay increases as the AXI4-Stream interface width increases. The GTX/GTH transceivers delays are fixed per the features of the GTX/GTH transceivers.

This section outlines expected latency for the Aurora 64B/66B core AXI4-Stream user interface in terms of USER\_CLK cycles for Virtex®-7/Kintex™-7 FPGA GTX/GTH transceiver based designs. For the purposes of illustrating latency, the Aurora 64B/66B modules are partitioned into GTX/GTH transceivers logic and protocol engine (PE) logic implemented in the FPGA logic.

Figure 2-2 illustrates the latency of the frame path.

Figure 2-2: Latency of the Frame Path

**Note:** Figure 2-2 does not include the latency incurred due to the length of the serial connection between each side of the Aurora 64B/66B channel.

Maximum latency for designs using GTX transceivers from first assertion on S\_AXI\_TX\_TVALID to M\_AXI\_RX\_TVALID is approximately 37 USER\_CLK cycles in simulation.

Maximum latency for designs using GTH transceivers from first assertion on S\_AXI\_TX\_TVALID to M\_AXI\_RX\_TVALID is approximately 45 USER\_CLK cycles in simulation.

The pipeline delays are designed to maintain the clock speed.

# **Throughput**

Aurora 64B/66B core throughput depends on the number of the transceivers and the target line rate of the transceivers selected. Throughput varies from 0.58 Gb/s to 203.3 Gb/s for a single-lane design to a 16-lane design, respectively. The throughput was calculated using 3% overhead of Aurora 64B/66B protocol encoding and 0.6 Gb/s to 13.1 Gb/s line rate range.

# **Resource Utilization**

Table 2-1 through Table 2-2 show the number of look-up tables (LUTs) and flip-flops (FFs) used in selected Aurora 64B/66B framing and streaming modules in the Vivado® Design Suite. The Aurora 64B/66B core is also available in configurations not shown in the tables. The tables do not include the additional resource usage for flow controls. Resource utilization in the following tables do not include the additional resource usage for the example design modules, such as FRAME\_GEN and FRAME\_CHECK.

Table 2-1: Virtex-7 Family GTX Transceiver Resource Usage for Streaming

| Virtex-7 Family (GTX Transceiver) |                     |             | Streaming |         |

|-----------------------------------|---------------------|-------------|-----------|---------|

| virtex-7 Family                   | y (GTX Transceiver) | Duplex      | Sim       | plex    |

| Lanes                             | Resource Type       | Full-Duplex | TX-Only   | RX-Only |

| 1                                 | LUTs                | 410         | 190       | 339     |

|                                   | FFs                 | 697         | 229       | 519     |

| 2                                 | LUTs                | 781         | 195       | 698     |

|                                   | FFs                 | 1216        | 229       | 1037    |

| 4                                 | LUTs                | 1450        | 253       | 1301    |

|                                   | FFs                 | 2193        | 231       | 2011    |

| 8                                 | LUTs                | 2736        | 156       | 2606    |

|                                   | FFs                 | 4144        | 235       | 3959    |

| 16                                | LUTs                | 5321        | 164       | 5091    |

|                                   | FFs                 | 8049        | 244       | 7855    |

Table 2-2: Virtex-7 Family GTX Transceiver Resource Usage for Framing

| Virtor 7 Family (CTV Transcolver) |                                   |             | Framing |         |

|-----------------------------------|-----------------------------------|-------------|---------|---------|

| virtex-7 ramily                   | Virtex-7 Family (GTX Transceiver) |             | Sim     | plex    |

| Lanes                             | Resource Type                     | Full-Duplex | TX-Only | RX-Only |

| 1                                 | LUTs                              | 448         | 190     | 345     |

|                                   | FFs                               | 697         | 229     | 519     |

| 2                                 | LUTs                              | 779         | 194     | 708     |

|                                   | FFs                               | 1218        | 229     | 1039    |

| 4                                 | LUTs                              | 1448        | 253     | 1300    |

|                                   | FFs                               | 2196        | 231     | 2014    |

| 8                                 | LUTs                              | 2750        | 148     | 2681    |

|                                   | FFs                               | 4144        | 235     | 3959    |

Table 2-2: Virtex-7 Family GTX Transceiver Resource Usage for Framing (Cont'd)

| Virtex-7 Family (GTX Transceiver) |               |             | Framing |         |

|-----------------------------------|---------------|-------------|---------|---------|

|                                   |               | Duplex      | Sim     | plex    |

| Lanes                             | Resource Type | Full-Duplex | TX-Only | RX-Only |

| 16                                | LUTs          | 5416        | 162     | 5146    |

|                                   | FFs           | 8048        | 244     | 7855    |

# **Port Descriptions**

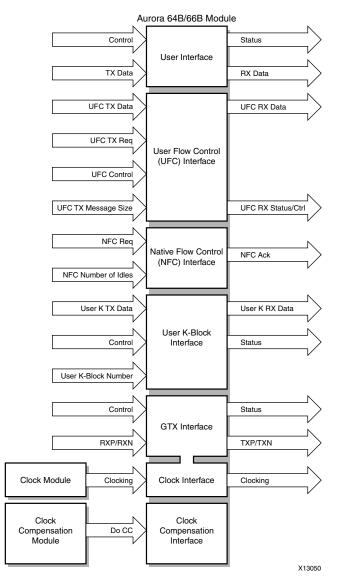

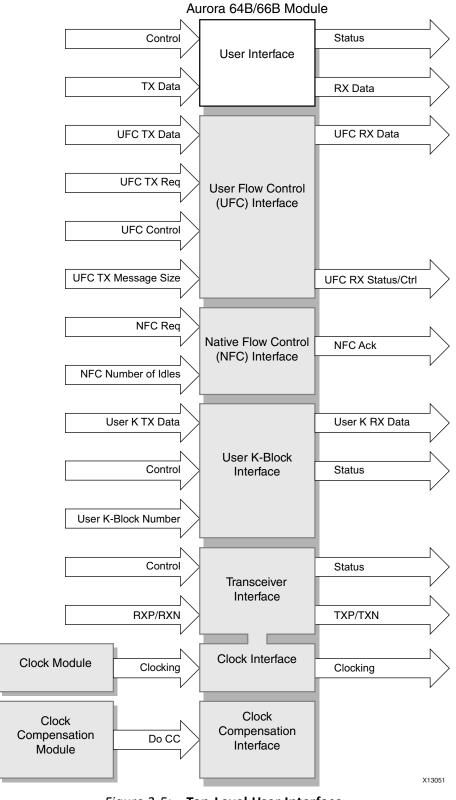

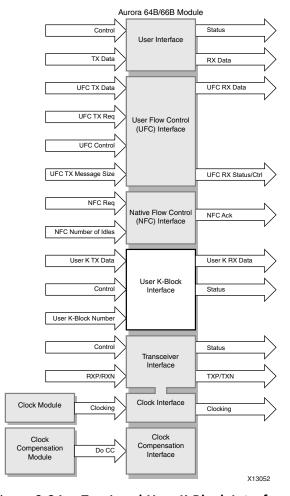

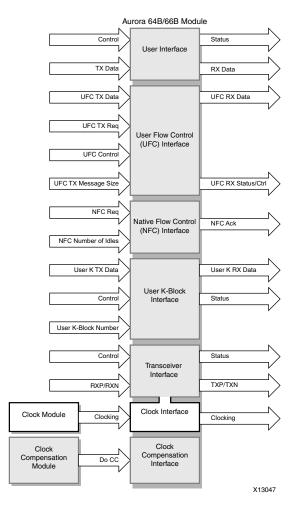

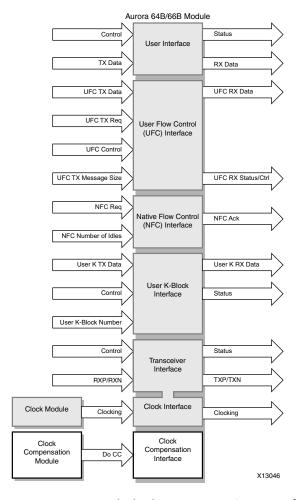

The parameters used to generate each Aurora 64B/66B core determine the interfaces available (Figure 2-3) for that specific core. The Aurora 64B/66B cores have four to seven interfaces:

- User Interface, page 14

- User Flow Control Interface, page 16

- Native Flow Control Interface, page 17

- User K-Block Interface, page 18

- GTX/GTH Transceiver Interface, page 22

- Clock Interface, page 24

- Clock Compensation Interface, page 51

Figure 2-3: Top-Level Interface

## **User Interface**

This interface includes all the ports needed to read and write *streaming* or *framed* data to and from the Aurora 64B/66B core. AXI4-Stream ports are used if the Aurora 64B/66B core is generated with a framing interface; for streaming modules, the interface consists of a simple set of data ports with data valid and ready ports. Full-duplex cores include ports for both transmit (TX) and receive (RX); simplex cores use only the ports they require in the direction they support. The width of the data ports in all interfaces depends on the number of GTX/GTH transceivers used by the core. CRC is computed on the data interface for every frame in the framing interface, if the CRC32 option is selected.

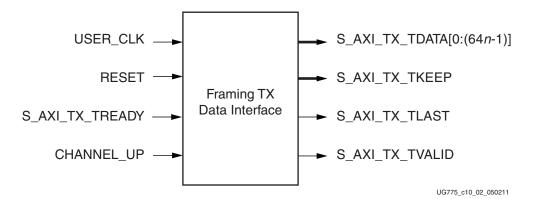

## Framing Interface Ports (AXI4-Stream)

Table 2-3 lists the AXI4-Stream TX data ports and their descriptions.

Table 2-3: AXI4-Stream User I/O Ports (TX)

| Name                            | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_TX_TDATA[0:(64n-1)]       | Input     | Outgoing data (Ascending bit order).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| S_AXI_TX_TREADY                 | Output    | Asserted (active-High) during clock edges when signals from the source are accepted (if S_AXI_TX_TVALID is also asserted).  Deasserted (active-Low) on clock edges when signals from the source are ignored.                                                                                                                                                                                                                                              |

| S_AXI_TX_TLAST                  | Input     | Signals the end of the frame (active-High).                                                                                                                                                                                                                                                                                                                                                                                                               |

| S_AXI_TX_TKEEP[0:8 <i>n</i> -1] | Input     | Specifies the number of valid bytes in the last data beat (number of valid bytes = number of 1s in TKEEP. Example: S_AXI_TX_TKEEP = FF indicates 8 bytes are valid); valid only while S_AXI_TX_TLAST is asserted. The Aurora core supports continuous aligned stream and continuous unaligned stream of data and expects the data to be filled continuously from LSB to MSB. There cannot be invalid bytes interleaved with the valid S_AXI_TX_TDATA bus. |

| S_AXI_TX_TVALID                 | Input     | Asserted (active-High) when AXI4-Stream signals from the source are valid.  Deasserted (active-Low) when AXI4-Stream control signals and/or data from the source should be ignored.                                                                                                                                                                                                                                                                       |

See Framing Interface, page 27 for more information.

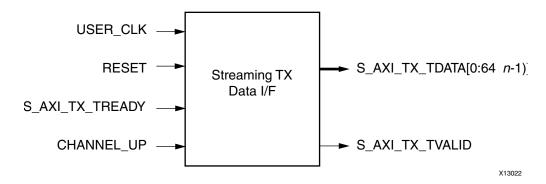

## **Streaming Ports**

Table 2-4 lists the streaming TX data ports.

Table 2-4: Streaming User I/O Ports (TX)

| Name                               | Direction | Description                                                                                                                                                                                                  |

|------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_TX_TDATA[0:(64 <i>n</i> -1)] | Input     | Outgoing data (Ascending bit order).                                                                                                                                                                         |

| S_AXI_TX_TREADY                    | Output    | Asserted (active-High) during clock edges when signals from the source are accepted (if S_AXI_TX_TVALID is also asserted).  Deasserted (active-Low) on clock edges when signals from the source are ignored. |

| S_AXI_TX_TVALID                    | Input     | Asserted (active-High) when AXI4-Stream signals from the source are valid.  Deasserted (active-Low) when AXI4-Stream control signals and/or data from the source should be ignored.                          |

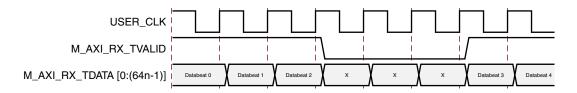

Table 2-5 lists the streaming RX data ports. These ports are included on full-duplex and simplex RX framing cores.

Table 2-5: Streaming User I/O Ports (RX)

| Name                               | Direction | Description                                                                                                                                                                                          |

|------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M_AXI_RX_TDATA[0:(64 <i>n</i> -1)] | Output    | Incoming data from channel partner (Ascending bit order).                                                                                                                                            |

| M_AXI_RX_TVALID                    | Output    | Asserted (active-High) when data and control signals from an Aurora 64B/66B core are valid.  Deasserted (active-Low) when data and/or control signals from an Aurora 64B/66B core should be ignored. |

See Streaming Interface, page 34 for more information.

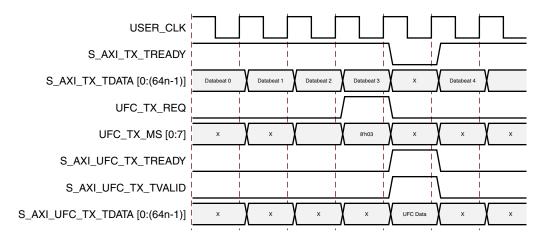

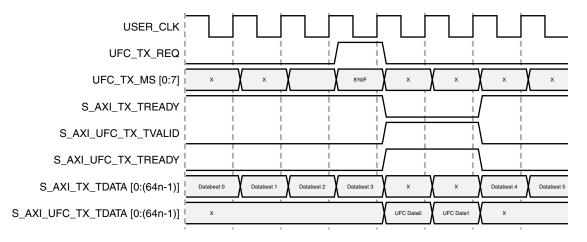

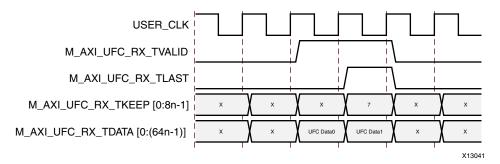

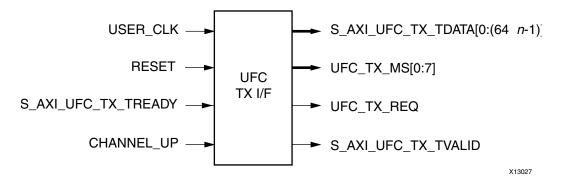

### **User Flow Control Interface**

If the core is generated with User Flow Control (UFC) enabled, a UFC interface is created. The TX side of the UFC interface consists of a request, valid, and ready ports that are used to start a UFC message, and a port to specify the length of the message. You supply the message data to the UFC data port immediately after a UFC request, depending on valid and ready ports of the UFC interface; this in turn deasserts the ready port of the user data interface indicating that the core is no longer ready for normal data, thereby allowing UFC data to be written to the UFC data port.

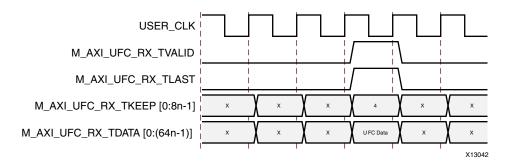

The RX side of the UFC interface consists of a set of AXI4-Stream ports that allows the UFC message to be read as a frame. Full-duplex modules include both TX and RX UFC ports; simplex modules retain only the interface they need to send data in the direction they support. Table 2-6 describes the ports for the UFC interface.

Table 2-6: UFC I/O Ports

| Name           | Direction | Description                                                                                                                                                                                                                                                                                                                          |

|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UFC_TX_REQ     | Input     | Asserted (active-High) to request a UFC message be sent to the channel partner. Requests are processed after a single cycle, unless another UFC message is in progress and not on its last cycle. After a request, the S_AXI_UFC_TX_TDATA bus is ready to send data within two cycles unless interrupted by a higher priority event. |

| UFC_TX_MS[0:7] | Input     | Specifies the number of bytes in the UFC message (the message size). The maximum UFC message size is 256. The value specified at UFC_TX_MS is one less than the actual amount of bytes transferred. For example, a value of 3 will transmit 4 bytes of data; and a value of 0 will transfer 1 byte.                                  |

Table 2-6: UFC I/O Ports (Cont'd)

| Name                                   | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_UFC_TX_TREADY                    | Output    | Asserted (active-High) when an Aurora 64B/66B core is ready to read data from the S_AXI_UFC_TX_TDATA interface. This signal is asserted one clock cycle after UFC_TX_REQ is asserted and no high priority requests in progress.  S_AXI_UFC_TX_TREADY continues to be asserted while the core waits for data for the most recently requested UFC message. The signal is deasserted for CC, CB, and NFC requests, which are higher priority. While S_AXI_UFC_TX_TREADY is asserted, S_AXI_TX_TREADY is deasserted. |

| S_AXI_UFC_TX_TDATA[0:(64 <i>n</i> -1)] | Input     | Input bus for UFC message data to the Aurora channel. Data is read from the bus into the channel only when both S_AXI_UFC_TX_TVALID and S_AXI_UFC_TX_TREADY are asserted on a positive USER_CLK edge. If the number of bytes in the message is not an integer multiple of the bytes in the bus, on the last cycle, only the bytes needed to finish the message starting from the left of the bus are used.                                                                                                       |

| S_AXI_UFC_TX_TVALID                    | Input     | Asserted (active-High) when data on S_AXI_UFC_TX_TDATA is valid. If deasserted while S_AXI_UFC_TX_TREADY is asserted, Idle blocks are inserted in the UFC message.                                                                                                                                                                                                                                                                                                                                               |

| M_AXI_UFC_RX_TDATA[0:(64 <i>n</i> -1)] | Output    | Incoming UFC message data from the channel partner.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| M_AXI_UFC_RX_TVALID                    | Output    | Asserted (active-High) when the values on the M_AXI_UFC_RX_TDATA port is valid. When this signal is not asserted, all values on the M_AXI_UFC_RX_TDATA port should be ignored.                                                                                                                                                                                                                                                                                                                                   |

| M_AXI_UFC_RX_TLAST                     | Output    | Signals (active-High) the end of the incoming UFC message.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M_AXI_UFC_RX_TKEEP[0:(8n-1)]           | Output    | Specifies the number of valid bytes of data presented on the M_AXI_UFC_RX_TDATA port on the last word of a UFC message. Valid only when M_AXI_UFC_RX_TLAST is asserted. Maximum size of UFC is 256 bytes.                                                                                                                                                                                                                                                                                                        |

See User Flow Control, page 39 for more information.

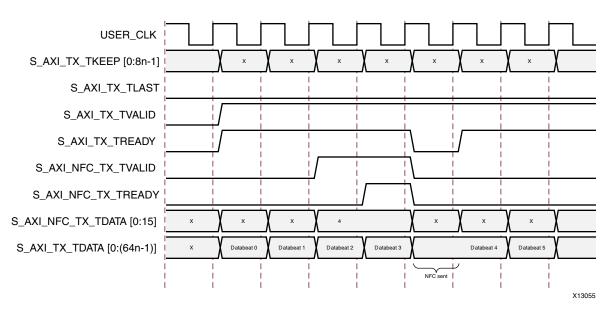

## **Native Flow Control Interface**

If the core is generated with native flow control (NFC) enabled, an NFC interface is created. This interface includes a request and an acknowledge port that are used to send NFC messages, an NFC XOFF bit that when asserted sends XOFF code to the lane partner to stop transmission, and a 16-bit port to specify the NFC PAUSE count (number of idle cycles requested) and NFC XOFF.

**Note:** NFC completion mode is not applicable to streaming designs.

Table 2-7 lists the ports for the NFC interface.

Table 2-7: NFC I/O Ports

| Name                     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_NFC_TX_TVALID      | Input     | Asserted (active-High) to request an NFC message be sent to the channel partner. Must be held until S_AXI_NFC_TX_TREADY is asserted.                                                                                                                                                                                                                                                                                                                                             |

| S_AXI_NFC_TX_TREADY      | Output    | Asserted (active-High) when an Aurora 64B/66B core accepts an NFC request.                                                                                                                                                                                                                                                                                                                                                                                                       |

| S_AXI_NFC_TX_TDATA[0:15] | Input     | S_AXI_NFC_TX_TDATA[8:15]: Indicates how many USER_CLK cycles the channel partner must wait before it can send data when it receives the NFC message. Must be held until S_AXI_NFC_TX_TREADY is asserted. The number of USER_CLK cycles without data is equal to S_AXI_NFC_TX_TDATA + 1. S_AXI_NFC_TX_TDATA[7] - Indicates NFC_XOFF. Assert to send an NFC_XOFF message, requesting that the channel partner stop sending data until it receives a non-XOFF NFC message or reset. |

See Native Flow Control, page 37 for more information.

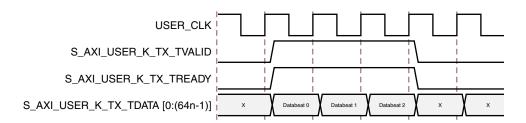

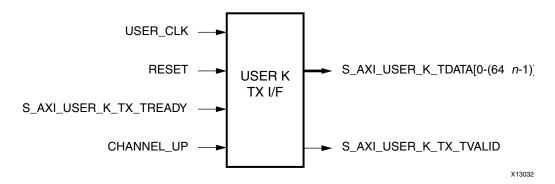

#### **User K-Block Interface**

If the core is generated with the User K-block feature enabled, a User K interface is created. User K-blocks are special single block codes that include control blocks that are not decoded by the Aurora interface, but are instead passed directly to the user application. These blocks can be used to implement application specific control functions. The TX side consists of valid and ready ports that are used to start a User K transmission along with the block number port to indicate which of the nine User K-blocks needs to be transmitted. The User K data is transmitted after the core provides a ready for the User K interface. It also indicates to the user interface that it is no longer ready for normal data, thereby allowing User K data to be written to the User K data port. The User K blocks are single block codes.

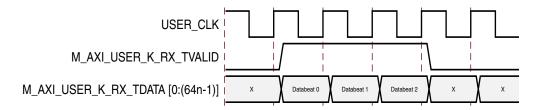

The receive side of the User K interface consists of an RX valid signal to indicate the reception of User K-block. Full-duplex modules include both TX and RX User K ports; simplex modules retain only the interface they need to send data in the direction they support.

Table 2-8 lists the ports for the User K-block interface.

Table 2-8: User K-Block I/O Ports

| Name                             | Direction | Description                                                                                                                                                              |

|----------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AXI_USER_K_TX_TDATA[0:(64n-1)] | Input     | User K-block data is 64-bit aligned. Signal Mapping per lane: S_AXI_USER_K_TX_TDATA={4'h0,USER K BLOCK NO[0:3],S_AXI_USER_K_TDATA[0:56n-1]}.                             |

| S_AXI_USER_K_TX_TVALID           | Input     | Asserted (active-High) when User K data on S_AXI_USER_K_TX_TDATA port is valid.                                                                                          |

| S_AXI_USER_K_TX_TREADY           | Output    | Asserted (active-High) when the Aurora 64B/66B core is ready to read data from the S_AXI_USER_K_TX_TDATA interface.                                                      |

| M_AXI_USER_K_RX_TVALID           | Output    | Asserted (active-High) when User K data on M_AXI_USER_K_RX_TDATA port is valid.                                                                                          |

| M_AXI_USER_K_RX_TDATA[0:(64n-1)] | Output    | Receive User K-blocks from the Aurora lane is 64-bit aligned.  Signal Mapping per lane:  M_AXI_USER_K_RX_TDATA={4'h0,RX USER K BLOCK NO[0:4n-1],RX USER K DATA[0:56n-1]} |

See User K-Block Interface, page 18 for more information.

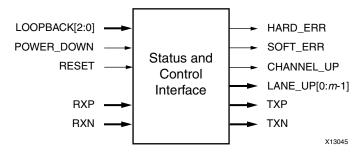

## **Status and Control Ports**

Table 2-9 describes the function of the status and control ports for full-duplex cores.

Table 2-9: Status and Control Ports for Full-Duplex Cores

| Name               | Direction | Description                                                                                                                                                                                                                                                                                        |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL_UP         | Output    | Asserted (active-High) when Aurora channel initialization is complete and channel is ready to send data.                                                                                                                                                                                           |

| LANE_UP[0:m-1] (1) | Output    | Asserted (active-High) for each lane upon successful lane initialization, with each bit representing one lane. The Aurora 64B/66B core can only receive data after all LANE_UP signals are asserted.                                                                                               |

| HARD_ERR           | Output    | Hard error detected (active-High, asserted until Aurora 64B/66B core resets). See Table 2-18, page 46 for more details.                                                                                                                                                                            |

| LOOPBACK[2:0]      | Input     | See the 7 Series FPGAs GTX/GTH Transceivers User Guide for details about loopback. See References in Appendix E.                                                                                                                                                                                   |

| POWER_DOWN         | Input     | Drives the power-down input to the GTX/GTH transceiver (active-High).                                                                                                                                                                                                                              |

| RESET              | Input     | Resets the Aurora 64B/66B core (active-High) is connected to top level through a debouncer. This port systematically resets all of the Aurora core logic. This signal is debounced using USER_CLK for at least 6 USER_CLK cycles. See Reset and Power Down in this product guide for more details. |

| SOFT_ERR           | Output    | Soft error detected in the incoming serial stream. See Table 2-18, page 46 for more details (active-High, asserted for a single clock).                                                                                                                                                            |

Table 2-9: Status and Control Ports for Full-Duplex Cores (Cont'd)

| Name                           | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RXP[0: <i>m</i> -1]            | Input     | Positive differential serial data input pin.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| RXN[0: <i>m</i> -1]            | Input     | Negative differential serial data input pin.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| TXP[0:m-1]                     | Output    | Positive differential serial data output pin.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TXN[0:m-1]                     | Output    | Negative differential serial data output pin.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| PMA_INIT Input  INIT_CLK Input |           | The PMA_INIT (active-High) reset signal for the serial transceiver is connected to the top level through a debouncer. This port systematically resets all Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) subcomponents of the transceiver.  The signal is debounced using INIT_CLK_IN for at least 6 INIT_CLK cycles.  See the Reset section in the user guide of the related transceiver for more details. |  |

|                                |           | INIT_CLK is used to register and debounce the PMA_INIT signal. The rate of INIT_CLK is preferred to be slower than the serial transceiver reference clock rate.                                                                                                                                                                                                                                                                  |  |

#### Notes:

Table 2-10 describes the function of the status and control ports for simplex-TX cores.

Table 2-10: Status and Control Ports for Simplex-TX Cores

| Name                             | Direction | Description                                                                                                                                                                                              |

|----------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CHANNEL_UP                    | Output    | Asserted (active-High) when Aurora channel initialization is complete and channel is ready to send data.                                                                                                 |

| TX_LANE_UP[0:m-1] <sup>(1)</sup> | Output    | Asserted (active-High) for each lane upon successful lane initialization, with each bit representing one lane. The Aurora 64B/66B core can only transmit data after all TX_LANE_UP signals are asserted. |

| TX_HARD_ERR                      | Output    | Hard error detected (active-High, asserted until Aurora 64B/66B core resets). See Table 2-18, page 46 for more details.                                                                                  |

| POWER_DOWN                       | Input     | Drives the power-down input to the GTX/GTH transceiver (active-High).                                                                                                                                    |

| RESET                            | Input     | Resets the Aurora 64B/66B core (active-High). This signal must be synchronous to USER_CLK and must be asserted for at least six USER_CLK cycles.                                                         |

| TX_SOFT_ERR                      | Output    | Soft error detected in the transmit logic. See Table 2-18, page 46 for more details (active-High, asserted for a single clock).                                                                          |

| TXP[0:m-1]                       | Output    | Positive differential serial data output pin.                                                                                                                                                            |

| TXN[0:m-1]                       | Output    | Negative differential serial data output pin.                                                                                                                                                            |

<sup>1.</sup> *m* is the number of GTX/GTH transceivers

Table 2-10: Status and Control Ports for Simplex-TX Cores

| Name     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PMA_INIT | Input     | The PMA_INIT (active-High) reset signal for the serial transceiver is connected to the top level through a debouncer. This port systematically resets all Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) subcomponents of the transceiver. The signal is debounced using INIT_CLK_IN for at least 6 INIT_CLK cycles. See the Reset section in the user guide of relevant transceiver for more details. |  |

| INIT_CLK | Input     | INIT_CLK is used to register and debounce the PMA_INIT signal. The rate of INIT_CLK is preferred to be slower than the serial transceiver reference clock rate.                                                                                                                                                                                                                                                             |  |

#### **Notes:**

Table 2-11 describes the function of the status and control ports for simplex-RX cores.

Table 2-11: Status and Control Ports for Simplex-RX Cores

| Name                                      | Direction | Direction                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_CHANNEL_UP                             | Output    | Asserted (active-High) when Aurora channel initialization is complete and the channel is ready to receive data.                                                                                                                                                                                                                           |

| RX_LANE_UP[0: <i>m</i> -1] <sup>(1)</sup> | Output    | Asserted (active-High) for each lane upon successful lane initialization, with each bit representing one. The Aurora 64B/66B core can only receive data after all RX_LANE_UP signals are asserted.                                                                                                                                        |

| RX_HARD_ERR                               | Output    | Hard error detected (active-High, asserted until Aurora 64B/66B core resets). See Table 2-18, page 46 for more details.                                                                                                                                                                                                                   |

| POWER_DOWN                                | Input     | Drives the power-down input to the GTX/GTH transceiver (active-High).                                                                                                                                                                                                                                                                     |

| RESET                                     | Input     | Resets the Aurora 64B/66B core (active-High). This signal must be synchronous to USER_CLK and must be asserted for at least six USER_CLK cycles.                                                                                                                                                                                          |

| RX_SOFT_ERR                               | Output    | Soft error detected in the receive logic. See Table 2-18, page 46 for more details. (active-High, asserted for a single clock).                                                                                                                                                                                                           |

| RXP[0:m-1]                                | Input     | Positive differential serial data input pin.                                                                                                                                                                                                                                                                                              |

| RXN[0: <i>m</i> -1]                       | Input     | Negative differential serial data input pin.                                                                                                                                                                                                                                                                                              |

| PMA_INIT                                  | Input     | The PMA_INIT (active-High) reset signal for the serial transceiver is connected to the top level through a debouncer. This port systematically resets all Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) subcomponents of the transceiver. The signal is debounced using INIT_CLK_IN for at least 6 INIT_CLK cycles. |

| INIT_CLK                                  | Input     | INIT_CLK is used to register and debounce the PMA_INIT signal. The rate of INIT_CLK is preferred to be slower than the serial transceiver reference clock rate.                                                                                                                                                                           |

#### Notes:

1. *m* is the number of GTX and GTH transceivers.

<sup>1.</sup> *m* is the number of GTX and GTH transceivers.

See Status and Control Ports, page 19 for more information.

# **GTX/GTH Transceiver Interface**

This interface includes the serial I/O ports of the GTX/GTH transceivers and the control and status ports of the Aurora 64B/66B core. This interface is your access to control functions such as reset, loopback, and power down. The DRP interface can be used to access or update the serial transceiver parameters and settings through the AXI4-Lite or Native DRP interface.

Table 2-12 describes the available transceiver ports.

Table 2-12: Transceiver Ports

| Name                      | Direction | Description                                                                                                                                |  |

|---------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| RXP[0:m-1] <sup>(1)</sup> | Input     | Positive differential serial data input pin.                                                                                               |  |

| RXN[0: <i>m</i> -1]       | Input     | Negative differential serial data input pin.                                                                                               |  |

| TXP[0:m-1]                | Output    | Positive differential serial data output pin.                                                                                              |  |

| TXN[0:m-1]                | Output    | Negative differential serial data output pin.                                                                                              |  |

| POWER_DOWN                | Input     | Drives the power-down input of the GTX/GTH transceiver (active-High).                                                                      |  |

| LOOPBACK[2:0]             | Input     | Loopback port of the transceiver. See the related transceiver user guide for loopback test mode configurations                             |  |

| PMA_INIT                  | Input     | Asynchronous reset signal for the transceiver. See the related transceiver user guide for more information.                                |  |

| TX_LOCK                   | Output    | Indicates incoming serial transceiver REFCLK is locked by the transceiver PLL. See the related transceiver user guide for more information |  |

**Table 2-12:** Transceiver Ports

| Name       | Direction                                          | n Description                                                                               |  |  |  |  |

|------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

|            | 7 Series FPGA Transceiver DRP Ports <sup>(2)</sup> |                                                                                             |  |  |  |  |

| DRPADDR_IN | Input                                              | DRP address bus.                                                                            |  |  |  |  |

| DRPCLK_IN  | Input                                              | DRP interface clock.                                                                        |  |  |  |  |

| DRPDI_IN   | Input                                              | Data bus for writing configuration data from the FPGA logic resources to the transceiver    |  |  |  |  |

| DRPDO_OUT  | Output                                             | Data bus for reading configuration data from the transceiver to the FPGA logic resources.   |  |  |  |  |

| DRPEN_IN   | Input                                              | DRP enable signal.                                                                          |  |  |  |  |

| DRPRDY_OUT | Output                                             | Indicates operation is complete for write operations and data is valid for read operations. |  |  |  |  |

| DRPWE_IN   | Input                                              | DRP write enable.                                                                           |  |  |  |  |

<sup>1.</sup> m is the number of GTX/GTH transceivers

<sup>2.</sup> See the related transceiver user guide for more information on DRP operation

## **Clock Interface**

**IMPORTANT:** This interface is most critical for correct Aurora 64B/66B core operation. The clock interface has ports for the reference clocks that drive the GTX/GTH transceivers and ports for the parallel clocks that the Aurora 64B/66B core shares with application logic.

Table 2-13 describes the Virtex®-7 and Kintex®-7 FPGA Aurora 64B/66B core clock ports. In GTX/GTH transceiver designs, the reference clock can be from GTXQ/GTHQ, which is a differential input clock for each GTX/GTH transceiver. The reference clock for a GTX/GTH transceiver is provided through the CLKIN port.

Table 2-13: Clock Ports for a Virtex-7 and Kintex-7 FPGA Aurora 64B/66B Core

| Name            | Direction | n Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MMCM_NOT_LOCKED | Input     | If a MMCM is used to generate clocks for the Aurora 64B/66B core, the MMCM_NOT_LOCKED signal should be connected to the inverse of the PLL LOCKED signal of the serial transceiver PLL. The clock modules provided with the Aurora 64B/66B core use the PLL for clock division. The MMCM_NOT_LOCKED signal from the clock module should be connected to the MMCM_NOT_LOCKED signal on the Aurora 64B/66B core. |  |  |

| USER_CLK        | Input     | Parallel clock shared by the Aurora 64B/66B core and the user application. The USER_CLK is the output of a BUFG whose input is derived from TX_OUT_CLK. See the related transceiver user guide/data sheet for rate related information.                                                                                                                                                                        |  |  |

| TX_OUT_CLK      | Output    | Clock signal from Virtex-7/Kintex-7 device GTX/GTH transceiver. The GTX/GTH transceiver generates TX_OUT_CLK from its reference clock based on its PLL speed setting. This clock should be buffered and used to generate the user clock for logic connected to the Aurora 64B/66B core.                                                                                                                        |  |  |

| SYNC_CLK        | Input     | Parallel clock used by internal synchronization logic of the serial transceivers in the Aurora 64B/66B core. This clock is provided as the TXUSRCLK to the transceiver interface. SYNC_CLK is used as TXUSERCLK and USER_CLK is TXUSRCLK2. SYNC_CLK is double the rate of USER_CLK. See the related transceiver user guide/data sheet for rate related information.                                            |  |  |

| PLL_LOCK        | Output    | Active-High, asserted when TX_OUT_CLK is stable. When this signal is deasserted (Low), circuits using TX_OUT_CLK should be held in reset.                                                                                                                                                                                                                                                                      |  |  |

For more details on the clock interface, see Clocking, page 53.

# **Detailed Functional Description**

An Aurora 64B/66B core can be generated with either a framing or streaming user data interface. In addition, flow control options are available for designs with framing interfaces. See Flow Control.

The framing user interface complies with the AXI4-Stream Protocol Specification (AMBA AXI4-Stream Protocol Specification). It comprises the signals necessary for transmitting and receiving framed user data. The streaming interface allows you to send data without frame delimiters. It is simple to operate and uses fewer resources than framing

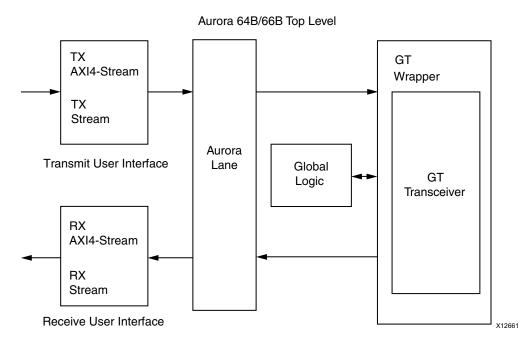

## **Top-Level Architecture**

The Aurora 64B/66B top-level (block level) file instantiates the Aurora lane module, the TX and RX AXI4-Stream modules, the global logic module, and the wrapper for the GTX/GTH transceiver. This top-level wrapper file is instantiated in the example design file together with clock, reset circuit, and frame generator and checker modules.

Figure 2-4 shows the Aurora 64B/66B top level for a duplex configuration. The top-level file is the starting point for a user design.

Figure 2-4: Top-Level Architecture

The following sections describe the streaming and framing interfaces in detail. User interface logic should be designed such that it complies with timing requirements of the respective interface as explained in the subsequent sections.

Figure 2-5: Top-Level User Interface

**Note:** The user interface signals vary depending upon the selections made when generating an Aurora 64B/66B core using the Vivado IP catalog.

#### **Framing Interface**

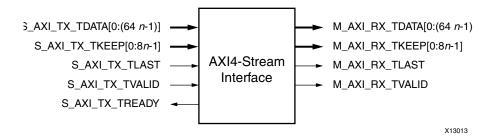

Figure 2-6 shows the framing user interface of the Aurora 64B/66B core, with AXI4-Stream compliant ports for TX and RX data.

Figure 2-6: Aurora 64B/66B Core Framing Interface (AXI4-Stream)

To transmit data, the user application should manipulate the control signals to cause the core to do the following:

- Take data from the user application on the S\_AXI\_TX\_TDATA bus

- Encapsulate and stripe the data across lanes in the Aurora channel (S\_AXI\_TX\_TLAST)

- Pause data (that is, insert idles) (S\_AXI\_TX\_TVALID)

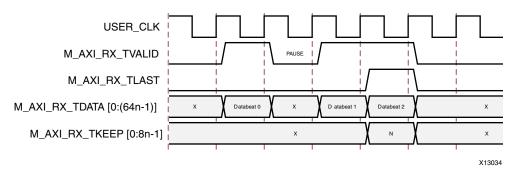

When the core receives data, it does the following:

- Detects and discards control bytes (idles, clock compensation)

- Asserts framing signals (M\_AXI\_RX\_TLAST)

- Recovers data from the lanes

- Assembles data for presentation to the user application on the M\_AXI\_RX\_TDATA bus along with valid number of bytes (M\_AXI\_RX\_TKEEP) during the M\_AXI\_RX\_TLAST cycle

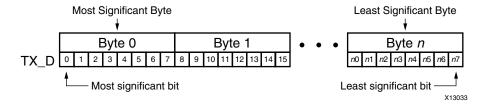

The AXI4-Stream user interface of Aurora 64B/66B cores uses ascending ordering. The cores transmit and receive the most significant bit of the least significant byte first. Figure 2-7 shows the organization of an n-byte example of the AXI4-Stream data interfaces of an Aurora 64B/66B core.

Figure 2-7: AXI4-Stream Interface Bit Ordering

#### **Transmitting Data**

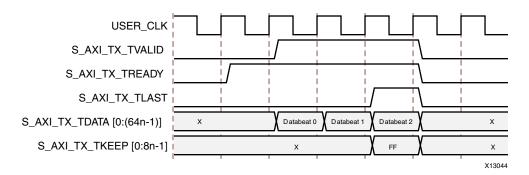

AXI4-Stream is a synchronous interface. The Aurora 64B/66B core samples the data on the interface only on the positive edge of USER\_CLK, and only on the cycles when both S\_AXI\_TX\_TREADY and S\_AXI\_TX\_TVALID are asserted (active-High).

When AXI4-Stream signals are sampled, they are only considered valid if S\_AXI\_TX\_TVALID and S\_AXI\_TX\_TREADY signals are asserted. The user application can deassert S\_AXI\_TX\_TVALID on any clock cycle; this causes the Aurora core to ignore the AXI4-Stream input for that cycle. If this occurs in the middle of a frame, idle symbols are sent through the Aurora channel, which eventually result in a idle cycles during the frame when it is received at the RX user interface.

AXI4-Stream data is only valid when it is framed. Data outside of a frame is ignored. To end a frame, assert S\_AXI\_TX\_TLAST while the last word (or partial word) of data is on the S\_AXI\_TX\_TDATA port. If the CRC option is selected, CRC is calculated and inserted into the data stream after the last data word. This re-calculates S\_AXI\_TX\_TKEEP based on the number of valid CRC bytes and asserts S\_AXI\_TX\_TLAST accordingly.

#### **Data Strobe**

AXI4-Stream allows the last word of a frame to be a partial word. This lets a frame contain any number of bytes, regardless of the word size. The S\_AXI\_TX\_TKEEP bus is used to indicate the number of valid bytes in the final word of the frame. The bus is only used when S\_AXI\_TX\_TLAST is asserted. TKEEP is the number of valid bytes in the S\_AXI\_TX\_TDATA bus. TKEEP associates validity to a particular byte in the last data beat of a frame. If TKEEP is "OF" in the last beat of data with S\_AXI\_TX\_TLAST asserted high, then 4 (LSB bytes) out of 8 bytes are valid and byte4 to byte7 are not valid. All 1s in the S\_AXI\_TX\_TKEEP value indicate all bytes in the S\_AXI\_TX\_TDATA port are valid. S\_AXI\_TX\_TKEEP does not specify the position of the valid bytes, but is the number of valid bytes on the last beat of data with S\_AXI\_TX\_TLAST asserted. Core expects TKEEP to be left aligned from LSB. See Appendix B, Migrating for limitations on the types of data stream supported by the core.

#### Aurora 64B/66B Frames

The TX submodule translates each user frame that it receives through the TX interface to an Aurora 64B/66B frame. The core starts an Aurora 64B/66B frame by sending a data block with the first word of data, and ends the frame by sending a separator block containing the last bytes of the frame. Idle blocks are inserted whenever data is not available. Blocks are eight bytes of scrambled data or control information with a two-bit control header (a total of 66 bits). All data in Aurora 64B/66B is sent as part of a data block or a separator block (a separator block consists of a count field, indicating how many bytes are valid in that particular block).

Table 2-14 shows a typical Aurora 64B/66B frame with an even number of data bytes.

#### Length

The user application controls the channel frame length by manipulating the S\_AXI\_TX\_TVALID and S\_AXI\_TX\_TLAST signals. The Aurora 64B/66B core converts these to data blocks, idle blocks, and separator blocks, as shown in Table 2-14.

**Table 2-14:** Typical Channel Frame

| Data Byte<br>0 | Data Byte<br>1 | Data Byte<br>2 | Data Byte<br>3 |                | Data Byte<br>n -2 | Data Byte<br>n -1 | Data Byte<br>n |

|----------------|----------------|----------------|----------------|----------------|-------------------|-------------------|----------------|

| SEP (1E)       | Count (4)      | Data Byte<br>0 | Data Byte<br>1 | Data Byte<br>2 | Data Byte<br>3    | х                 | х              |

#### **Example A: Simple Data Transfer**

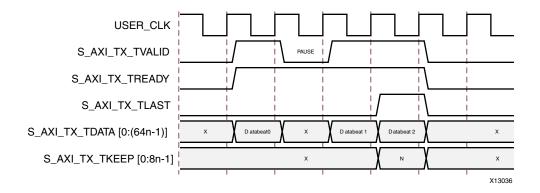

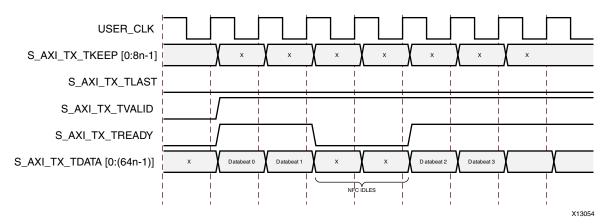

Figure 2-8 shows an example of a simple data transfer on a AXI4-Stream interface that is n bytes wide. In this case, the amount of data being sent is 3n bytes and so requires three data beats.  $S_AXI_TX_TREADY$  is asserted, indicating that the AXI4-Stream interface is ready to transmit data. When the Aurora 64B/66B is not sending data, it sends idle blocks.

To begin the data transfer, the user application asserts  $S_{AXI\_TX\_TVALID}$  and provides the first n bytes of the user frame. Because  $S_{AXI\_TX\_TREADY}$  is already asserted, data transfer begins on the next clock edge. The data bytes are placed in data blocks and transferred through the Aurora channel.

To end the data transfer, the user application asserts  $S_AXI_TX_TLAST$ ,  $S_AXI_TX_TVALID$ , the last data bytes, and the appropriate value on the  $S_AXI_TX_TKEEP$  bus. In this example,  $S_AXI_TX_TKEEP$  is set to FF to indicate that all bytes are valid in the last data beat. The Aurora 64B/66B core sends the final word of data in data blocks, and must send an empty separator block on the next cycle to indicate the end of the frame.  $S_AXI_TX_TREADY$  is reasserted on the next cycle so that more data transfers can continue. As long as there is no new data, the Aurora 64B/66B core sends idles.

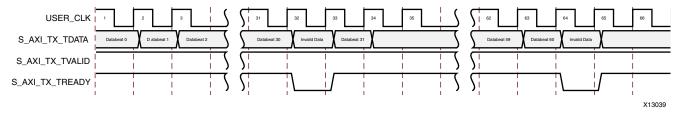

Figure 2-8: Simple Data Transfer

#### **Example B: Data Transfer with Pause**

Figure 2-9 shows how the user application can pause data transmission during a frame transfer. In this example, the user application is sending 3*n* bytes of data, and pauses the data flow after the first *n* bytes. After the first data word, the user application deasserts S\_AXI\_TX\_TVALID, causing the TX Aurora 64B/66B core to ignore all data on the bus and transmit idle blocks instead. The pause continues until S\_AXI\_TX\_TVALID is deasserted.

Figure 2-9: Data Transfer with Pause

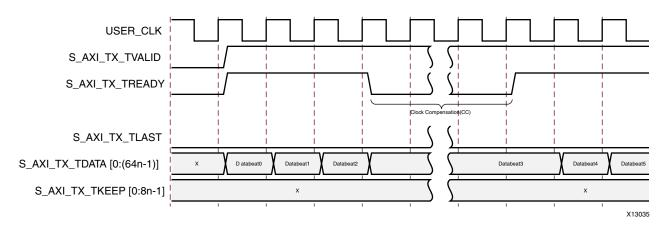

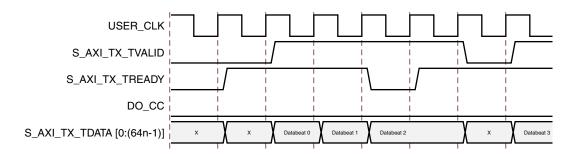

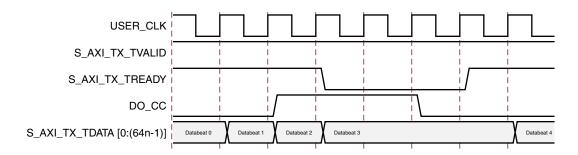

#### **Example C: Data Transfer with Clock Compensation**

The Aurora 64B/66B core automatically interrupts data transmission when it sends clock compensation sequences. The clock compensation sequence imposes three cycles of PAUSE every 10,000 cycles.

Figure 2-10 shows how the Aurora 64B/66B core pauses data transmission during the clock compensation sequence.

#### Notes:

1. When clock compensation is used, uninterrupted data transmission is not possible. See Clock Compensation Interface, page 51 for more information about when clock compensation is required.

Figure 2-10: Data Transfer Paused by Clock Compensation

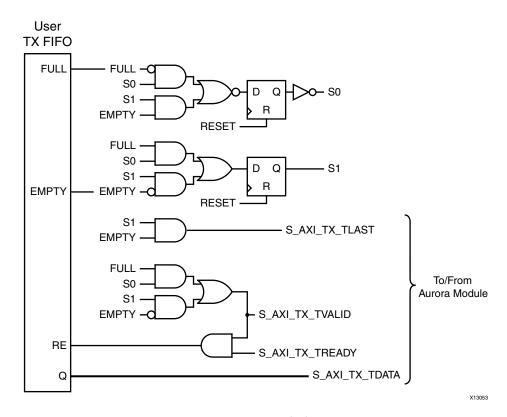

#### TX Interface Example

This section illustrates a simple example of an interface between a transmit FIFO and the AXI4-Stream interface of an Aurora 64B/66B core.

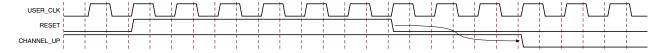

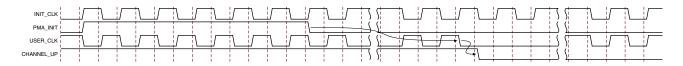

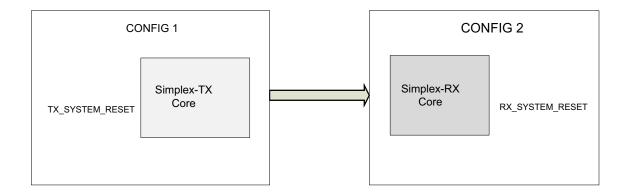

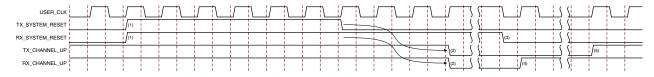

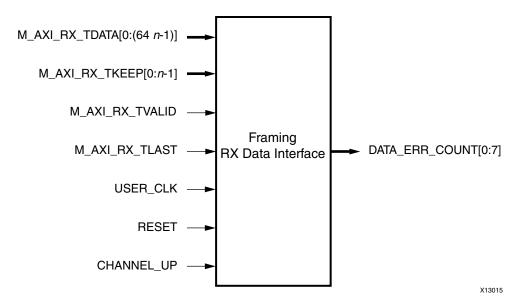

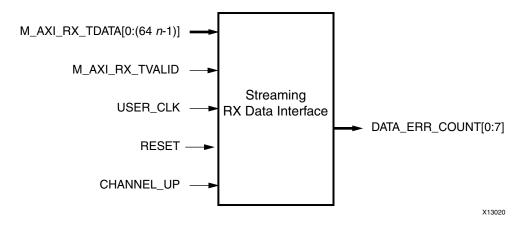

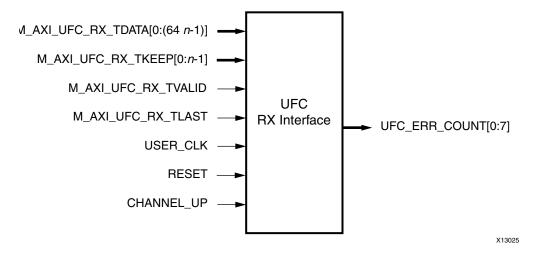

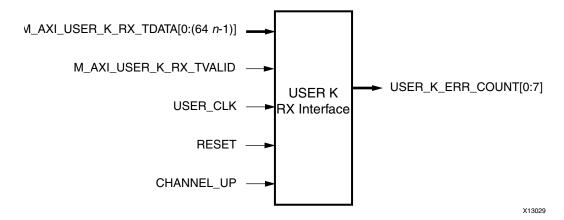

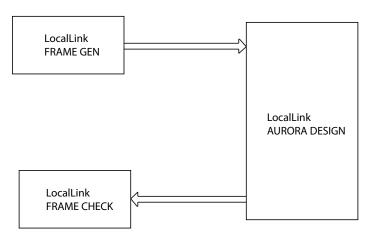

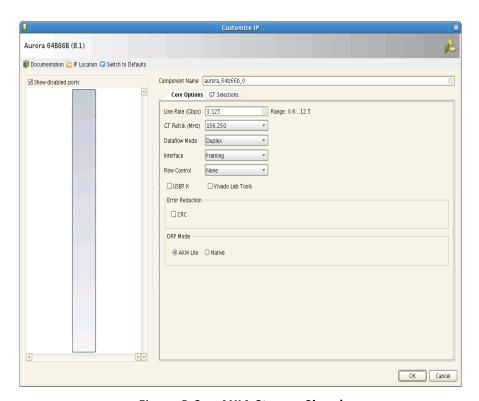

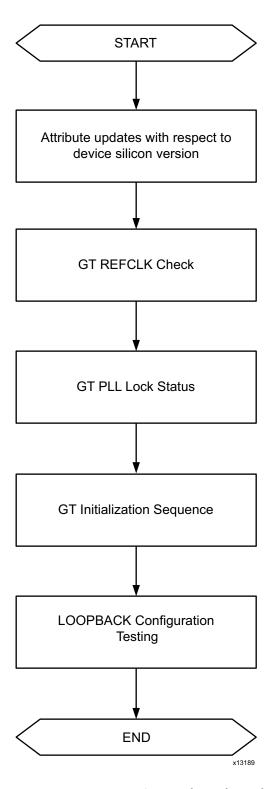

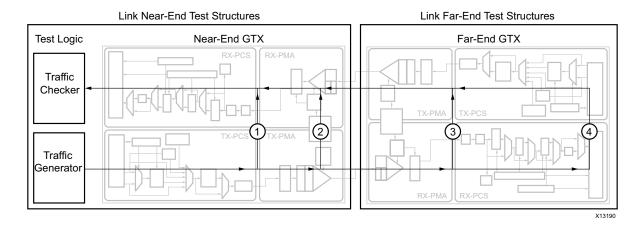

To review, to transmit data, the user application asserts S\_AXI\_TX\_TVALID, S\_AXI\_TX\_TREADY indicates that the data on the S\_AXI\_TX\_TDATA bus is transmitted on the next rising edge of the clock, assuming S\_AXI\_TX\_TVALID remains asserted.