# ISE Design Suite 14: Release Notes, Installation, and Licensing

UG631 (v14.7) July 10, 2020

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 1995-2020 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA® is a registered trademark of ARM in the EU and other countries. CPRI is a trademark of Siemens AG. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                |

|------------|---------|-----------------------------------------------------------------------------------------|

| 07/10/2020 | 14.7    | Updates in the Important Information About This Release section, ISE Design Suite 14.2. |

# **Table of Contents**

| Chapter 1: Release Notes 14.7                                     |

|-------------------------------------------------------------------|

| What's New                                                        |

| Important Information 6                                           |

| Chapter 2: Architecture Support and Requirements                  |

| Operating Systems                                                 |

| Architectures                                                     |

| Compatible Third-Party Tools                                      |

| System Requirements                                               |

| Chapter 3: Download and Installation                              |

| Downloading the ISE Design Suite Tools                            |

| Installing the ISE Design Suite Tools: Overview for All Platforms |

| Platform-Specific Installation Instructions                       |

| Installation Flow                                                 |

| USB FLEXid Dongle Driver Installation                             |

| Network Installations                                             |

| Obtaining Quarterly Releases                                      |

| Uninstalling the ISE Design Suite Tools                           |

| Chapter 4: WebTalk                                                |

| WebTalk Participation                                             |

| Setting WebTalk Install Preference                                |

| Setting WebTalk User Preferences                                  |

| Types of Data Collected                                           |

| Transmission of Data                                              |

| Chapter 5: Obtaining and Managing a License                       |

| Accessing the Product Licensing Site                              |

| Changing Xilinx User Account Information                          |

| Product Licensing Accounts                                        |

| User Types and Actions                                            |

| Creating a License Key File                                       |

3

| Managing License Key Files                        | 43 |

|---------------------------------------------------|----|

| Legacy Licensing                                  | 47 |

| Understanding Your Tool and IP Orders             | 48 |

| Managing User Access to Product Licensing Account | 49 |

| Installing Your License Key File                  | 51 |

| Chapter 6: Technical Support and Documentation    |    |

| Known Issues                                      | 53 |

| Support Site                                      | 53 |

| Customer Training                                 | 53 |

| Documentation                                     | 54 |

| Chapter 7: Older Release Notes                    |    |

| ISE Design Suite 14.6                             | 55 |

| ISE Design Suite 14.5                             | 57 |

| ISE Design Suite 14.4                             | 58 |

| ISE Design Suite 14.3                             | 60 |

| ISE Design Suite 14.2                             | 61 |

| ISE Design Suite 14.1                             | 65 |

# Release Notes 14.7

## What's New

ISE® Design Suite is a proven and mature development environment for All Programmable devices. With the 14.7 release, it now moves into the sustaining phase of its product life cycle. In the future, while there are no more planned ISE major releases, you will continue to receive Xilinx's superior technical support and Xilinx may release periodic updates and patches. If you have not already done so, Xilinx recommends signing up for "My Alerts" at <a href="http://www.xilinx.com/support/answers/18683.htm">http://www.xilinx.com/support/answers/18683.htm</a> to keep you informed.

For new design starts with 7 series and Zynq®, Xilinx recommends that customers migrate to the Vivado® Design Suite. This will allow customers to take advantage of the improved productivity and quality of results found in the new UltraFAST design methodology for Vivado. For new designs on pre 7 series devices, ISE licenses will continue to be provided when purchasing Vivado Design Suite.

#### **Limited Access Devices**

The following devices are Limited Access that require a special license:

- Zynq®-7000

- 。 7Z100

- Virtex®-7

- VX1140T, 2000T, H580T and H870T

**IMPORTANT:** The device Zynq-7000 7Z030 in the SBG485 package is often used as a migration for the Zynq-7000 7Z015 devices. The Zynq-7000 7z015 devices are not supported in ISE Design Suite and you should use Vivado Design Suite to target this device

# **Important Information**

#### **Limited Access Devices**

The following devices are fully supported in Vivado, but are limited access in ISE. A special license is required for their use in ISE.

- Zynq-7000

- 。 7Z100

- Virtex®-7

- VX1140T, 2000T, H580T and H870T

### **Vivado IP Catalog**

Readme files included with IP provided through the Vivado IP Catalog and ISE CORE Generator™ tools have been updated to show a running history of new feature additions.

#### **Updates to Existing IP**

- AXI-PCle IP moved to production

- 1000BASE-X/SGMII

- Virtex-7, Artix-7 and Zyng-7000 moved to production

- GMII to RGMII

- Zynq-7000 moved to production

- QSGMII

- Virtex-7 Kintex-7, Artix-7 and Zynq-7000 moved to production

- 10G Ethernet MAC

- Artix-7 moved to production

- XAUI

- Artix-7 and Zynq-7000 moved to production

- RXAUI

- Artix-7 and Zynq-7000 moved to production

- 10G Ethernet PCS/PMA (10GBASE-R)

- Virtex-7, Kintex-7 and Zynq-7000 moved to production

- 10GBASE-KR access in Vivado only

# **Architecture Support and Requirements**

## **Operating Systems**

Xilinx only supports the following operating systems on x86 and x86-64 processor architectures.

## **Microsoft Windows Support**

- Windows XP Professional (32-bit and 64-bit), English/Japanese

- Windows 7 Professional (32-bit and 64-bit), English/Japanese

- Windows Server 2008 (64-bit)

### **Linux Support**

- Red Hat Enterprise Workstation 5 (32-bit and 64-bit)

- Red Hat Enterprise Workstation 6 (32-bit and 64-bit)

- SUSE Linux Enterprise 11 (32-bit and 64-bit)

## **Architectures**

The following table lists architecture support for commercial products in the ISE® Design Suite WebPACK™ tool versus all other ISE® Design Suite editions. For non-commercial support:

- All Xilinx® Automotive devices are supported in the ISE Design Suite WebPACK tool.

- Xilinx Defense-Grade FPGA devices are supported where their equivalent commercial part sizes are supported.

**Table 2-1:** Architecture Support

|                                                     | ISE WebPACK Tool                                                              | ISE Design Suite<br>(All Other Editions)                     |

|-----------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|

| Zynq® Device                                        | Zynq-7000 Device • XC7Z010, XC7Z020, XC7Z030                                  | Zynq-7000 Device • All                                       |

| Virtex® FPGA                                        | Virtex-4 FPGA  LX: XC4VLX15, XC4VLX25  SX: XC4VSX25  FX: XC4VFX12             | Virtex-4 FPGA  • All  Virtex-5 FPGA  • All                   |

|                                                     | Virtex-5 FPGA  LX: XC5VLX30, XC5VLX50  LXT: XC5VLX20T - XC5VLX50T  SXT: None  | Virtex-6 FPGA • All                                          |

|                                                     | <ul><li>FXT: XC5VFX30T</li><li>Virtex-6 FPGA</li><li>LXT: XC6VLX75T</li></ul> | <ul><li>Virtex-7 FPGA</li><li>All non-SSIT devices</li></ul> |

|                                                     | Virtex-7 FPGA • None                                                          |                                                              |

| Kintex™ FPGA                                        | Kintex-7 FPGA • XC7K70T, XC7K160T                                             | Kintex-7 FPGA • All                                          |

| Artix™ FPGA                                         | Artix-7 FPGA • XC7A100T, XC7A200T                                             | Artix-7 FPGA • All                                           |

| Spartan® FPGA                                       | Spartan-3 FPGA • XC3S50 - XC3S1500(L)                                         | Spartan-3 FPGA • All                                         |

|                                                     | Spartan-3A/-3AN/-3E FPGA • All                                                | Spartan-3A/-3AN/-3E FPGA • All                               |

|                                                     | Spartan-3A DSP FPGA • XC3SD1800A                                              | Spartan-3A DSP FPGA • All                                    |

|                                                     | Spartan-6 FPGA • XC6SLX4 - XC6SLX75T                                          | Spartan-6 FPGA • All                                         |

| CoolRunner™ XPLA3,<br>CoolRunner-II,<br>XC9500 CPLD | • All                                                                         | • All                                                        |

# **Compatible Third-Party Tools**

Table 2-2: Compatible Third-Party Tools

| Third-Party Tool                                                                                         | Red Hat<br>Linux | Red Hat<br>Linux-64 | SUSE<br>Linux | Windows<br>XP 32-bit | Windows<br>XP 64-bit | Windows-<br>7 32-bit | Windows-<br>7 64-bit |

|----------------------------------------------------------------------------------------------------------|------------------|---------------------|---------------|----------------------|----------------------|----------------------|----------------------|

| Simulation                                                                                               |                  |                     |               |                      |                      |                      |                      |

| Mentor Graphics<br>ModelSim PE/DE/SE<br>(10.2a)                                                          | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Mentor Graphics<br>ModelSim PE (10.1b)                                                                   | N/A              | N/A                 | N/A           | Yes                  | Yes                  | Yes                  | Yes                  |

| Mentor Graphics<br>Questa Advanced<br>Simulator(10.1b)                                                   | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Cadence Incisive<br>Enterprise Simulator<br>(IES) (12.20.016)                                            | Yes              | Yes                 | Yes           | N/A                  | N/A                  | N/A                  | N/A                  |

| Synopsys VCS and<br>VCS MX<br>2(013.06-3*)<br>*- Contact Synopsys<br>for availability of<br>Synopsys VCS | Yes              | Yes                 | Yes           | N/A                  | N/A                  | N/A                  | N/A                  |

| The MathWorks MATLAB® and Simulink® with Fixed-Point Toolbox (2012a, 2012)                               | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Aldec Active-HDL<br>(9.2)                                                                                | N/A              | N/A                 | N/A           | Yes                  | Yes                  | Yes                  | Yes                  |

| Aldec Riviera-PRO<br>(2013.02)                                                                           | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Synthesis                                                                                                | 1                |                     |               | l .                  | 1                    |                      |                      |

| Synopsys<br>Synplify/Synplify<br>Pro (H-2013.03)                                                         | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Mentor Graphics<br>Precision RTL/Plus<br>(2012c)                                                         | Yes              | Yes                 | Yes           | Yes                  | Yes                  | Yes                  | Yes                  |

| Equivalence Checking                                                                                     |                  |                     |               |                      |                      |                      |                      |

| Cadence Encounter<br>Conformal (9.1)                                                                     | Yes              | Yes                 | Yes           | N/A                  | N/A                  | N/A                  | N/A                  |

Note: Support for Aldec simulators is offered by Aldec.

**Note:** Contact Synopsys for availability of Synplify Overlay.

**Note:** Cadence Encounter Conformal Support is for RTL2Gate using Synopsys Synplify only.

## **System Requirements**

This section provides information on system memory requirements, cable installation, and other requirements and recommendations.

## **System Memory Recommendations**

For memory recommendations for the ISE Design Suite tools, see: <a href="http://www.xilinx.com/ise/products/memory.htm">http://www.xilinx.com/ise/products/memory.htm</a>.

#### **Operating Systems and Available Memory**

The Microsoft Windows and Linux® operating system (OS) architectures have limitations on the maximum memory available to a Xilinx program. Users targeting the largest devices and most complex designs may encounter this limitation. The ISE Design Suite has optimized memory and enabled support for applications to increase RAM memory available to Xilinx tools.

#### Windows XP Professional 32-bit

Xilinx applications are enabled to take advantage of the memory increase feature on Windows 32-bit systems. You must then modify Windows setting to get access to this larger memory.

The standard Windows OS architecture limits the maximum memory available to a Xilinx process to 2 Gigabyte (GB). In Windows XP Professional, Microsoft created an option to support the ability of an application to address 3 GB of RAM. Xilinx ISE tools have built-in support for this option. To take advantage of this capability, you must also modify your Windows XP OS to enable this feature, which requires that you modify your boot .ini file by adding a "/3GB" entry to the end of the "startup" line.

Before enabling 3 GB support for Xilinx applications, read the Microsoft Knowledge Base Article #328269 at <a href="http://support.microsoft.com/?kbid=328269">http://support.microsoft.com/?kbid=328269</a>. If you upgrade your computer to Windows XP Service Pack 1 (SP1) and you are using the /3GB switch, Windows might not restart without a patch from Microsoft. See the Xilinx Answer Record 17905 for more information at <a href="http://www.xilinx.com/support/answers/17905.htm">http://www.xilinx.com/support/answers/17905.htm</a>.

Additionally, before making this change, read:

Microsoft Bulletin Q17193

<a href="http://support.microsoft.com/default.aspx?scid=kb;en-us;Q171793">http://support.microsoft.com/default.aspx?scid=kb;en-us;Q171793</a>, which contains information on "Application Use of 4GT RAM Tuning".

Microsoft Bulletin Q289022

<a href="http://support.microsoft.com/default.aspx?scid=kb;en-us;q289022">http://support.microsoft.com/default.aspx?scid=kb;en-us;q289022</a>, which contains instructions for editing your boot.ini file.

#### Linux

For 32-bit Red Hat Enterprise Linux systems, the operating system can use the hugemem kernel to allocate 4 GB to each process. More information can be found on the Red Hat support site: <a href="http://www.redhat.com/docs/manuals/enterprise/">http://www.redhat.com/docs/manuals/enterprise/</a>

## **Cable Installation Requirements**

Platform Cable USB II and Parallel Cable IV are high-performance cables that enable Xilinx design tools to program and configure target hardware.

To install Platform Cable USB II, a system must have at least a USB 1.1 port. For maximum performance, Xilinx recommends using Platform Cable USB II with a USB 2.0 port.

To install Parallel Cable IV, a system must have a parallel port connector and support parallel port communication.

Cables are officially supported on the 32-bit and 64-bit versions of the following operating systems: Windows XP Professional, Windows-7, Red Hat Linux Enterprise, and SUSE Linux Enterprise 11. Additional platform specific notes are as follows:

- Root privileges are required.

- SUSE Linux Enterprise 11: The fxload software package is required to ensure correct Platform Cable USB II operation. The fxload package is not automatically installed on SUSE Linux Enterprise 11 distributions, and must be installed by the user or System Administrator.

- Linux LibUSB support: Support for Platform Cable USB II based upon the LibUSB package is now available from the Xilinx website. See Xilinx Answer Record 29310 at: <a href="http://www.xilinx.com/support/answers/29310.htm">http://www.xilinx.com/support/answers/29310.htm</a>.

For additional information regarding Xilinx cables, see to the following documents:

- USB Cable Installation Guide (UG344): <a href="http://www.xilinx.com/support/documentation/user\_guides/ug344.pdf">http://www.xilinx.com/support/documentation/user\_guides/ug344.pdf</a>

- Platform Cable USB II Data Sheet (DS593): http://www.xilinx.com/support/documentation/data\_sheets/ds593.pdf

- Parallel Cable IV Data Sheet (DS097): http://www.xilinx.com/support/documentation/data\_sheets/ds097.pdf

## **Equipment and Permissions**

The following table lists related equipment, permissions, and network connections.

Table 2-3: Equipment and Permissions Requirements

| Item                  | Requirement                                                                                                                                                                                         |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Directory permissions | Write permissions must exist for all directories containing design files to be edited.                                                                                                              |  |  |

| Monitor               | 16-bit color VGA with a minimum recommended resolution of 1024 by 768 pixels.                                                                                                                       |  |  |

| Drive                 | You must have a DVD-ROM for ISE Design Suite (if you have received a DVD, rather than downloading from the web).                                                                                    |  |  |

| Ports                 | To program devices, you must have an available parallel, or USB port appropriate for your Xilinx programming cable. Specifications for ports are listed in the documentation for your cable.        |  |  |

|                       | <b>Note:</b> Installation of the cable driver software requires Windows XP Pro SP1 (or later), or Windows-7. If you are not using one of these operating systems, the cables may not work properly. |  |  |

**Note:** X Servers/ Remote Desktop Servers, such as Exceed, ReflectionX, and XWin32, are not supported.

#### **Network Time Synchronization**

When design files are located on a network machine, other than the machine with the installed software, the clock settings of both machines must be set the same. These times must be synchronized on a regular basis for continued proper functioning of the software.

# Download and Installation

This chapter explains how to download and install the Integrated Software Environment (ISE®) Design Suite tools, which includes ChipScope™ Pro logic analyzer, Embedded Tools (including Embedded Development Kit (EDK) and standalone Software Development Kit (SDK)), System Generator for DSP, and PlanAhead™ design tool.

## **Downloading the ISE Design Suite Tools**

This section explains how to download the ISE Design Suite tools.

To begin, open an internet browser and navigate to the Xilinx Download Center at <a href="http://www.xilinx.com/support/download/index.htm">http://www.xilinx.com/support/download/index.htm</a>.

Most files in the Xilinx® Download Center are downloaded using the Akamai download manager. For the optimum download experience:

- Allow pop-ups from entitlenow.com

- Set security settings to allow for secure and non-secure items to be displayed on the same page

- Allow the Akamai download manager to run Java processes

To download the Xilinx Design Tools:

- 1. Select the **Design Tools** tab in the web page.

- 2. Under the Version heading, click the version of the tools you want to download.

- 3. Click the link for the installer you want to download.

**Note:** Beginning in 14.3, there is a Multiple File Download option. This option contains four smaller downloadable archives and is the recommended option for customers who cannot reliably download the larger install files. This option requires that all four files listed in the section be downloaded prior to running the installer. See Important Information area of the web page section for more details.

**Note:** For 14.x, the installers under the Xilinx Design Tools heading also contain the standalone selections for the Software Development Kit and Lab Tools. Depending on your use case, you may not need to download these separate installation programs if you are downloading the Xilinx Design Tools installers.

4. Enter your User ID and Password to log into your Xilinx account.

Note: If you do not have a Xilinx account, you must create to download products.

An address verification screen appears.

- 5. After the current address is correct, click Next.

- 6. The Akamai download manager launches in your browser to complete the download process. If you have trouble using the Akamai download manager, look on the download page under "Having Trouble Downloading?". You can follow a link to a Xilinx Answer Record which allows you to obtain the tools without using the download manager.

Most files in the Xilinx Download Center are packaged using TAR methods. You will need to use software from a third party provider to unpack them. Consult your IT department for assistance. Commonly used tools for TAR files are 7-ZIP, GNU built-in tools, WinZIP, and WinRar. These tools are licensed solely by each respective developer, and not by Xilinx. Xilinx hereby disclaims any warranties, express or implied, including warranties of merchantability, fitness for a particular purpose, or non infringement with respect to these suggested software tools.

# Installing the ISE Design Suite Tools: Overview for All Platforms

This section explains the installation process for all platforms for the ISE Design Suite tools. Before installation:

- Disable anti-virus software to reduce installation time.

- Make sure you have the necessary privileges for the system on which the design tools

will be installed. Some components, such as programming cable device drivers, require

administrator-level permissions.

- Close all open programs before you begin installation.

- Make sure your system meets the requirements described in Chapter 2, Architecture Support and Requirements.

- If EDK is installed, make sure the installation is in a directory structure that does not contain spaces.

**Note:** The Xilinx Design Tools installers do not set global environment variables, such as XILINX, on Windows. To find out if this affects the way you run Xilinx design tools, see "Platform-Specific Installation Instructions."

• When running xsetup.exe from a 32-bit machine onto the network location of a 64-bit machine, the tools install the 32-bit executables onto that machine and not the 64-bit executables.

# **Platform-Specific Installation Instructions**

This section provides platform-specific instructions for installing the ISE Design Suite tools.

#### **Microsoft Windows Installation**

How you start installation depends on how you obtained the installation program. See Downloading the ISE Design Suite Tools for details on your options.

- If you downloaded an installation file, decompress that file and run xsetup.exe.

- If you downloaded the installation file in multiple parts, decompress the file with the .tar

extension and run xsetup.exe. You should not decompress any other files

- If you received a Xilinx Design Tools DVD, load the DVD. If the auto-run feature of your DVD drive is enabled, the setup program should start automatically. If it does not, browse to the DVD in Windows Explorer and run xsetup.exe.

#### **Linux Installation**

The method of starting the installation depends on how you have obtained the installation program. See Downloading the ISE Design Suite Tools for details on your options.

- If you have downloaded an installation file, decompress that file and run the xsetup program contained therein.

- If you downloaded the installation file in multiple parts, decompress the file with the .tar extension and run xsetup. You should not decompress any other files.

- If you have ordered and received a Xilinx Design Tools DVD, load the DVD. Click the setup file in your file manager, or browse to the root of your DVD drive and type ./xsetup.

## **Installation Flow**

The following section describes important screens you will encounter during the installation process.

**Note:** For each of the following installation steps, click the text of any item with a check box next to it to obtain more information. Information is displayed in the "Description" area near the bottom of the screen.

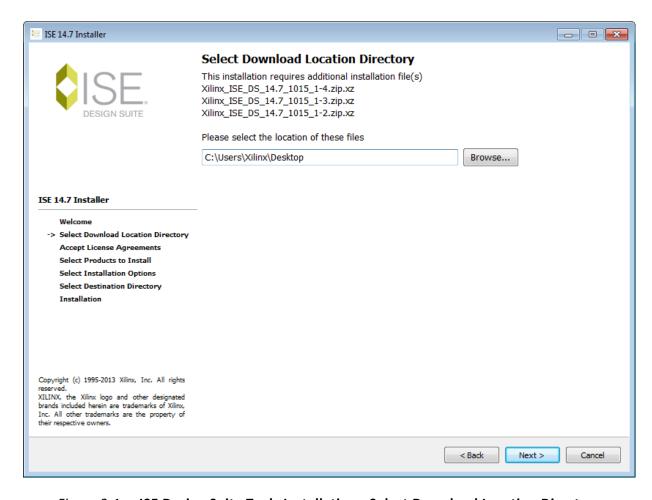

## **Select Download Location Directory**

This step applies to users who downloaded the installation files in multiple archive files. If you downloaded a single image, skip to Accepting Software Licenses.

This screen lists all the required additional installation files to complete the installation. Users will need to point the tool to a location that contains these files. All the required files should be in the same directory. After the correct files have been identified, the installer checks the integrity of these files to ensure archives are not corrupt. This process might take a few minutes to complete.

Figure 3-1: ISE Design Suite Tools Installation - Select Download Location Directory

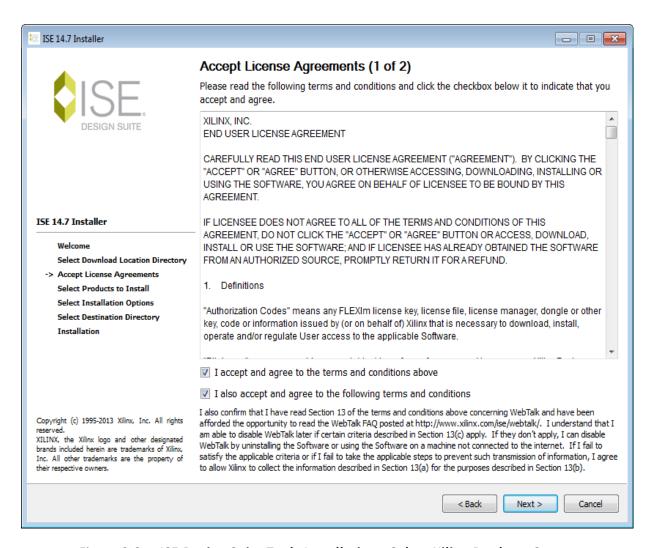

## **Accepting Software Licenses**

You must accept two software license agreements. On each Accept Software Agreement screen:

- 1. Click I accept and agree to the terms and conditions above.

- 2. Click Next.

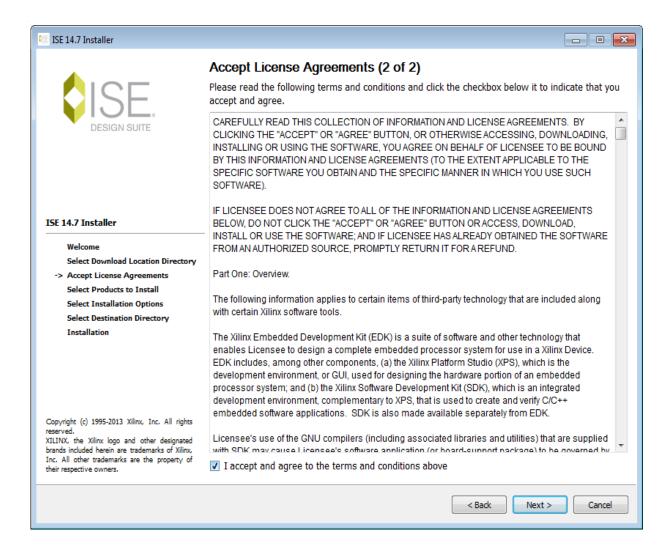

#### Select Xilinx Products to Install

Select the Xilinx products you want to install.

Figure 3-2: ISE Design Suite Tools Installation - Select Xilinx Products Screen

**Note:** The ISE WebPACK™ tool product installer installs both ChipScope Pro analyzer and the Embedded Development Kit. Although installed, these applications will require a separate license to run.

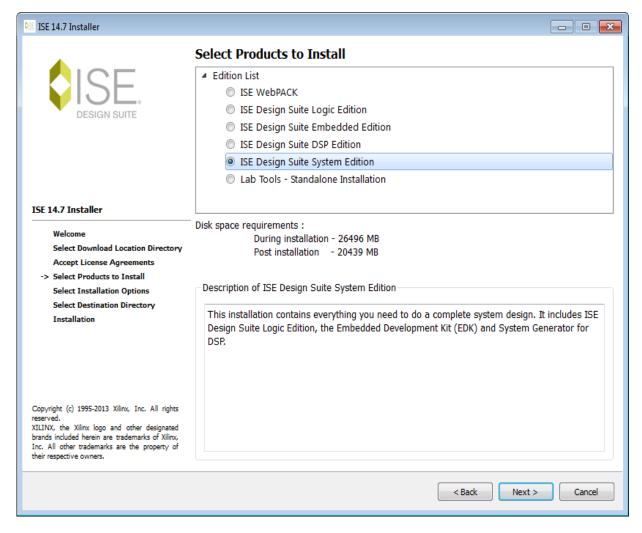

## **Select Installation Options**

There are several optional installation steps during installation. If selected, these options install toward the end of the installation process, after the main installation has completed.

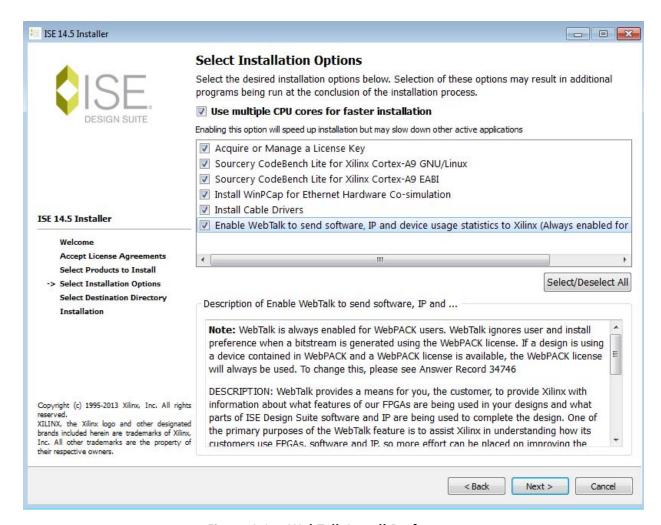

Select Xilinx Installation Options from the following screen.

Figure 3-3: ISE Design Suite Tools Installation - Installation Options

**Note:** WebTalk is always enabled when using the WebPACK tool. If you install an Edition product, the installer allows you to deselect Enable WebTalk. However, if a WebPACK tool license is used to process the design, Enable WebTalk is ignored. Click the Enable WebTalk item, in the installer, and read the description box for full details.

## **Select Destination Directory**

In the Select Destination Directory screen, select the directory in which to install the design tools. Enter a name for the Program Folders list. The installer displays a level of hierarchy underneath the installation path you specify. The name of the directory varies depending on the type of product you are installing. Any Editors or WebPACK tool installation creates a directory named \ISE\_DS. Lab tool standalone installations create \LabTools. SDK standalone installations create \SDK. This ensures Edition and Standalone tools can coexist properly on your hard drive.

Figure 3-4: ISE Design Tools Suite Installation - Select Destination Directory

## **Installation Options Summary**

The Installation Options Summary screen summarizes the tools, products, and options to be installed. To begin installation, click **Install**.

Near the end of the installation, the Xilinx License Configuration Manager opens by default. Follow the instructions in the Manager to obtain or locate a license file.

**Note:** EDK tools require the Cygwin tools distributed by RedHat. A copy of these tools is distributed with the EDK installation.

#### **Setting Environment Variables**

#### **Microsoft Windows Clients**

When installation is complete, the installation program creates an environment variable batch file. All appropriate Desktop and Program Group shortcuts call this file before launching the target application. A shortcut to a command-line prompt which sets the environment has been created. The shortcut is located at Xilinx Design Tools > ISE Design Suite 14.7 > Accessories > ISE Design Suite 32 (or 64) Bit Command Prompt.

To set environment variables in make or script files:

Add <XILINX installation directory>\settings32.bat or settings64.bat to your script. The numbers 32 or 64 corresponds to the bit-width of the operating system installed on the computer.

#### **Linux Clients**

When installation is complete, the installation program creates an environment variables file.

- 1. Go to the XILINX installation directory.

- 2. Type either source settings32.(c) sh or source settings64.(c) sh, as required for your shell.

**Note:** 32-bit ISE tools do not work with 64-bit EDK. 64-bit EDK does not work with 32-bit ISE tools.

To set your environment variables manually or from within your setup script, Xilinx recommends you copy the settings from the appropriate file for your operating system, as listed above. Xilinx environment variables settings are specific to each operating system platform.

## **USB FLEXid Dongle Driver Installation**

If you purchased a USB FLEXid Dongle for use with the Windows operating systems, you must install the appropriate driver before creating a FLEXnet license for use with it.

- 1. Install the Xilinx Design Tools first. This installation contains the installer files for the USB FLEXid dongle driver.

- 2. Run FLEXId\_Dongle\_Driver\_Installer.exe from <Xilinx Installation Directory>\14.7\ISE DS\ISE\bin\nt.

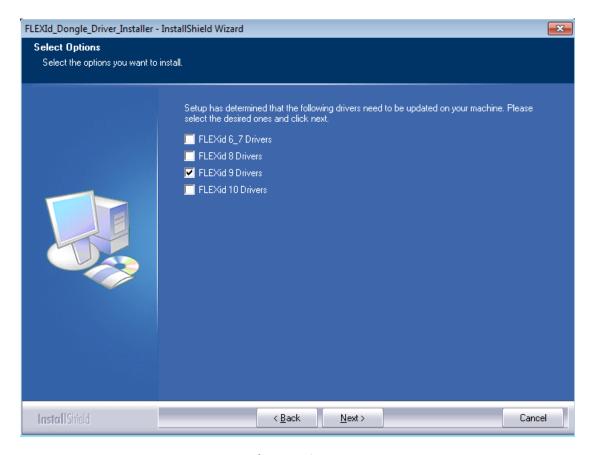

- 3. On the Select Options screen, be sure only **FLEXid 9 Drivers** is checked.

Figure 3-5: Select Options Screen

4. Click **Next** twice. The driver installs.

After installation, you will need to reboot to ensure the dongle operates correctly.

## **Network Installations**

Installing to a network location provides a way for client machines to access the design tools by pointing to it on the network drive. To run the design tools on the network, the client machines must be set up correctly to ensure the environment variables, registry, and program groups all point to the network. The following sections describe the procedure for network setups.

#### **Linux Clients**

Each user must source settings32.(c) sh or settings64.(c) sh (whichever is appropriate for your operating system) from the \$XILINX area in which the design tools are installed. This points the Xilinx environment variable, path, and LD\_LIBRARY\_PATH to the installed location.

To run the design tools from a remotely installed location, run an X Windows display manager, and include a DISPLAY environment variable. Define DISPLAY as the name of your display. DISPLAY is typically unix:0.0. For example, the following syntax allows you to run the tools on the host named bigben and to display the graphics on the local monitor of the machine called mynode:

```

setenv DISPLAY mynode:0.0

xhost = bigbenPC Clients

```

#### **Microsoft Windows Clients**

- 1. Install design tools to a PC network server. Make sure your users know the location of the design tools and have access to the installation directory, and they have Administrator privileges for the following steps.

- 2. From the local client machine, browse to the following directory: network\_install\_location\common\bin\nt and run the program shortcutSetup.bat.

- 3. Running this program sets up the Windows settings batch files and Program Group or Desktop shortcuts to run the Xilinx tools from the remote location.

- 4. From the client machine, launch the ISE tools by clicking the **Program Group** or **Desktop** shortcuts, or by running the applications on the network drive.

#### **Installing to a Mounted Network Drive**

Xilinx design tools are designed to be installed in a directory under ROOT (typically C: \Xilinx). The installer normally presents this option when installing to a local driver. When installing to a mounted network drive, if a subdirectory is not defined, it appears to the Installer as if it is installing to a ROOT directory.

To work around this issue, define your target installation directory as "\Xilinx" under the network mount point (For example: "N:\Xilinx").

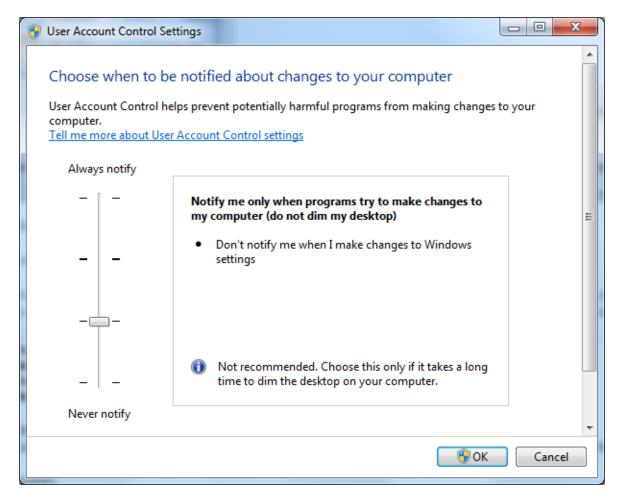

Windows 7 default security levels do not allow you to select remote mapped drives as an Administrator. To install Xilinx Design Tools on remote mapped drives, you need to change your account control settings using the steps below:

- Open the Windows Control Panel, from the Windows Start menu, and select 'User Accounts'. If your Control Panel Uses 'Category View', you will need to click 'User Accounts' on two successive screens

- 2. Click 'Change User Account Control settings' and allow the program to make changes

- 3. Click and slider the slider-bar down to the second to lowest setting (as seen in the below figure). Click OK.

Figure 3-6: User Account Control Settings

Xilinx recommends you revisit this procedure to restore your settings to their previous state after installation.

**Note:** You will not be able to browse to remote mapped drives using the Xilinx installer. You will need to manually type in your installation path which contains a mapped network drive.

# **Obtaining Quarterly Releases**

Xilinx releases quarterly versions of the ISE Design Suite tools throughout the year. Each quarterly version contains device support updates, new features and bug fixes. The following sections describe how to obtain updates through XilinxNotify and the Download Center.

## XilinxNotify

The XilinxNotify tool is the preferred method of obtaining updates. It provides the following features:

- Compares the latest version of Xilinx design tools updates available on <a href="http://www.xilinx.com/support">http://www.xilinx.com/support</a> with what you have installed, and notifies you if a newer version is available.

- Provides a Download button allowing you to log in to the Xilinx Download Center. Once you log in, the download of your selected product begins.

- XilinxNotify can be run in any of the following ways:

- Automatic periodic checks at ISE Project Navigator start-up time.

- Select Help > Check for Updates from Project Navigator.

- Select Start > All Programs > Xilinx Design Tools > ISE Design Tools 14.7 > Accessories >

Check for Updates.

- Type xilinxnotify in a Linux shell.

**Note:** Select **Edit > Preferences** in Project Navigator to control the frequency of the automatic periodic checks.

#### XilinxNotify Network Installations

By default, the Automatically check for updates option at Project Navigator startup is enabled on the machine used to install the ISE tools to the network location. All clients pointing to this network location have this option disabled by default. Client users have the option of enabling this option (**Edit > Preferences > XilinxNotify** from Project Navigator) and also running manual checks.

**Note:** To perform an update installation, you must have write permissions for the \$XILINX installation directory.

#### **Download Center**

Quarterly releases for all platforms are regularly made available on the Download Center at:

http://www.xilinx.com/support/download/index.htm

# **Uninstalling the ISE Design Suite Tools**

## **Uninstalling on Microsoft Windows**

The following sections describe how to uninstall the ISE Design Suite tools on Microsoft Windows.

To uninstall any Xilinx product, select the **Uninstall** item from that product's Start Menu folder. For instance, to uninstall the ISE WebPACK design tools or an ISE Design Suite: Edition, select **Start > All Programs > Xilinx Design Tools > ISE Design Suite 14.7 > Accessories > Uninstall**.

Depending on what you have installed, you may also need to uninstall some ancillary applications, such as WinPcap 4.0 (optional component of DSP Tools).

Before uninstalling, make sure you have moved any project files you want to keep outside your Xilinx installation directory structure, or they will be deleted.

### **Uninstalling on Linux**

To uninstall the Xilinx Design Suite product, you need to remove the Xilinx installation directory from the shell.

# WebTalk

The WebTalk feature helps Xilinx understand how you use Xilinx® FPGA devices, software, and IP. The information collected and transmitted by WebTalk allows Xilinx to improve the features most important to you as part of our ongoing effort to provide products that meet your current and future needs. When enabled, WebTalk provides information on your use of the ISE® Design Suite tools.

# WebTalk Participation

Your participation in WebTalk is voluntary except in the following cases:

- You are using a WebPack™ license.

- You are using pre-release software or devices.

In these cases, WebTalk data collection and transmission always occurs, regardless of your preference settings. For all other cases, data is not collected or transmitted if you disable WebTalk.

The table below summarizes WebTalk behavior for data transmission to Xilinx from your post-route design, based on your Xilinx license, WebTalk install preference, and user preference settings.

Table 4-1: WebTalk Behavior for Bitstream Generation or Route Design Flow

| Design Flow                              | License                              | WebTalk Install<br>Preference | WebTalk User<br>Preference | WebTalk Data<br>Transmission to<br>Xilinx |

|------------------------------------------|--------------------------------------|-------------------------------|----------------------------|-------------------------------------------|

| Bitstream<br>Generation/ Route<br>Design | WebPACK<br>(or pre-release software) | lgnored                       | lgnored                    | Yes<br>(Send)                             |

| Bitstream<br>Generation/ Route<br>Design | Logic Edition                        | Enabled                       | Enabled                    | Yes<br>(Send)                             |

Table 4-1: WebTalk Behavior for Bitstream Generation or Route Design Flow

| Design Flow                              | License       | WebTalk Install<br>Preference | WebTalk User<br>Preference | WebTalk Data<br>Transmission to<br>Xilinx |

|------------------------------------------|---------------|-------------------------------|----------------------------|-------------------------------------------|

| Bitstream<br>Generation/ Route<br>Design | Logic Edition | Enabled                       | Disabled                   | No<br>(Do Not Send)                       |

| Bitstream<br>Generation/ Route<br>Design | Logic Edition | Disabled                      | lgnored                    | No<br>(Do Not Send)                       |

**Note:** Webtalk transmits data after PAR for devices which bitstream generation is not enabled and after bitstream generation for devices that support bitstream generation.

# **Setting WebTalk Install Preference**

You can enable or disable WebTalk globally during or after installation as described below. During installation you can enable or disable WebTalk installation options by checking or unchecking the Enable WebTalk to send software, IP and device usage statistics to Xilinx (Always enabled for WebPACK license) checkbox.

Figure 4-1: WebTalk Install Preference

# **Setting WebTalk User Preferences**

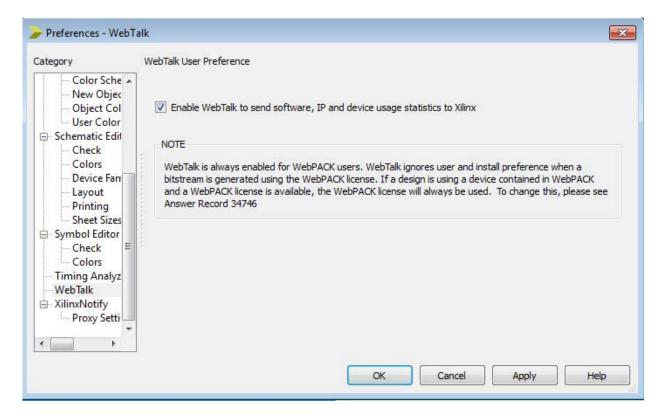

You can enable or disable WebTalk user options from the Project Navigator Preferences graphical user interface (GUI). For more information, go to the <u>Xilinx Design Tools WebTalk</u> page available from the Xilinx website.

You can enable or disable WebTalk user options by selecting **Edit > Preferences** as shown below.

Figure 4-2: WebTalk User Preferences

# Types of Data Collected

WebTalk does not collect your design netlist or any other proprietary information that can be used to reverse engineer your design. The data that Xilinx collects through WebTalk includes:

- Software version

- Platform information (for example, operating system, speed and number of processors, and main memory)

- Unique project ID

- Authorization code

- Date of generation

- Targeted device and family information

For more information on the type of data that is collected, see the Xilinx Design Tools WebTalk page available from the Xilinx website. To see the specific WebTalk data collected for your design, open the usage\_statistics\_webtalk.xml file in the project directory.

You can also open the usage\_statistics\_webtalk.xml file for easy viewing of the data transmitted to Xilinx.

### **Transmission of Data**

WebTalk is invoked after bitstream or route design compilation. WebTalk bundles the collected data in an usage\_statistics\_webtalk.xml file and sends this file to Xilinx by https (hypertext transfer protocol secure) post. Every new compilation for a given design overwrites the previous usage\_statistics\_webtalk.xml file. WebTalk also writes an HTML file equivalent usage\_statistics\_webtalk.html file for easy viewing of the data transmitted to Xilinx. WebTalk also writes to the runme.log file that contains additional information about whether the file was successfully transmitted to Xilinx.

# Obtaining and Managing a License

The Xilinx® Product Licensing Site is an online service for licensing and administering evaluation and full copies of Xilinx design tools and IP products. This chapter describes the FLEXnet license generation functionality of the Product Licensing Site.

## **Accessing the Product Licensing Site**

You can access the Xilinx Product Licensing Site in various ways depending upon the type of license being generated.

- If you purchased products, follow the link included in your order confirmation email. It provides direct access to an account containing your product entitlements.

- To evaluate IP products, go to <a href="http://www.xilinx.com/ipcenter">http://www.xilinx.com/ipcenter</a> and follow the Evaluate link on the IP product page of interest.

- To access the Product Licensing Site directly, go to <a href="http://www.xilinx.com/getlicense">http://www.xilinx.com/getlicense</a>.

You must first register or enter your registration information.

## Sign in to the Xilinx Licensing Site

Note: Xilinx employees should Sign In using their Xilinx ID and password.

Figure 5-1: Xilinx Licensing Sign In Page

You must first sign in. If you already have a Xilinx user account, enter your user ID and password, and then confirm your contact information is current. If you do not have an account, click the **Create Account** button.

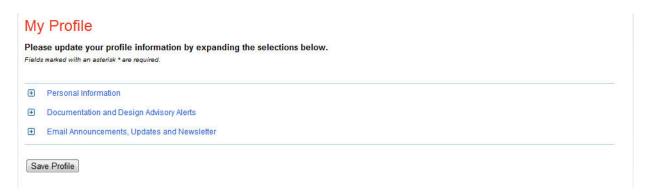

# **Changing Xilinx User Account Information**

It is important to keep your Xilinx User Account up to date. As you change companies, addresses or emails may change.

### **Modifying your Corporate Email Address**

1. Go to www.xilinx.com.

Figure 5-2: Xilinx Website

2. Click **Sign In**.

Figure 5-3: Personal Information

3. Expand Personal Information.

Figure 5-4: Enter New Corporate email Address

- 4. Enter your new corporate email address in the Enter new Corporate email address box.

- 5. Click **Save Profile** button for changes to take effect.

# **Product Licensing Accounts**

When you purchase a design tool edition or IP product from Xilinx, you are purchasing a license to use and receive updates for that product for one year. The license to use Xilinx deign tools and IP products is managed through the use of product entitlements. A product entitlement is the determination of:

- Which product was purchased

- · The number of seats purchased

- The license type (floating or node-locked)

- The product subscription period (product updates are provided throughout the year)

In addition to managing the product entitlements for your purchased design tools and IP, you can also access product entitlements for No Charge or Evaluation products. Full and No Charge licenses have a subscription period of one year. Design tools evaluations are for 30 days, and IP evaluations are for 120 days.

Activating a product entitlement results in one or more license keys being generated by the website. When installed, the license keys enable the use of the design tools and IP that were purchased or are being evaluated. Your product entitlements and resulting license key files are managed in a product licensing account on the Xilinx website.

Product licensing accounts are specific to the individual listed on the Xilinx Software Purchase Order, who is either the end user or administrator of the design tools. All purchases made can be managed in the same product licensing account if a single administrator is named. A company site can have multiple accounts managed by different administrators. The latter is helpful if a site has multiple design teams working on differing projects with different budget pools.

**Note:** A license key can be generated for a product entitlement that has expired; however, it will only enable product releases up to the subscription end date. Applying a product update made available after the subscription end date of your license results in an error.

#### **LogiCORE IP License Generation**

Any LogiCORE™ IP and design tools entitlements you have purchased appear in your list of entitled products when you log into the Product Licensing Site. Licenses for Evaluation and No Charge IP are available on the site in a separate area. Licenses for all your design tools and IP can now be generated in one pass. They are emailed to you in a single license file. IP core FLEXnet licenses now feature more licensing options, such as single or Triple-Redundant Floating Server support, and more host options for node-locked license keys: Ethernet MAC address, Hard Drive Serial Number or USB Dongle ID.

# **User Types and Actions**

There are three user types for the Product Licensing Site: customer account administrator, end user, and evaluation user.

#### **Customer Account Administrator**

An example of a typical customer account administrator is a CAD tools manager. Every product licensing account *must* have at least one customer account administrator. A customer account administrator can manage more than one product licensing account.

The responsibilities as the customer account administrator include:

- Generating node-locked or floating licenses for Xilinx design tools and IP products.

- Adding and removing users from the product licensing account.

- Assigning administrative privileges to other users.

- Ordering product DVDs (if desired).

The original customer account administrator is the Ship To contact identified during the product ordering process. That person receives an email with instructions on how to download and license each purchased product. The customer account administrator must follow the link in the email, to ensure access to the purchased products.

#### **End User**

Adding end users to a product licensing account allows an engineer or design team member the flexibility to manage and generate license keys on their own. The end user may generate license keys for node-locked products entitlements within the account as well as evaluation and "no charge" license keys for design tools and IP products. A customer account administrator can also configure the end user account to allow an end user to generate floating licenses. An end user cannot:

- View or generate floating license keys by default. This privilege may be assigned to them by the customer account administrator.

- View the license keys generated by other users.

- Add or remove other users to or from the product licensing account.

#### **Evaluation User**

Evaluation users can:

- Generate a 30-day free evaluation license key for the Vivado Design Suite: System Edition which includes the ISE® Design Suite: System Edition

- Generate license keys for evaluation and no charge IP products

- Generate a WebPACK™ tool license for the Xilinx Design Tools

- Request a Xilinx Design Tools DVD package with one of the following shipping options:

- Free Shipping (2-4 Weeks)

- Standard (2-3 Days)

- Overnight

**Note:** A customer who is already licensed for a full version of a Xilinx Design Tools product edition can evaluate other Xilinx Design Tools product editions or IP. These product entitlements are made available in the same product licensing account.

All user types can download products electronically and request a Xilinx Design Tools DVD.

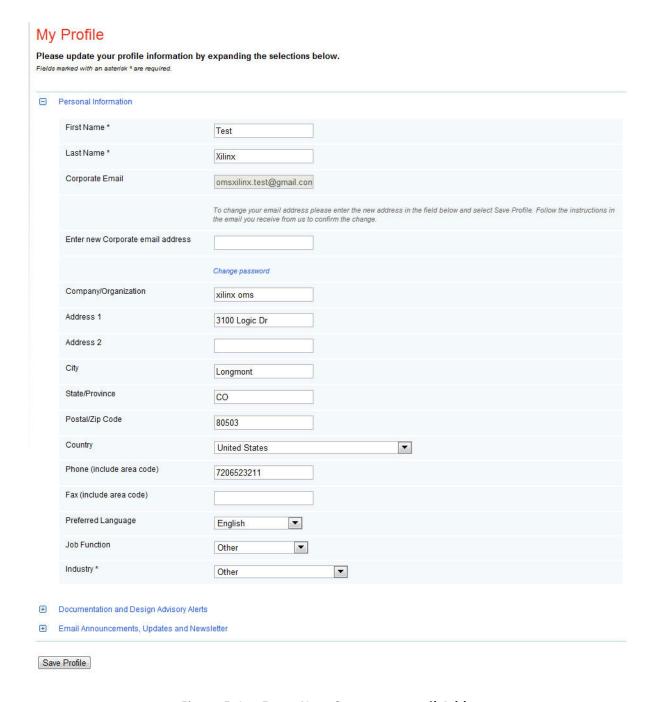

# **Creating a License Key File**

The Create New Licenses tab on the Product Licensing Site is the starting point for license key file generation. The design tools and IP product entitlements you have purchased or wish to evaluate are shown in the product entitlement table.

Figure 5-5: Create New License

# **Selecting Products**

To begin the license generation process for products you have purchased or want to evaluate:

- 1. Select a product licensing account from the Account drop-down list.

- **Note:** This selection is not available if you are entitled to evaluation or free products only.

- 2. Enter product voucher codes for design tools or IP product licenses purchased with kits or for tools purchased from the Xilinx online store (optional).

- 3. Add evaluation or no-charge IP product entitlements to the product entitlement table (optional).

- 4. Make your product selections from the product entitlement table.

The type of product entitlements available are Full (purchased), No Charge, or Evaluation. Full and No Charge licenses have a subscription period of one year. Design tools evaluation is for 30 days. IP evaluations are for 120 days.

Floating and node-locked licenses cannot be combined in the same license key file.

**Note:** A floating license resides on a network server and enables applications to check out a license when they are invoked. At any one time, the number of licenses for simultaneous users is restricted to the number of license seats purchased. A node-locked license allows for the use of a single seat of a product entitlement on a specific machine.

For design tools, available seats represents the number of seats available for licensing over the total number of seats purchased. For IP, seats are managed according to the terms of the site wide license agreement.

Products with a status of Current are within their warranty period. Products with a status of Expired have a warranty period end date that has passed. If seats are available, licenses can be generated for either Current or Expired product entitlements.

The Xilinx Design Tools: System Edition evaluation product entitlement provides access to all the capabilities in the Xilinx Design Tools tool set. This product entitlement is automatically included in your product licensing account.

Product vouchers for design tools and IP product licenses may be shipped with a Xilinx or partner development board or design kit. If you have a product voucher card, you may enter the voucher code on the card into the associated text field and click Redeem Now. This places the corresponding design tools or IP product entitlement in the product entitlement table which you can use to generate a license key.

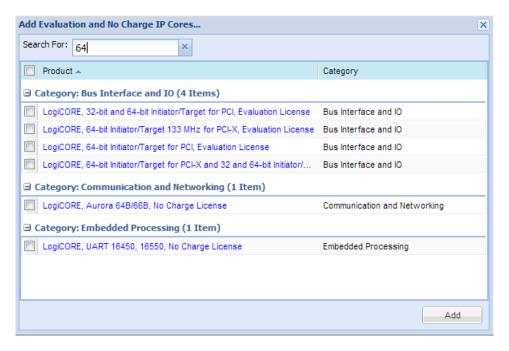

To add Evaluation and No Charge IP to the list of product entitlements, click the **Search Now** button in the Add Evaluation and No Charge IP Cores section of the page. This opens an IP product finder tool.

Figure 5-6: IP Product Selector

**Note:** IP products are typically sold as site licenses that gives the administrator the ability to generate license keys for floating and node-locked license types. End users see only product entitlements for node-locked products. The customer account administrator, or an End User who has been granted Floating License generation status by the administrator, sees product entitlements for both node-locked and floating products.

# **Generating a License**

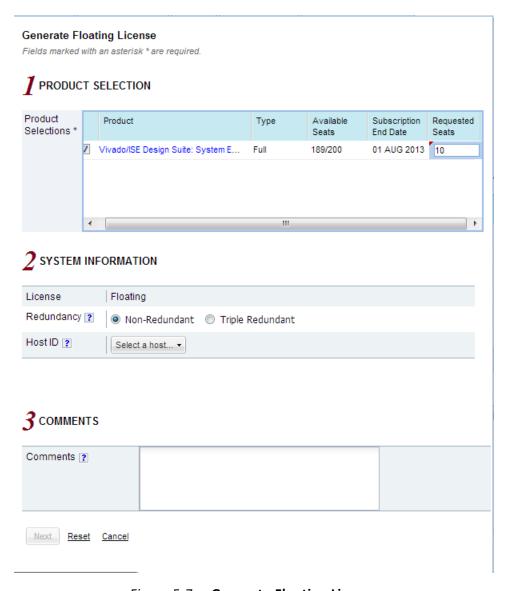

Click the **Generate License** button corresponding to the type of license key file you are generating (floating or node-locked). The license generation form shown below appears.

Figure 5-7: Generate Floating License

To generate floating licenses:

1. Select the number of seats required for each product license.

This is for floating licenses only. All node-locked licenses are for one seat. The number of seats available for a product entitlement is automatically maintained by the system. The Requested Seats field is populated, by default, with the full number of seats remaining on the product entitlement. A product is removed from the product entitlement table if all seats have been activated.

### 2. Enter system information.

System information is pre-populated in the option menu if you arrived at the Product Licensing Site from a link within the Xilinx License Configuration Manager (XLCM).

A redundant server configuration provides a fail over for the license manager software. As long as two of the three servers are running, the license manager can continue to run.

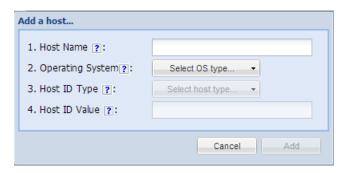

If you do not have pre-populated system information, or if you want to add a different host, select the **Add a host** option.

Figure 5-8: Add a Host

The host ID value uniquely identifies the machine to which your design tools or IP is licensed. You may choose a host ID type to be a MAC address, a hard drive serial number, a dongle ID, or a Solaris host ID.

**Note:** Not all host ID types are supported for all operating systems. The easiest way to obtain your host ID is to run the XLCM on the machine that serves as the license host.

#### 3. Add a comment.

Adding a comment to the license key file makes it easier for an administrator to track the allocation of design tools and IP product entitlements among users.

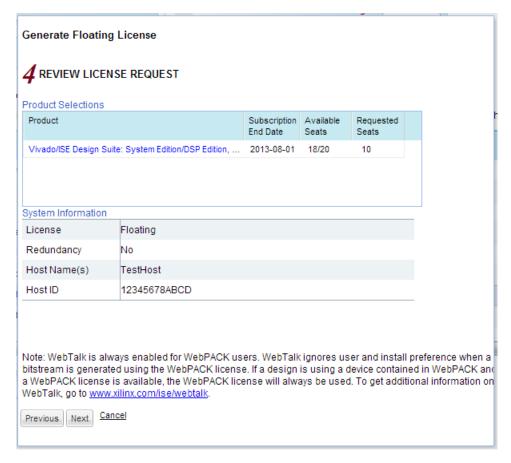

#### Click Next.

The Review License Request form opens.

Figure 5-9: Review License Request

- 5. Review your selections.

- 6. If you are satisfied with your selections, click Next.

### **End User License Agreements**

Xilinx Design Tools and No Charge IP product End User License Agreements (EULAs) are agreed to during the product installation process. If you license IP products, you must accept the terms of the associated IP product EULAs before the license file can be generated.

### Third-Party Licenses

A complete copy of the third-party licenses is located at: <install\_directory>/common/licenses/unified\_3rd\_party\_eula.txt

#### **License Generation Confirmation**

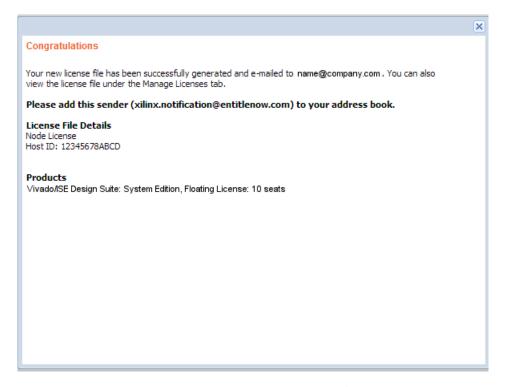

When you finish generating the licenses, you will receive a confirmation message summarizing your licensing activity.

Figure 5-10: License Generation Confirmation

You will also receive a license generation confirmation email. This message contains the generated license key file as an attachment. Add 'xilinx.notification@entitlenow.com' as a trusted sender in your email address book.

If you do not receive your license by email, you can download it directly from the Xilinx Licensing Site. See the Managing License Key Files section for details

# **Managing License Key Files**

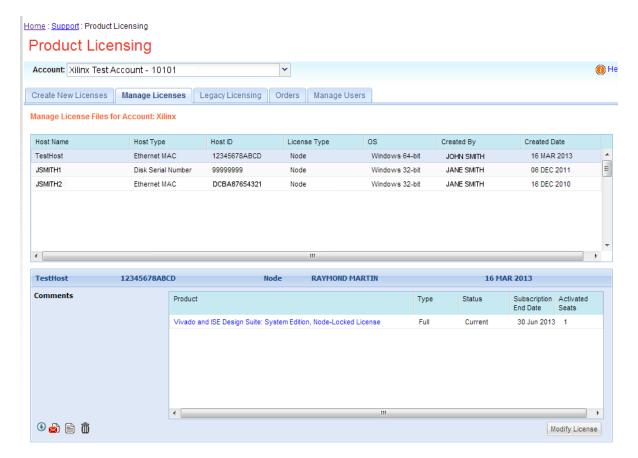

The Product Licensing Site tracks your license key files. Select the Manage Licenses tab to see all license key files for your product licensing account.

Figure 5-11: Manage Licenses

Use the Manage Licenses page, to perform the actions described below.

# **Exploring and Retrieving Your Existing License Key Files**

Information regarding the license key files in your product licensing account are displayed in a split-section view. Click a row in the master view in the top table, to see detailed information about the license key file in the detail view in the bottom table. The detail view table displays:

- A list of product entitlements activated in the key file.

- Comments associated with the key file.

The detail view table gives you the ability to:

- Download If your license file does not arrive via email you may download the license file here. (1)

- Email The license file may be emailed to you or another user.

- View Gives you the ability to view the actual license file.

- Delete Delete the license file. Once a file is deleted it will then become available on the Create New License page and may be regenerated for another host ID.

- View the end user license agreement (IP only).

# **Modifying a License Key File**

To modify an existing license key file, select the license key file in the master view. You can modify a license key file as follows:

### Delete an entire license file and place entitlement back into your account

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file you wish to delete.

- 2. Click the **Trash Can** icon located below and to the left of the license file details.

- 3. Click the **Accept** button to accept the Affidavit of Destruction.

**Note:** This will delete all license seats in the entire license key file and return the entitlements to your account.

### Rehost or change the license server host for a license key file

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file you wish to rehost.

- 2. Click the **Modify License** button. The Modify License screen appears.

- 3. Go to **System Information**.

- 4. Change or add new Host ID and/or Host Name by using the drop-down list and text entry boxes respectively.

- 5. Click the **Next** button twice and then click the **Accept** button to accept the Affidavit of Destruction.

### Activate or add additional seats to an existing licensed product entitlement

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file to which you wish to add seats.

- 2. Click the **Modify License** button. The Modify License screen appears.

- 3. Go to Product Selection.

- 4. For floating licenses, you will be able to change the Requested Seats field and add seats up to the total number of seats available in your entitlement.

- 5. Click **Next** twice. No Affidavit of Destruction is required for adding seats.

### Deactivate or remove seats from an existing licensed product entitlement

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file from which you wish to remove seats.

- 2. Click the **Modify License** button. The Modify License screen appears.

- 3. Go to Product Selection.

- 4. For floating licenses, you will be able to change the Requested Seats field and reduce the number of seats that will be authorized by this license file.

- Click the **Next** button twice and then click the **Accept** button to accept the Affidavit of Destruction.

### Activate or add additional product entitlements to a license key file

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file to which you wish to add features/entitlements.

- 2. Click the **Modify License** button. The Modify License screen appears.

- 3. Go to **Product Selection**.

- 4. Check boxes of any new entitlements you wish to add to this license file.

- 5. Click **Next** twice. No Affidavit of Destruction is required for adding features.

### Deactivate or delete product entitlements from a license key file

- 1. From the Manage Licenses Tab (see Figure 5-11), select the license file to which you wish to add features/entitlements.

- 2. Click the **Modify License** button. The Modify License screen appears.

- 3. Go to **Product Selection**.

- 4. Check boxes of any entitlements you wish to remove from this license file.

- Click the **Next** button twice and then click the **Accept** button to accept the Affidavit of Destruction.

Modifying a key file uses the same input form as when the license key file was created, except additional product entitlements of the same license type (floating or node-locked) are made available for licensing.

If, during any of the modification steps, you receive a message that you have exceeded your number of rehost attempts, email <u>cs\_1@xilinx.com</u> to request additional rehost options.

# **Reclaiming Deactivated Product Entitlements**

A product entitlement is deactivated when one of the following occurs:

- Rehosting or changing the license server host for a license key file.

- Deactivating or removing seats from an existing licensed product entitlement.

- Deactivating or deleting product entitlements from a license key file.

The license generation facility allows the reallocation of the deactivated seats or product entitlements by making the corresponding seats or product entitlements available for activation in the product entitlements table on the Create License page.

Before the reallocation of entitlement occurs, you must first agree to an Affidavit of Destruction. This legal agreement is required to ensure the deactivated product entitlements are no longer being used.

The number of allocation operations is recorded for each user. Administrators are allowed to reallocate product entitlements five times per major release. End users are allowed to reallocate product entitlements three times per major release.

### What Happens to Your License Key File

For each product entitlement activated, a FLEXnet increment line and corresponding package line is added to the license key file. When a license key file is modified to activate (add) seats for an existing or new product entitlement, additional increment or package lines are added to the license key file.

When a license key file is rehosted or is modified to deactivate (delete) seats or product entitlements, the corresponding increment lines are regenerated or removed from the modified license key file.

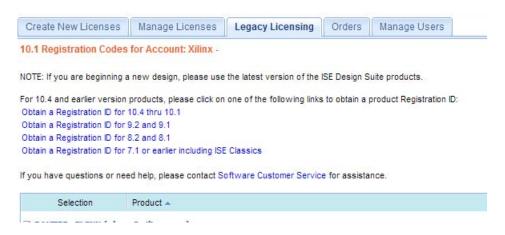

# **Legacy Licensing**

If you wish to obtain a license for Releases 10.1 or earlier, click the **Legacy Licensing** tab.

Figure 5-12: Legacy Licensing

Then complete the following steps for the respective versions:

### 10.1 and Prior Versions

- 1. Select the version you desire. You will be prompted to verify your contact information.

- 2. Fill out the requested form with the required information to receive your registration IDs. Your registration ID will be displayed on the screen and emailed for your records.

- 3. Go to the Xilinx download center, click the **Archive** link under the **Version** column on the left side of the page to select the product you desire.

- 4. During the download process you will be prompted to insert your registration ID to complete the download process.

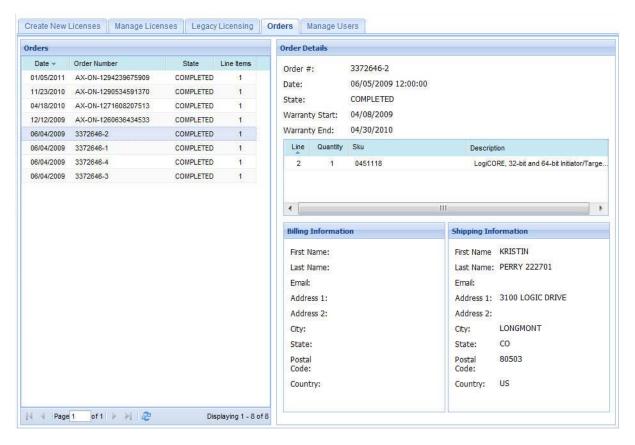

# **Understanding Your Tool and IP Orders**

The Orders tab will display information regarding the purchasing orders that created the entitlements you see in this account.

Figure 5-13: Order Information

- Xilinx order numbers are listed on the left panel of the screen.

- Order details populate on the right panel of the screen when you highlight specific order.

- You may only select one order at a time.

- The order's shipping address information is visible even when product is delivered electronically.

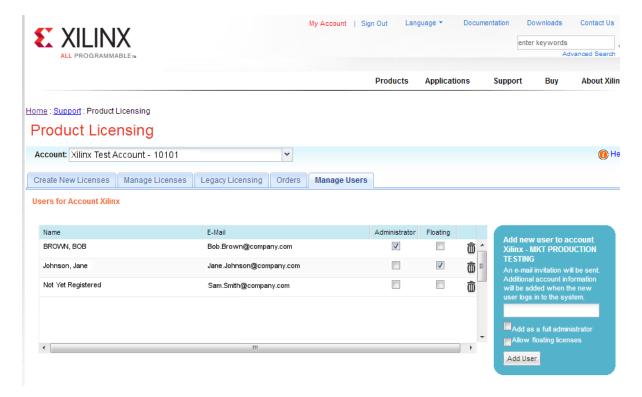

# Managing User Access to Product Licensing Account

The responsibility of administering a product licensing account may be transferred or shared with another user. The ability to add or remove users from a product licensing account is managed under the Manage Users tab.

Figure 5-14: Manage Users

### **Adding Users**

To add a user to your product licensing account:

- Type in the corporate email address of the new user.

- Check Add as a full administrator, to grant the new user customer account administrative privileges. Check Allow Floating Licenses, to grant the new user the ability to generate Floating Licenses, but not have full administrative privileges.

**Note:** The email address you provide must be the same email address the user supplied or supplies when creating their Xilinx account. If not, you may not be properly recognized when logging in.

If you have already logged into the Product Licensing Site, your name appears in the user list. If the user has never been to the site, the words Not Yet Registered appears in the space for their name. Once the user has signed in, their name is filled in.

In some instances, a customer account administrator may wish to have design team members administer license key files for their own use. By leaving both Add as full administrator and Allow Floating Licenses check boxes unchecked, the user is granted the following restricted privileges:

- Can generate node-locked license keys only.

- Can view and modify only those license key files they generated for themselves.

Cannot manage users.

If you check Allow Floating Licenses only, the restriction on node-locked keys is lifted, but the others remain. You cannot check both boxes because it is not allowed. Full administrators already have floating license generation capability.

### **Removing Users**

To remove administrative or floating license generation privileges from a user, uncheck the **Administrator** or **Floating** check box for that user.

To remove a user from a product licensing account, click the **Trash Can** icon for that user.

# **Installing Your License Key File**

The following subsections describe installing different types of licenses.

### **Node Lock License Installation**

After generating a license file, you will receive an e-mail from 'xilinx.notification@entitlenow.com'.

- 1. Save the license file attached to the e-mail to a temporary directory on your local system.

- 2. Run the Xilinx License Configuration Manager:

- For Windows: Select Start > All Programs > Xilinx Design Tools 14.7 > Accessories > Manage Xilinx Licenses.

- For Linux: Type xlcm in a command-line shell.

- 3. Click **Copy License** at the top of the Manage Xilinx Licenses tab.

- 4. Browse to your license file (Xilinx.lic) and click Open.

- 5. This copies the license file to the C:\.Xilinx (Windows) or <Home>/.Xilinx directory of your computer where it will be automatically found by the Xilinx tools.

- 6. When the Copy License operation is complete, the table on the Manage Xilinx Licenses tab is updated with licensing information from the license file.

- 7. Click **Close** to exit the Xilinx License Configuration Manager.

# **Floating License Installation on Servers**

For existing FLEXnet license servers, a common practice is to copy the contents of the license file, mailed from 'xilinx.notification@entitlenow.com', into the existing license file on your FLEXnet server.

**Note:** Restart the floating license server to enable the Xilinx licenses.

### For New License Servers

1. Download the appropriate Xilinx FLEXnet license utilities for your server's operating system from the Xilinx Download Center:

http://www.xilinx.com/download/index.htm

- 2. Unzip these utilities into a destination directory. Xilinx recommends you place this directory into your application search path.

- 3. Once the FLEXnet utilities are installed, run the following commands to start the floating license server:

- Linux

- <Server Tool directory>/bin/lin/lmgrd -c <path\_to\_license>/Xilinx.lic -l

<path\_to\_license>/log1.log

- <Server Tool directory> bin/lin64/lmgrd -c <path\_to\_license>/Xilinx.lic -l <path\_to\_license>/log1.log

- Windows

- < Server Tool directory>\bin\nt\lmgrd -c <path\_to\_license>\Xilinx.lic -l

<path\_to\_license>\log1.log

- < Server Tool directory>\bin\nt64\lmgrd -c <path\_to\_license>\Xilinx.lic -l

<path\_to\_license>\log1.log

# **Client Machines Pointing to a Floating License**

- 1. Run the Xilinx License Configuration Manager (XLCM).

- 2. Click the Manage Xilinx Licenses tab.

- 3. On the Manage Xilinx Licenses tab, enter the network path to the license server in the port@server format into the XILINXD\_LICENSE\_FILE field. Click **Set**. The default Xilinx port number is 2100.

- 4. For Linux operating systems, licensing environment variables cannot be set using the Xilinx License Configuration Manager (XLCM). The environment variable fields are read only, and they are grayed out and there are no Set buttons. The environment variable must be set using the appropriate shell and commands.

# Technical Support and Documentation

# **Known Issues**

ISE® Design Suite Tools Known Issues can be found at the following Xilinx® Answer Record: http://www.xilinx.com/support/answers/46491.htm.

# **Support Site**

For general technical questions, visit the Xilinx Product Support and Documentation site at <a href="http://www.xilinx.com/support/">http://www.xilinx.com/support/</a>, where you can search the Answers Database or utilize other self-support features such as:

- Download Center, http://www.xilinx.com/support/download/index.htm

- Xilinx User Community Forums, http://forums.xilinx.com

- Free Design Training Videos, http://www.xilinx.com/training/free-video-courses.htm

If you cannot resolve your issue using our online resources, you can contact Xilinx Technical Support directly at <a href="http://www.xilinx.com/support/techsup/tappinfo.htm">http://www.xilinx.com/support/techsup/tappinfo.htm</a>.

# **Customer Training**

Xilinx hands-on training programs provide you with the foundational knowledge necessary to begin designing right away. These programs target both engineers new to FPGA technology and experienced engineers developing complex connectivity, digital signal processing, or embedded solutions.

For more information on training courses, free on-demand training, live online training, and upcoming events, visit the Xilinx Training website, <a href="http://www.xilinx.com/support/education-home.htm">http://www.xilinx.com/support/education-home.htm</a>.

# **Documentation**

### **Context-Sensitive Help**

Context-sensitive online Help is available for most ISE Design Suite tools that are available with a graphical user interface (GUI). From Project Navigator, select **Help > Help Topics** to access the online Help or press **F1**.

### **Software Manuals**

Detailed software manuals about the Xilinx Design Tools and command-line functions are found on xilinx.com. To locate the software manuals on the website:

- 1. Go to the Documentation Center, http://www.xilinx.com/support.

- 2. Click the **Design Tools** tab.

- 3. Click the **ISE Design Suite** category and then select version, such as ISE Design Suite 14.7, or click the **See All ISE Design Suite Documentation** link.

# **Xilinx Glossary**

For a glossary of technical terms used in Xilinx documentation, see: http://www.xilinx.com/company/terms.htm.

# **Licenses and End User License Agreements**

The third-party licenses govern the use of certain third-party technology included in and/or distributed in connection with the Xilinx design tools. Each license applies only to the applicable technology expressly governed by such license and not to any other technology. You must accept the terms of the End User License Agreements (EULAs) for Xilinx design tools and third-party products before license files can be generated.

To view the third-party license details and EULA, see <a href="http://www.xilinx.com/cgi-bin/docs/rdoc?v=14.7;d=ug763\_tplg.pdf">http://www.xilinx.com/cgi-bin/docs/rdoc?v=14.7;d=ug763\_tplg.pdf</a>.

To view the Xilinx design tools license details and EULA, see <a href="http://www.xilinx.com/cgi-bin/docs/rdoc?v=14.7;d=end-user-license-agreement.pdf">http://www.xilinx.com/cgi-bin/docs/rdoc?v=14.7;d=end-user-license-agreement.pdf</a>.

# Older Release Notes

# ISE Design Suite 14.6

### What's New

### **Device Support**

The following devices are production ready:

- Zyng®-7000

- 7Z010 and 7Z020

- Defense Grade Zynq-7000Q

- 7Z010, 7Z020 and 7Z030

- Defense-Grade Virtex-7Q

- VX690T and VX980T

- Defense-Grade Artix-7Q

- A100T and A200T

- XA Artix®-7

- A100T

# **Device Support for ChipScope Pro and iMPACT**

7 Series XQ package & speed grade changes

### **Important Information**