# System Cache v5.0

# **LogiCORE IP Product Guide**

Vivado Design Suite

PG118 (v5.0) August 6, 2021

# **Table of Contents**

| Chapter 1: Introduction               |     |

|---------------------------------------|-----|

| Features                              |     |

| IP Facts                              |     |

| Chapter 2: Overview                   | 6   |

| Navigating Content by Design Process  |     |

| Applications                          |     |

| Unsupported Features                  |     |

| Licensing and Ordering                |     |

| Chapter 3: Product Specification      | 18  |

| CCIX RA Master Port Cache Coherency   |     |

| CHI RN Master Port Cache Coherency    | 19  |

| Address Translation Service and Cache | 21  |

| AXI Master                            | 23  |

| ACE Master Port Cache Coherency       | 25  |

| Optimized Ports Cache Coherency       | 25  |

| Exclusive Monitor                     | 26  |

| Cache Memory                          | 26  |

| Error Handling                        | 27  |

| Non-Secure Handling                   | 29  |

| Control and Statistics                | 30  |

| Standards                             | 32  |

| Performance                           | 33  |

| Resource Use                          | 38  |

| Port Descriptions                     | 39  |

| Register Space                        | 43  |

| Chapter 4: Designing with the Core    | 98  |

| System Cache Design                   | 98  |

| Transaction Properties                |     |

| General Design Guidelines             | 113 |

| Back-Door DMA                                      | 119 |

|----------------------------------------------------|-----|

| Clocking                                           | 121 |

| Resets                                             | 122 |

| Protocol Description                               | 122 |

| Chapter 5: Design Flow Steps                       | 129 |

| Customizing and Generating the Core                |     |

| Constraining the Core                              | 159 |

| Simulation                                         | 159 |

| Synthesis and Implementation                       | 160 |

| Appendix A: Upgrading                              | 161 |

| Migrating to the Vivado Design Suite               |     |

| Upgrading in the Vivado Design Suite               |     |

| Functionality Changes                              |     |

| Port and Parameter Changes                         |     |

| Appendix B: Debugging                              | 165 |

| Finding Help on Xilinx.com                         |     |

| Debug Tools                                        |     |

| Simulation Debug                                   |     |

| Hardware Debug                                     |     |

| Interface Debug                                    |     |

| Appendix C: Additional Resources and Legal Notices | 172 |

| Xilinx Resources                                   |     |

| Documentation Navigator and Design Hubs            |     |

| References                                         |     |

| Revision History                                   |     |

| Please Read: Important Legal Notices               |     |

|                                                    |     |

# Introduction

The LogiCORE™ System Cache IP core provides system level caching capability to an AMBA® AXI4 system.

#### **Features**

- Support for Cache Coherent Interconnect for Accelerators (CCIX®) Request Agent (RA) coherency protocol with one port and one link

- Support for CHI interface with one Request Node (RN)

- Address Translation Cache (ATC) with the PCIe® Address Translation Service (ATS) protocol

- Dedicated AXI4 slave ports for a MicroBlaze<sup>™</sup> processor

- Up to 16 generic AXI4 slave ports for other AXI4 masters, limited to four ports with CCIX master coherency

- Up to 16 generic AXI4 slave ports for other AXI4 masters

- Optional cache coherency on dedicated MicroBlaze processor ports with AXI Coherency Extension (ACE)

- Optional support for exclusive access with non-coherent configuration

- Optional cache coherency on master port for Zynq® UltraScale+™ MPSoC connection

- Optional support for Non-Secure transactions

- Optional support for AXI error handling

- AXI4 master port connecting the external memory controller

- Highly configurable cache—2 or 4 set associative cache of up to 4 MB in size

- Optional AXI4-Lite Statistics and Control port

- Supports up to 64-bit AXI4 address width

- Optional support for 64-bit AXI4 Virtual Address via ATS and PRI over PCIe

- Optional support for PCle Advanced Error reporting (AER) error handling, when ATS is in use

# **IP Facts**

| LogiCORE™ IP Facts Table             |                                                                                                            |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------|--|

|                                      | Core Specifics                                                                                             |  |

| Supported Device Family <sup>1</sup> | UltraScale+™ Virtex® UltraScale+™ HBM UltraScale™ Zynq®-7000 SoC Zynq® UltraScale+™ MPSoC 7 series Versal™ |  |

| Supported User Interfaces            | AXI4, ACE, AXI4-Lite, AXI4-Stream (ATS), CXS (CCIX), CHI                                                   |  |

| Resources                            | Performance and Resource Use web page                                                                      |  |

| Provided with Core                   |                                                                                                            |  |

| Design Files                         | Vivado® RTL                                                                                                |  |

| Example Design                       | See the CCIX lounge and the Versal CCIX lounge (registration required)                                     |  |

| Test Bench                           | Not Provided                                                                                               |  |

| Constraints File                     | Not Provided                                                                                               |  |

| Simulation Model                     | Not Provided                                                                                               |  |

| Supported S/W Driver                 | N/A                                                                                                        |  |

|                                      | Tested Design Flows                                                                                        |  |

| Design Entry                         | Vivado® Design Suite                                                                                       |  |

| Simulation                           | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                                |  |

| Synthesis                            | Vivado Synthesis                                                                                           |  |

| Support                              |                                                                                                            |  |

| Release Notes and Known Issues       | Master Answer Record: 54452                                                                                |  |

| All Vivado IP Change Logs            | Master Vivado IP Change Logs: 72775                                                                        |  |

| Pr                                   | ovided by Xilinx at the Xilinx Support web page                                                            |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado® IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The System Cache core can be added to an AXI4 system to improve overall system computing performance, for accesses to external memory.

With cache coherency, efficient multi-processor systems can be implemented and the workload distributed between multiple processors or accelerators, with simple and safe data sharing. The coherency is managed on a hardware level with minimal software handling required.

The System Cache core can provide improved system performance for:

- Applications with repeated access of data occupying a certain address range, for example, when external memory is used to buffer data during computations. In particular, performance improvements are achieved when the data set exceeds the capacity of the MicroBlaze™ processor internal data cache.

- Systems with small MicroBlaze processor caches, for example, when the MicroBlaze processor

implementation is tuned to achieve as high frequency as possible. In this case, the increased

system frequency contributes to the performance improvements, and the System Cache core

alleviates the performance loss incurred by the reduced size of the MicroBlaze processor

internal caches.

- Accelerators working on data sets that are shared between multiple accelerators and the Application Processing Unit (APU) in the Zynq<sup>®</sup> UltraScale+™ MPSoC. The cache coherency ensures all participating units can share data safely and efficiently.

- Accelerators working on data sets that are shared between multiple accelerators and a remote PCle<sup>®</sup> host using the Cache Coherent Interconnect for Accelerators (CCIX<sup>®</sup>) cache coherency protocol. The cache coherency ensures all participating units share data safely and efficiently. PCle Address Translation Services, ATS, is provided to give accelerators the possibility to use virtual memory synchronized with the host.

- Accelerators connecting to System Cache in Versal<sup>™</sup> using a CHI connection to the Versal CCIX PCIe Module (CPM) for local coherency. From CPM the coherency domain can be increased to include other devices by utilizing CCIX. ATS with Process Address Space ID (PASID) is used for system wide address translation. This solution provides support for both local and remote memory.

# **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. All Versal™ ACAP design process Design Hubs can be found on the Xilinx.com website. This document covers the following design processes:

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Port Descriptions

- Customizing and Generating the Core

- System Integration and Validation: Integrating and validating the system functional performance, including timing, resource use, and power closure. Topics in this document that apply to this design process include:

- Performance

- Resource Use

- Frequency and Hit Rate

- Bandwidth

# **Applications**

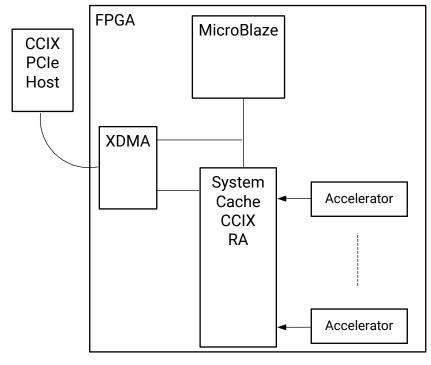

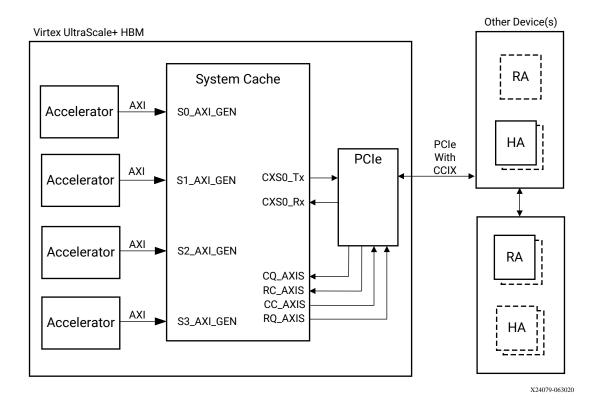

### **CCIX Example**

System Cache configured in CCIX mode enables cache coherency with memory distributed throughout the system all controlled by a PCIe host. In this use case the accelerators connect to System Cache using AXI4 and System Cache provides a local cache function coherent with the rest of the CCIX memory system, without any need for the accelerators to handle the coherency protocol.

Figure 1: CCIX Request Agent (RA) System

X20734-070519

In the CCIX configuration up to four accelerators/kernels can be used, connected to System Cache with ordinary AXI4 interfaces. The system can be configured to use Shared Virtual Memory, SVM, via the Address Translation Services, ATS. Coherent traffic is connected to PCIe using CXS interfaces, while the optional ATS support uses AXI4-Stream. A MicroBlaze processor subsystem handles all the configuration and maintenance to make System Cache operate as a full member of the CCIX network.

Key building blocks in this solution are:

- PCle Host with CCIX Home Agent

- XDMA IP core handling the PCIe connection for the CCIX communication protocol

- System Cache configured as a Request Agent using the CCIX protocol to keep the local cache coherent with the rest of the CCIX memory system, and the Address Translation Cache (ATC) to handle virtual address translation

- MicroBlaze processor based sub-system controlling System Cache to provide Designated Vendor-Specific Capability, DVSEC, to support the CCIX protocol

- Up to four accelerators connected via AXI4 to System Cache

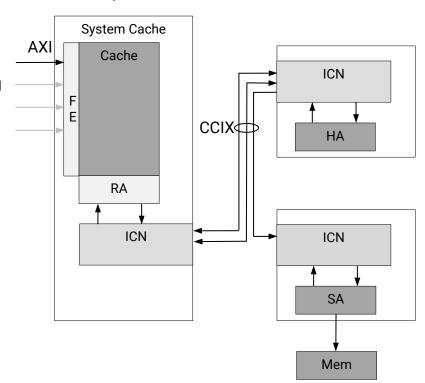

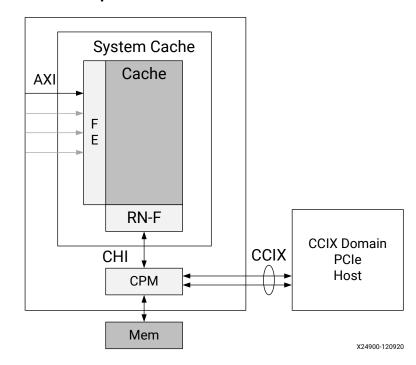

**Figure 2: CCIX Component Overview**

Front end (FE), handles arbitration between accelerators

Request Agent (RA), performs read and write transactions to different addresses

Home Agent (HA), is responsible for memory address range in system

Slave Agent (SA), provides additional memory in system. Always accessed through Home Agent

Memory (Mem)

Coherent Interconnect (ICN)

X23069-080219

### **CHI Example**

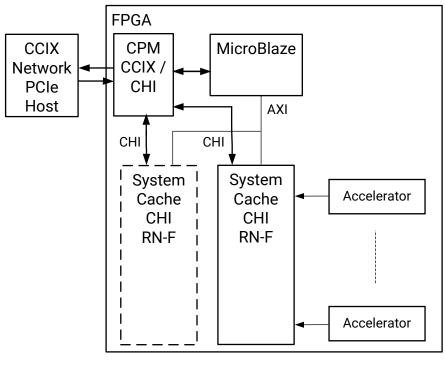

System Cache configured to use CHI Master Coherency enables cache coherency similar to CCIX. In this case System Cache is connected to CPM in Versal, which has the ability to extend the coherency domain to enable cache coherency with memory distributed throughout the system, all controlled by a PCIe host. In this use case the accelerators connect to System Cache using AXI4 and System Cache provides a local cache function coherent with the rest of the CHI/CCIX memory systems, without any need for the accelerators to handle the coherency protocol. CPM has the ability to connect to two System Cache cores with CHI enabled.

Figure 3: CHI Request Node (RN-F) System

X24851-112620

In the CHI configuration up to four accelerators/kernels can be used, connected to System Cache with ordinary AXI4 interfaces. The system can be configured to use Shared Virtual Memory, SVM, via the Address Translation Services, ATS. CPM supports the ability to use PASID, which enables each accelerator to use a unique ID when requesting address translation. A MicroBlaze processor subsystem handles all the configuration and maintenance to make System Cache operate as a full member of the CHI network.

Key building blocks in this solution are:

- Optional PCle Host with CCIX Home Agent

- Versal CPM for CHI connection and potential connection to CCIX domain

- One or two System Cache cores configured as Request Node using the CHI protocol to keep the local cache coherent with the rest of the memory system, and the Address Translation Cache (ATC) to handle virtual address translation with PASID

- MicroBlaze processor based sub-system controlling System Cache to provide configuration and control connection to rest of the system

- Up to four accelerators connected via AXI4 to each System Cache

Figure 4: CHI Component Overview

Request Node (RN-F), performs read and write transactions to different addresses

CPM, gateway between CHI and CCIX domain

Memory (Mem)

### **Pure AXI Example**

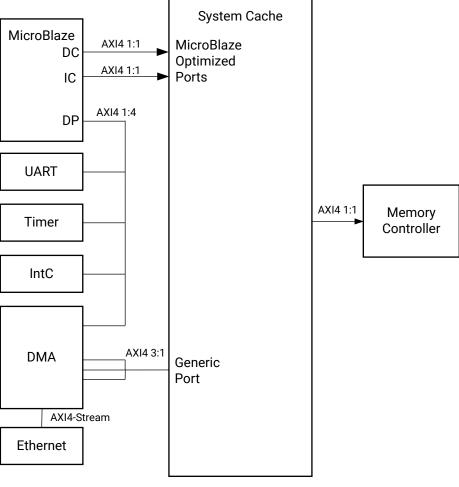

An Ethernet communication system example is shown in the following figure. The system consists of a MicroBlaze processor connected point-to-point to two optimized ports of the System Cache core. A DMA controller is connected to a generic port on the System Cache core through a 3:1 CCIX Component Overview interconnect, because the DMA controller has three master ports. The DMA in turn is connected to the Ethernet IP core using an AXI4-Stream MicroBlaze processor peripheral data port ( $M_AXI_DP$ ) for register configuration and control interface. Standard peripheral functions such as a UART, timer, interrupt controller as well as the DMA controller control port are connected to the MicroBlaze processor peripheral data port ( $M_AXI_DP$ ) for register configuration and control.

With this partitioning the bandwidth critical interfaces are connected directly to the System Cache core and kept completely separated from the AXI4-Lite based configuration and control connections. This system is used as an AXI-specific example throughout the documentation.

Figure 5: Ethernet Systems

X17768-020717

In this example, the MicroBlaze processor is configured for high performance while still being able to reach a high maximum frequency. The MicroBlaze processor frequency is mainly improved due to small cache sizes, implemented using distributed RAM.

The lower hit rate from small caches is mitigated by the higher system frequency and the use of the System Cache core. The decreased hit rate in the MicroBlaze processor caches is compensated by cache hits in the System Cache core, which incur less penalty than accesses to external memory.

Write-through data cache is enabled in the MicroBlaze processor which, in the majority of cases, gives higher performance than using write-back cache when MicroBlaze processor L1 caches are small. The reverse is usually true when there is no System Cache core, or when MicroBlaze processor L1 caches are large. Finally, victim cache is enabled for the MicroBlaze processor instruction cache, which improves the hit rate by storing the most recently discarded cache lines.

All AXI4 data widths on the System Cache core ports are matched to the AXI4 data widths of the connecting modules to avoid data width conversions, which minimizes the AXI4 interconnect area overhead. The AXI4 1:1 connections are only implemented as routing without any logic in this case. All AXI4 ports are clocked using the same clock, which means that there is no need for clock conversion within the AXI4 interconnects. Avoiding clock conversion gives minimal area and latency for the AXI4 interconnects. The parameter settings for the MicroBlaze processor and the System Cache core can be found in the following tables .

Table 1: MicroBlaze Processor Parameter Settings for the Ethernet System

| Parameter              | Value |

|------------------------|-------|

| C_CACHE_BYTE_SIZE      | 512   |

| C_ICACHE_ALWAYS_USED   | 1     |

| C_ICACHE_LINE_LEN      | 8     |

| C_ICACHE_STREAMS       | 0     |

| C_ICACHE_VICTIMS       | 8     |

| C_DCACHE_BYTE_SIZE     | 512   |

| C_DCACHE_ALWAYS_USED   | 1     |

| C_DCACHE_LINE_LEN      | 8     |

| C_DCACHE_USE_WRITEBACK | 0     |

| C_DCACHE_VICTIMS       | 0     |

Table 2: System Cache Parameter Settings for the Ethernet System

| Parameter             | Value |

|-----------------------|-------|

| C_NUM_OPTIMIZED_PORTS | 2     |

| C_NUM_GENERIC_PORTS   | 1     |

| C_NUM_WAYS            | 4     |

| C_CACHE_SIZE          | 65536 |

| C_M_AXI_DATA_WIDTH    | 32    |

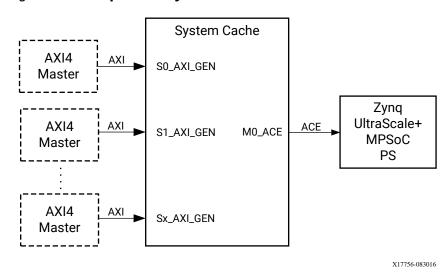

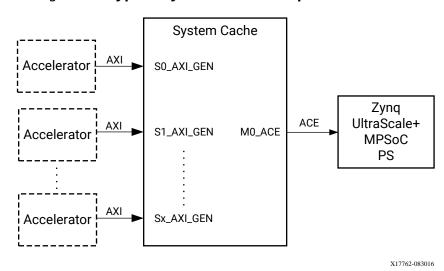

### **ACE Example**

Another example use case, shown in the following figure, is a set of accelerators connected through the System Cache core to the ACE port on a Zynq UltraScale+ MPSoC. To fully take advantage of the System Cache, AXI transactions from the accelerators should be set up as Write-Back memory type (ARCACHE and AWCACHE), preferably Write-back Read and Write-allocate. If it is not possible to directly control this from an accelerator, it is possible to override some of the AxCACHE function through parameters such as

$C_Sx_AXI_GEN_FORCE_WRITE_ALLOCATE$  on a per port basis. This override functionality is available on all ports including the optimized ports.

Figure 6: Example of a System With Two or More Accelerators

It is possible to connect one or more MicroBlaze processor caches to the optimized ports, but they will not be cache coherent with the Zynq UltraScale+ MPSoC Processing System (PS) so manual cache maintenance with WIC and WDC type instructions is needed to observe data.

Example parameters for the System Cache core in this kind of configuration can be found in the following table.  $Sx_AXI_GEN_*$  should be configured for all active ports.

Table 3: Example System Cache Parameters for Accelerator Configuration

| Parameter                            | Value     |

|--------------------------------------|-----------|

| C_NUM_OPTIMIZED_PORTS                | 0         |

| C_NUM_GENERIC_PORTS                  | 2 or more |

| C_NUM_WAYS                           | 4         |

| C_CACHE_SIZE                         | 131072    |

| C_M_AXI_DATA_WIDTH                   | 128       |

| C_ENABLE_COHERENCY                   | 2         |

| C_ENABLE_NON_SECURE                  | 1         |

| C_ENABLE_ERROR_HANDLING              | 1         |

| C_Sx_AXI_GEN_DATA_WIDTH              | 128       |

| C_Sx_AXI_GEN_FORCE_READ_ALLOCATE     | 1         |

| C_Sx_AXI_GEN_PROHIBIT_READ_ALLOCATE  | 0         |

| C_Sx_AXI_GEN_FORCE_WRITE_ALLOCATE    | 1         |

| C_Sx_AXI_GEN_PROHIBIT_WRITE_ALLOCATE | 0         |

| C_Sx_AXI_GEN_FORCE_READ_BUFFER       | 1         |

| C_Sx_AXI_GEN_PROHIBIT_READ_BUFFER    | 0         |

| C_Sx_AXI_GEN_FORCE_WRITE_BUFFER      | 1         |

| C_Sx_AXI_GEN_PROHIBIT_WRITE_BUFFER   | 0         |

All the C\_Sx\_AXI\_PROHIBIT\_WRITE\_ALLOCATE/

C\_Sx\_AXI\_GEN\_PROHIBIT\_WRITE\_ALLOCATE parameters are cleared by default and need to be set to disable allocation on Write Miss. This is not backwards compatible with earlier System Cache versions.

# **Unsupported Features**

The following features of the standards are not supported in the core:

### **CCIX RA Master Port Cache Coherency**

When CCIX Master Port coherency is selected the Optimized slave ports are disabled. The Generic ports are also limited to a maximum of four ports.

CCIX optional CompAck removal is not supported.

CCIX optional support for 128 byte cache lines is not available, only 64 byte cache lines are supported.

CCIX optional Partial Cache States are not supported.

### CHI Master Port Cache Coherency

When CHI Master Port coherency is selected the Optimized slave ports are disabled. The Generic ports are also limited to a maximum of four ports.

CHI optional Stashing feature is not supported.

CHI DVM feature is not supported. No DVM requests are generated, and SnpDVM is terminated but not acted upon.

CHI Partial Cache States are not supported.

# **AXI/ACE Slave Address Space**

Fixed burst is not supported on any AXI or ACE port. System Cache only deals with regular memory handling, fixed burst is more relevant in a queue context.

Most significant address bit is not available dynamically, only to set upper or lower half statically, i.e. up to 63 address bits can be used freely from AXI Masters.

### **ACE Master Port Cache Coherency**

When master port cache coherency is enabled coherency on the optimized ports is not supported. In this case, any MicroBlaze processor that is connected must perform manual cache maintenance operation with WIC and WDC instructions (usually through BSP function calls) in order to work reliably with the coherent domain. This usually also includes proper communication between the participants in the coherency domain and any MicroBlaze processor to synchronize for safe data exchange.

### **Non-Coherent Implementation**

The System Cache core provides no support for coherency between the MicroBlaze processor internal caches when cache coherency is disabled. This means that software must ensure coherency for data exchanged between the processors. When the MicroBlaze processors use write-back data caches, all processors need to flush their caches to ensure that correct data is being exchanged. For write-through caches, it is only the processors reading data that need to invalidate their caches to ensure that correct data is being exchanged.

## **Optimized Port Cache Coherent Implementation**

When optimized port cache coherency is enabled, cached masters connected through the generic AXI4 slave ports are not included in the coherency domain. The reason for this is that the connection is pure AXI and not ACE, so it is not possible to snoop any master connected to a generic port.

All writes from a generic port remove corresponding line(s) from any MicroBlaze processor cache connected to an optimized port so that the new data is visible to the MicroBlaze processor. A read gets a snapshot of the current value of the coherency domain; if this value is stored locally (cached) in the AXI master it is the responsibility of that master to perform proper cache maintenance to remain coherent.

When cache coherency is enabled, exclusive transactions from the generic ports are disabled, and treated as normal transactions. The reason for this is that only the ACE transaction-based method with snoop messages is supported when cache coherency is enabled.

# **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

# **CCIX RA Master Port Cache Coherency**

Cache Coherent Interconnect for Accelerators (CCIX®) cache coherency is used for multiple devices with system wide cache coherency. System Cache provides one Request Agent (RA) that can access multiple Home Agents (HA). It provides up to four AXI4 interfaces for accelerators to connect to as shown in the following figure.

Figure 7: Typical CCIX RA Master Port Cache Coherency System

System Cache connects to the PCIe block with one CXS point-to-point interface in each direction and with four AXI4-Stream interfaces when ATS address translation is enabled. The FPGA is connected to other devices via PCIe, which will tunnel CCIX traffic on a Virtual Channel (VC). These devices must contain one or more HAs, and possibly even internal RAs, as well as connect to other devices with additional RAs and/or HAs.

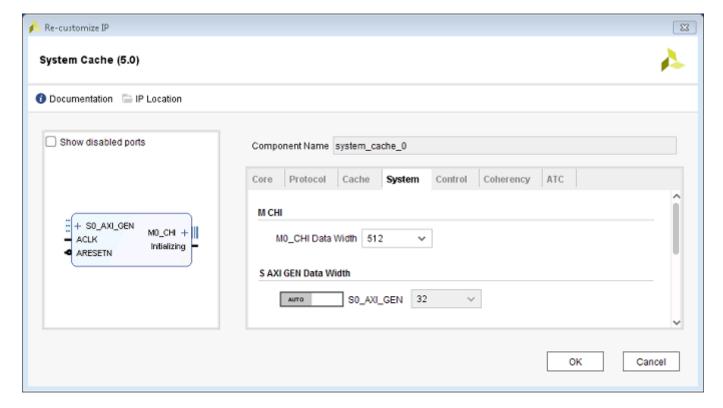

# **CHI RN Master Port Cache Coherency**

CHI is used for connection to local cache coherency in a device or system-wide cache coherency. System Cache provides one Request Node (RN-F) that can access the local Home Node (HN) in the Versal CPM and multiple Home Agents (HA) when CCIX is enabled externally in the CPM. Up to four AXI4 interfaces are provided per System Cache instance for accelerator connections as shown in the following figure.

Mem Other Device(s) Versal ACAP System Cache CHI RN-F RAAccelerator PCle S0\_AXI\_GEN CPM With CCIX/ CCIX CHI CHI НΑ M0\_CHI VC1 AXI Accelerator S1\_AXI\_GEN AXI Accelerator S2\_AXI\_GEN PCIe VC0 AXIS CO RC CC RQ RAATS(#0) AXI S3\_AXI\_GEN Accelerator HΑ ATS Switch PCIe VC0 System Cache CHI RN-F Accelerator ! S0\_AXI\_GEN ATS(#1) AXIS to **AXIMM** Accelerator ! ► S1\_AXI\_GEN CHI S2\_AXI\_GEN M0\_CHI Accelerator ! AXI S3\_AXI\_GEN Accelerator !

Figure 8: Typical CHI RN Master Port Cache Coherency System

X24853-120920

System Cache connects to the CPM block with one CHI point-to-point interface and with four AXI4-Stream interfaces when ATS address translation is enabled. The CPM has two CHI ports so that two System Caches can be connected to the same CPM. An ATS switch is included to distribute ATS traffic to all System Cache instances. The FPGA is connected to other devices via PCIe, which tunnels CCIX traffic on a Virtual Channel (VC). These devices must contain one or more HAs, and may possibly even have internal RAs, as well as connect to other devices with additional RAs and/or HAs.

# **Address Translation Service and Cache**

There are various reasons for enabling System Cache address translation, including:

- Avoiding host device driver and letting accelerators work directly with addresses provided by the host application

- Limiting the impact of "memory leakage" or an incorrectly programmed endpoint

- Address space conversion (smaller endpoint address range to larger system virtual address space)

- Providing scatter/gather functionality

- Virtualization support

The System Cache includes an ATC function with companion ATS to support virtual address handling. The function is split into three parts:

- ATC TLB: ATC Translation Lookaside Buffer, located in each AXI4 Slave port interface, which holds the most recently used translations for AR and AW channel transactions respectively.

- ATC Table: ATC Translation Lookaside Buffer Cache, one common table with recently cached local copies of the Host TA Virtual to Physical Address map, with a default size of 256 entries.

- ATS: Address Translation Service, protocol based message service over PCIe Virtual Channel 0 (VC0), including message structures to support maintenance of ATC Table synchronization with the Host TA.

To enable ATS, configure System Cache with optional C\_ENABLE\_ADDRESS\_TRANSLATION set. The ATS function is activated through the System Cache Capability registers and the PCle configuration structure, mirrored in the System Cache register space.

If ATS is enabled, but not activated, System Cache will not issue any ATS Translation Requests and will use the "untranslated" physical addresses for all read and write requests.

If System Cache is configured with address translation disabled, the ATS AXI4-Stream interfaces are not visible on the System Cache IP core.

The System Cache translation process, using the ATC Table and the AR and AW channel ATC TLB for each of the AXI4 Slave ports provides:

- The ability to reduce look-up latency by distributing address translation caching

- Reduced probability of "thrashing" within the Host TA memory management entries

- Improved system performance by ATC TLB search, ATC Table locality, and reduced dependency on the Host TA latency

- Reduced latency by less frequent requests to the Host TA for missing address mappings

ATS uses a request-completion protocol between an endpoint, System Cache and the Host TA, to provide the translation service. ATS capabilities also include handling the Page Request Interface (PRI), to request the Host TA to map requested pages.

Because System Cache only expects ATS/PRI messages, any other messages on VC0 must be filtered out outside System Cache. Unexpected messages will be silently discarded, to avoid inconsistency or message blocking, causing data to be lost for any memory or I/O accesses.

The System Cache ATS interface consists of independent Request/Completion streams, two for Requester and two for Completer, each having programmable parity protection and checking on the AXI4-Stream interfaces.

- Incoming Completer Request (CQ) interface through which ATS Invalidation requests and PRI Response from Host TA are sent to the System Cache

- Outgoing Completer Completion (CC) interface through which the System Cache sends back responses to the completer requests (including AER error handling)

- Outgoing Requester Request (RQ) interface through which the System Cache generates translation requests to the Host TA, ATS Invalidation completions and PRI requests

- Incoming Requester Completion (RC) interface through which the translation completions are received from the Host TA in response to System Cache ATS TA requests

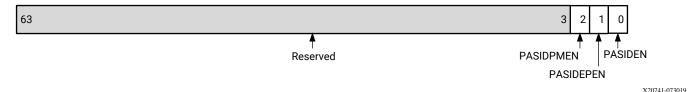

To allow ATC Table entries to use unique virtual address spaces, System Cache optionally allows a Process Address Space ID (PASID) extension.

With CCIX protocol address translations the PASID extension is added to the AXI4 Slave ports to allow different processes to use dedicated translation mappings in the ATC over time, which will not propagate PASID on the AXI4-Stream interfaces.

With CHI protocol address translation, for supported technologies, the added PASID extension also propagates the PASID to the Host TA via the AXI4-Stream interfaces.

When full PASID propagation is enabled the page attributes Privileged and Execute options are propagated from Host TA together with normal Read/Write attributes, as well as the translated page attributes Global Mapping (same TA page mapping regardless of PASID) and Global Invalidate (invalidate all TA pages in ATC table regardless of PASID for given TA).

X17757-082416

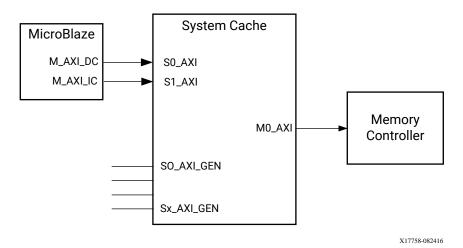

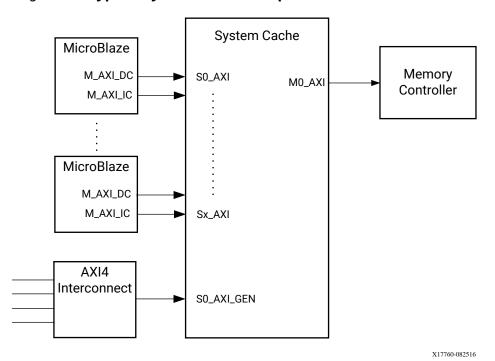

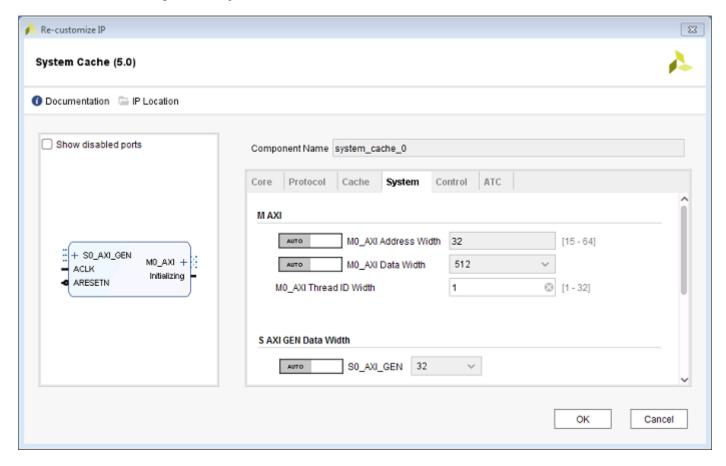

## **AXI Master**

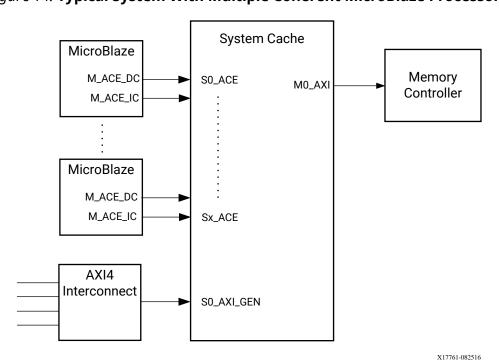

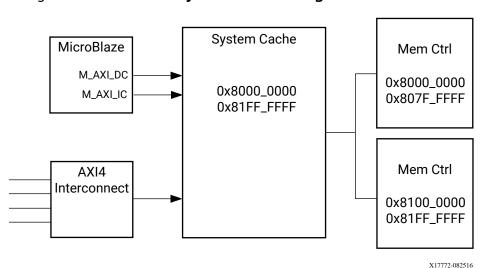

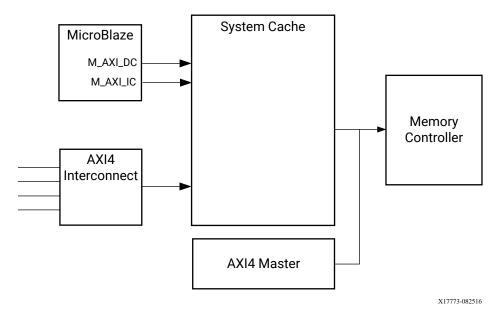

In a typical system with one MicroBlaze<sup>™</sup> processor, as shown in the following figures, the instruction and data cache interfaces (M\_AXI\_IC and M\_AXI\_DC) are connected to dedicated AXI4 interfaces optimized for MicroBlaze on the System Cache core. The System Cache core often makes it possible to reduce the MicroBlaze internal cache sizes without reducing system performance. Non-MicroBlaze AXI4 interface masters are connected to one or more of the generic AXI4 slave interfaces of the System Cache core either through an AXI4 interconnect or directly as shown in the following figures.

MicroBlaze

M\_AXI\_DC

M\_AXI\_IC

S0\_AXI

S1\_AXI

Memory

Controller

S0\_AXI\_GEN

Figure 9: Typical System with a Single Processor

Figure 10: Typical System With a Single Processor

AXI4

Interconnect

S0\_AXI\_GEN M0\_AXI

Memory

Controller

Figure 11: System Without Processor

The System Cache core has 16 cache interfaces optimized for MicroBlaze, enabling direct connection of up to eight MicroBlaze processors, as shown in the following figure.

Figure 12: Typical System With Multiple MicroBlaze Processors

# **ACE Master Port Cache Coherency**

ACE Master port cache coherency is used to support an arbitrary AXI4 master, primarily intended for accelerators, with a system cache that is coherent to the Zynq<sup>®</sup> UltraScale+™ MPSoC PS caches. All coherency is handled seamlessly from the point of view of the AXI master. The only software required is the regular set up of memory types and modes in the APU.

The R5 real-time processors need software interaction to accurately see the latest data because only the A53s have hardware support for cache coherency to the programmable logic (PL).

Up to 16 accelerators can be connected directly to the System Cache core which provides fast access to memory that is coherent to the PS caches in the Zynq UltraScale+ MPSoC, as shown in the following figure.

Figure 13: Typical System With Multiple Accelerators

# **Optimized Ports Cache Coherency**

Optimized port cache coherency support is used to enable data and instruction cache coherency for multiple MicroBlaze cores. It provides reliable exclusive transactions to implement software spinlocks and simplifies multi-processor (MP) systems where data is shared among the processors. Any data that is updated from one MicroBlaze is guaranteed to be seen from its peer processors without any special software interactions other than ordinary single MicroBlaze rules

for handling self-modifying code. This data manipulation information exchange is handled by the snooping mechanism provided by the AXI Coherency Extension (ACE) (see the AMBA AXI and ACE Protocol Specification). Distributed Virtual Memory (DVM) messages are also available with ACE to ensure that memory management units (MMU) and branch target caches are updated across the system when related changes are performed by any of the connected processors.

The 16 cache interfaces optimized for MicroBlaze provide support for up to eight cache coherent MicroBlaze processors, as shown in the following figure.

Figure 14: Typical System With Multiple Coherent MicroBlaze Processors

# **Exclusive Monitor**

The optional exclusive monitor provides full support for exclusive transactions when cache coherency is disabled. It supports exclusive transactions from both generic and optimized ports.

# **Cache Memory**

The cache memory provides the actual cache functionality in the core. The cache is configurable in terms of size and associativity.

The cache size can be configured with the parameter C\_CACHE\_SIZE according to User Parameters. The selected size is a trade-off between performance and resource usage, in particular the number of on-chip RAMs.

The associativity can be configured with the parameter C\_NUM\_WAYS according to User Parameters. Increased associativity generally provides better hit rate, which gives better performance but requires more area resources.

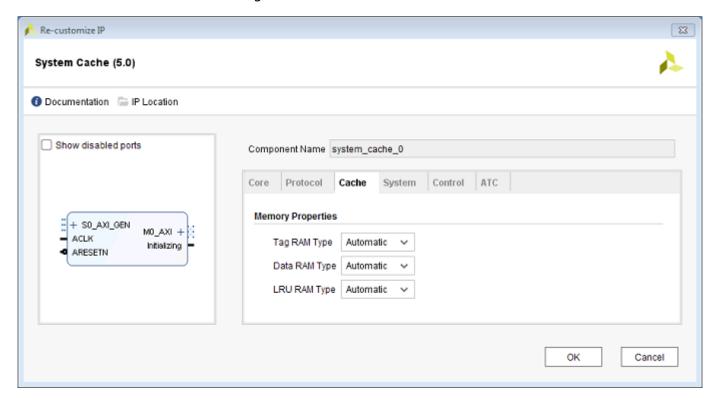

The type of memory used for Tags, Data and LRU can be configured with the parameters C\_CACHE\_TAG\_MEMORY\_TYPE, C\_CACHE\_DATA\_MEMORY\_TYPE and C\_CACHE\_LRU\_MEMORY\_TYPE respectively. The possible values are Automatic, LUTRAM, BRAM and URAM, except that LUTRAM cannot be selected for Data. Additionally, it is only possible to select URAM for UltraScale+ devices. The default configuration, Automatic, is generally recommended, but for larger cache sizes selecting URAM for Data (if possible) will provide better resource utilization.

The correspondence between selected parameters and on-chip RAMs used can be found in Performance and Resource Utilization.

#### **Related Information**

**User Parameters**

# **Error Handling**

Different levels of support for error handling are available depending on the configuration, all the way from feature-rich for CCIX down to bare minimum or none for pure AXI4.

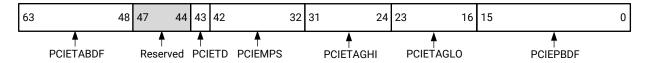

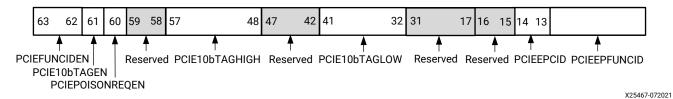

With the Address translation option, the PCle AER can be enabled extending AXI4-Stream data integrity.

### **CCIX Error Handling**

CCIX error handling expands on the AXI error handling and extends it to full Reliability, Availability and Serviceability (RAS) support, according to the CCIX protocol. It has all the filtering and control options in order to tailor the kind of errors that need to be handled.

The Protocol Error Reporting (PER) messages sent and error logs created depend on the configuration defined by control registers.

## **CHI Error Handling**

CHI Error handling is based on CCIX, with the same structure used for PER Log but without the PER message part. In addition the CHI specific error handling is used.

# ATS/ATC Error Handling

ATS/ATC error handling expands on the PCIe, Requester and Completer AXI4-Stream, error handling and extends it to full AER support. Generated AER messages and created error logs depend on the configuration defined by control registers.

Internal ATC memory structures are protected by optional parity, with all parity errors reported as internal ATC correctable errors via CCIX PER.

- Protocol errors reported via the Advanced Error Reporting Extended Capability Structure:

- 1. Unsupported Request (UR), Completer Abort (CA), or Unexpected Completion: AER is propagated by the ATS interface

- 2. AXI4-Stream parity error: When parity check is enabled, AER is propagated by the ATS interface and the TLP is aborted

- 3. Malformed TLP detected by the PCIe core: AER is reported by the core and the ongoing translation results in Decode Error on the generic AXI port BRESP

- 4. Illegal TAG usage, unsuccessful or erroneous completions detected by the PCle core: AER is reported by the core and the ongoing translation results in Decode Error on the generic AXI port BRESP

- 5. Requester channel timeout detected by the PCIe core: AER is reported by the core

- 6. Protocol Completer channel timeouts: AER is propagated by the ATS interface and the ongoing translation results in Decode Error on the generic AXI port BRESP

- Protocol Error not reported via AER:

- 1. Receiver overflow: Error should avoided by configuration and when full or not ready the ATS interface does not accept additional data on the AXI4-Stream interface

- ECRC Check Failed: ECRC is not supported and System Cache must be configured with the TD bit cleared

- 3. Header Discontinue, Poisoned TLP Received: Transaction is aborted and no AER is propagated by the ATS interface

The ATS/ATC error handling is enabled with the C\_ATS0\_CQ\_CC\_ENABLE\_AER parameter for Completer channels and C\_ATS0\_RQ\_RC\_ENABLE\_AER for Requester channels.

When ATS AER handling is enabled a detected error will be logged and propagated to the PCIe Host and the Cmd/Cpl (header) and/or Payload (data) affected will be discarded.

In case CA/UR, Sequence and TLP incompleteness are detected on the RC channel, errors signaled over AXI4-Stream are logged and reported, but error handling relies on the PCIe core reporting of AER external to System Cache for complementary error logs.

The ATC integrity error handling feature is controlled by the configuration parameter C\_ENABLE\_INTEGRITY, also used for all other System Cache integrity functionality.

In case of ATC integrity error detection, caused by a Single Event Upset (SEU) or by integrity function fault injection, the affected ATC table entry is silently invalidated to avoid undetectable multiple error accumulation in the memory.

ATC Table look-up, in case of an ATC TLB miss, blocks any attempt to use table entries with parity errors. The automatic background scrubbing or manually initiated scrubbing then removes any pending errors from the ATC Table, with silent invalidation.

Also note that any normal Host TA commanded invalidation, for any address range, causes pending errors to be removed.

Integrity error detection and removal is logged and reported via PER.

ATC integrity handling uses the same structure on CHI as for CCIX, with PER Log but without the PER message propagation.

With CHI, the interrupt event notifies the software error manager to poll the PER log

An ATC integrity error is correctable on system level, since the PCIe host TA holds all translations cached by the ATC Table. Any invalidation due to an integrity error will cause a new ATS TA request.

See the PCI Express® Base Specification for the AER structure definition, and CCIX® Base Specification for the PER message definition.

# **AXI4/ACE Error Handling**

The optional AXI4/ACE error handling is enabled with the C\_ENABLE\_ERROR\_HANDLING parameter. It allows the refusal of the allocation of a line if there is an decode or slave error when a line is fetched from external memory.

# **Non-Secure Handling**

The optional handling of Secure/Non-Secure can be enabled with the  $C_ENABLE_NON_SECURE$  parameter. When active the AxPROT[1] bit is treated as an extra address bit to provide a distinction between the two modes. This also means that the same address can be cached as both Secure and Non-Secure at the same time.

Additional control registers are available when this feature is enabled to allow command and control of the System Cache core, distinguishing between the different modes.

**Note:** When enabling Address Translation, the same Host TA Address map will be used. The need to keep a unique mapping per mode must be resolved on the system level in host TA, by invalidation and address remapping.

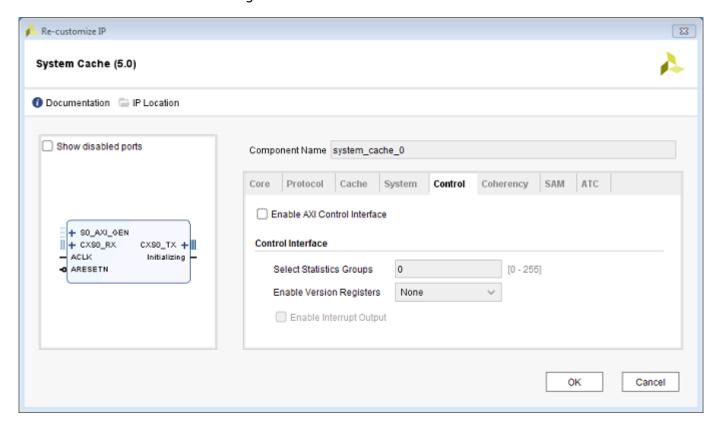

## **Control and Statistics**

A minimal set of control and statistics is always available. When CCIX is enabled the set of available control and statistics features is expanded.

#### **CCIX Control**

Typically CCIX is controlled by firmware executing on a dedicated MicroBlaze processor. Features that can be controlled are:

- Request Agent on/off

- Link on/off including the entire sequence of bringing up and taking down the link

- Port on/off

- Snoop response behavior

- Cache Maintenance Operations (CMO) event properties

#### **CHI Control**

Like CCIX, CHI is typically controlled by firmware executing on a dedicated MicroBlaze processor. Features that can be controlled are:

- Request Node on/off

- Link on/off including the entire sequence of bringing up and taking down the link

- System Coherency on/off

- Snoop response behavior

- Cache Maintenance Operations (CMO) event properties

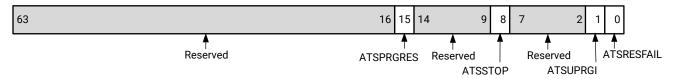

## **ATS/ATC Control**

When Address Translation with ATS is enabled, for CHI and CCIX, the set of available control and statistics features is expanded to configure, control and gather statistics.

ATS control is needed to configure, control and report status to the PCIe root complex (host TA), to simplify system configuration and bring up; normally all PCIe endpoint configuration, enumeration and operational control are handled by firmware.

Features available for control are:

- ATS propagation on/off

- PRI propagation on/off

- PRI Retry capability on/off

- PRI Retry threshold level, if PRI Retry capability on

- TAG range support

- Memory attributes on/off (propagated from Host TA override defaults)

- PASID on/off (when enabled both CCIX and CHI)

- Page attributes Privilege Enable/ Execute Enable on/off (with CHI PASID enabled)

- Global Invalidate Enabled on/off (with CHI PASID enabled)

## **AXI4/ACE Control**

The Following types of control and configuration information are available:

- Control registers for Flush and Clear cache maintenance

- Version Registers with System Cache core configuration

#### **Statistics**

The optional Statistics and Control block can be used to collect cache statistics such as cache hit rate and access latency. The statistics are primarily intended for internal Xilinx use, but can also be used to tailor the configuration of the System Cache core to meet the needs of a specific application. The following types of statistics are collected:

- Port statistics for each slave interface

- Total Read and Write transaction counts

- Port queue usage for the six transaction queues associated with each port

- Cache hit rates for read and write

- Read and Write transaction latency

- Total ATC Read and Write transaction counts

- ATC TLB Address hit rates for read and write

- ATC TLB Read and write latency

- . ATC TLB Read and write LRU replacement ratio

- Arbitration statistics

- Functional unit statistics

- Stall cycles

- Internal queue usage

- Port statistics for the master interface

- Read and write latency

- CCIX Backend

- Message count

- 。 TLP count

- Credit count

- CHI Backend

- Message count

- Credit count

- ATS

- ATC Table Address hit rates for read and write

- ATC Table Read and write latency

- ATC Table Read and write LRW replacement ratio

- ATC Table PRI transaction Retry counts

- ATC Table PRI transaction TimeOut counts

- ATC Table TA transaction Fail counts

- ATC Table Invalidation transaction counts

# **Standards**

The System Cache core adheres to:

AMBA® AXI4 and ACE interface standard (see Arm® AMBA AXI Protocol Specification, Version 2.0 ARM IHI 0022E)

- AMBA AXI4-Stream interface standard (see Arm AMBA 4 AXI4-Stream Protocol Specification, Version 1.0 ARM IHI 0051A)

- AMBA® CHI interface standard (see AMBA® 5 CHI Architecture Specification, Issue B ARM IHI 0050B)

- AMBA CXS interface standard (see Arm AMBA CXS Protocol Specification, ARM IHI 0079A)

- CCIX Cache Coherent Interconnect for Accelerators standard (see CCIX Base Specification Revision 1.1 Version 1.0)

- PCI Express<sup>®</sup> standard (see PCI Express Base Specification Revision 5.0 Version 1.0)

- PCI Express ATS Memory Attributes (see ATS Memory Attributes ECN, Revision A)

# **Performance**

The perceived performance is dependent on many factors such as frequency, latency and throughput. Which factor has the dominating effect is application-specific. There is also a correlation between the performance factors; for example, achieving high frequency can add latency and also wide datapaths for throughput can adversely affect frequency.

Read latency is defined as the clock cycle from the read address is accepted by the System Cache core to the cycle when first read data is available.

Write latency is defined as the clock cycle from the write address is accepted by the System Cache core to the cycle when the BRESP is valid. These calculations assume that the start of the write data is aligned to the transaction address.

Snoop latency is defined as the time from the clock cycle a snoop request is accepted by the System Cache core to the cycle when CRRESP or CDDATA is valid, whichever is last. Not all snoops result in a CDDATA transaction.

#### **Maximum Frequencies**

For details about performance, visit Performance and Resource Utilization.

#### **CCIX Cache Latency**

CCIX latency calculations are in principle defined in the same way as above in the introduction, but the time in flight on the PCIe bus is not included. Also, no additional delays due to ATS/ATC virtual address translation is included.

For the different types of transactions, this means:

- Read: From AXI ARVALID to start of TLP request + start of TLP response to AXI RRESP

- Write: From AXI AWVALID to start of TLP request + start of TLP response to AXI BRESP

- Snoop: From start of TLP request to start of TLP response

- Scrub (automatic): From timer initiation of the scrub to completion

- Scrub (manual): From AXI control write initiation of the scrub to completion

The latency depends on many factors such as traffic from other ports and conflict with earlier transactions. The numbers in the following table assume a completely idle System Cache core.

**Table 4: System Cache CCIX Latency**

| Туре                      | CCIX Latency                                                                                           |

|---------------------------|--------------------------------------------------------------------------------------------------------|

| Read Hit                  | 16                                                                                                     |

| Read Miss                 | 45 + round-trip delay on PCIe for request                                                              |

| Read Miss Dirty           | max of: 45 + round-trip delay on PCIe for read request 39 + round-trip delay on PCIe for write request |

| Write Hit                 | 16                                                                                                     |

| Write Miss                | 44 + round-trip delay on PCIe for request                                                              |

| Write Miss Dirty          | max of: 45 + round-trip delay on PCIe for read request 39 + round-trip delay on PCIe for write request |

| Snoop (missing broadcast) | 23                                                                                                     |

| Snoop                     | 26                                                                                                     |

| Snoop with data           | 33                                                                                                     |

| Scrub (automatic)         | 11                                                                                                     |

| Scrub (manual)            | 17                                                                                                     |

#### CHI Cache Latency

CHI latency calculations are defined in a similar way as CCIX, but the time in flight in the CHI domain is not included. Also, no additional delays due to ATS/ATC virtual address translation is included.

For the different types of transactions, this means:

- Read: From AXI ARVALID to request FLIT + response FLIT to AXI RRESP

- Write: From AXI AWVALID to request FLIT + response FLIT to AXI BRESP

- Snoop: From start of Request FLIT to start of TLP response

- Scrub (automatic): From timer initiation of the scrub to completion

- Scrub (manual): From AXI control write initiation of the scrub to completion

The latency depends on many factors such as traffic from other ports and conflict with earlier transactions. The numbers in the following table assume a completely idle System Cache core.

Table 5: System Cache CHI Latency

| Туре                      | CHI Latency                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------|

| Read Hit                  | 16                                                                                                   |

| Read Miss                 | 34 + round-trip delay on CHI for request                                                             |

| Read Miss Dirty           | max of: 32 + round-trip delay on CHI for read request 31 + round-trip delay on CHI for write request |

| Write Hit                 | 16                                                                                                   |

| Write Miss                | 32 + round-trip delay on CHI for request                                                             |

| Write Miss Dirty          | max of: 32 + round-trip delay on CHI for read request 31 + round-trip delay on CHI for write request |

| Snoop (missing broadcast) | 23                                                                                                   |

| Snoop                     | 26                                                                                                   |

| Snoop with data           | 33                                                                                                   |

| Scrub (automatic)         | 11                                                                                                   |

| Scrub (manual)            | 17                                                                                                   |

#### **ATS/ATC Latency**

The inclusion of the Address Translation Service, ATS and the ATC TLB in the AXI port interfaces will add latency to the above AXI4/ACE Cache Latency, in most cases the locality will have minimal hit latency but miss latency are expected in restarted systems with no accumulated translation and in case of locality context change.

Read latency is defined from the read address is accepted by the System Cache core to the cycle when first read data is available via the Address Translation service.

Write latency is defined from the write address is accepted by the System Cache core to start of the write data is aligned to the transaction address via the Address Translation service.

For the transaction best case latency it is assumed that previous accesses have already used the address range, hence both read and write will result in ATC TLB hits.

When a miss occurs in the ATC TLB, it is assumed that the ATC Table has a copy of a valid Translation, latency is added with best-case and worst-case latency due to ATS search.

**Note:** The worst-case latency is related to ATS Tables size and is depth dependent – here the default size of 256 entries is used.

The average expected for ATC Search latency depends upon temporal locality of addresses in use in the ATC Table, where the entries of the n last mapped translations are cached, and ATC search hits will be within these n translations.

In the case of ATC table miss, the latency will be extended with PCIe Root Complex, Host TA, translation latency, which are system level defined latency – outside System Cache definition scope.

The host TA best-case translation time is the round trip transaction latency from request to response plus the host TA lookup time. The time can be extended with one or more page request round trips plus host page management latencies, and finally another retry translation round trip host TA lookup.

ATC table lookup latency is two clock cycles best case, 256+2 clock cycles worst case, and n/2+2 clock cycles on average (assuming locality for the n last accesses and hit latency within n entries).

**Table 6: System Cache Core Latencies with Address Translation**

| Туре                                           | AXI4 Port Latency with Address Translation Latency (See CHI/<br>CCIX Master port Read/Write Latency)       |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Read Hit/Miss, ATC TLB Hit                     | 2 + Master port Read latency (Hit/Miss)                                                                    |

| Read Hit/Miss, ATC TLB Miss, ATC Table Hit     | 3 + ATC table lookup + Master port Read latency (Hit/Miss)                                                 |

| Read Hit/Miss, ATC TLB Miss and ATC Table Miss | 3 + ATC table lookup Worst + latency added by PCIe ATS lookup + Master port<br>Read latency (Hit/Miss)     |

| Write Hit/Miss, ATC TLB Hit                    | 2 + Master port Write burst latency (Hit/Miss)                                                             |

| Write Hit/Miss, ATC TLB Miss, ATC Table Hit    | 3 + ATC table lookup + Master port Write burst latency (Hit/Miss)                                          |

| Write Hit/Miss, ATC TLB Miss, ATS Table Miss   | 3 + ATC table lookup Worst + latency added by PCIe ATS lookup + Master port Write burst latency (Hit/Miss) |

#### **AXI4/ACE Cache Latency**

Here latency is used as described in the introduction.

The latency depends on many factors such as traffic from other ports and conflict with earlier transactions. The numbers in the following table assume a completely idle System Cache core and no write data delay for transactions on one of the optimized ports. For transactions using a generic AXI4 port an additional two clock cycle latency is added.

**Table 7: System Cache Core Latencies for Optimized Port**

| Туре            | Optimized Port Latency                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Read Hit        | 6                                                                                                                                       |

| Read Miss       | 7 + latency added by memory subsystem                                                                                                   |

| Read Miss Dirty | Maximum of: 7 + latency added by memory subsystem 7 + latency added for evicting dirty data (cache line length * 32 / M_AXI Data Width) |

| Write Hit       | 3 + burst length                                                                                                                        |

| Write Miss      | Non-bufferable transaction: 7 + latency added by memory subsystem for writing data<br>Bufferable transaction: Same as Write Hit         |

Enabling optimized port cache coherency affects the latency and also introduces new types of transaction latencies. The numbers in the following table assume a completely idle System Cache core and no write data delay for transactions on one of the optimized ports. Transactions from a generic port still have two cycles of extra latency.

**Table 8: System Cache Core Latencies for Cache Coherent Optimized Port**

| Туре            | Coherent Optimized Port Latency                                                                                                                                                                                 |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DVM Message     | 9 + latency added by snooped masters                                                                                                                                                                            |  |  |  |  |

| DVM Sync        | 2 + latency added by snooped masters                                                                                                                                                                            |  |  |  |  |

| Read Hit        | 9 + latency added by snooped masters                                                                                                                                                                            |  |  |  |  |

| Read Miss       | 10 + latency added by snooped masters + latency added by memory subsystem                                                                                                                                       |  |  |  |  |

| Read Miss Dirty | Maximum of: 10 + latency added by snooped masters + latency added by memory subsystem 10 + latency added by snooped masters + latency added for evicting dirty data (cache line lengtl * 32 / M_AXI Data Width) |  |  |  |  |

| Write Hit       | Maximum of: 3 + burst length 6 + latency added by snooped masters                                                                                                                                               |  |  |  |  |

| Write Miss      | Non-bufferable transaction: 10 + latency added by snooped masters + latency added by memory subsystem for writing data Bufferable transaction: same as Write Hit                                                |  |  |  |  |

When master port cache coherency is enabled the System Cache core provides CRRESP and potential data as quickly as possible, but the response time varies according to the current state and transactions in flight, both internally and externally, as long as they have an effect on the System Cache state. See the following table for latency values.

**Table 9: Core Latency Values for Master Port Cache Coherency**

| Туре       | Master Port Snoop Latency                                                                                                                                                                                                                                                        |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Snoop Miss | 3 + latency of any preceding snoop blocking progress 4 + latency of any preceding snoop blocking progress (if hazard with pipelined access) 5 + latency of any preceding snoop blocking progress + latency to compete active write with hazard                                   |  |  |  |

| Snoop Hit  | 4 + latency to acquire data access + latency of any preceding snoop blocking progress 5 + latency of any preceding snoop blocking progress (if hazard with pipelined access) 5 + latency of any preceding snoop blocking progress + latency to complete active write with hazard |  |  |  |

The numbers for an actual MicroBlaze application vary depending on access patterns, hit/miss ratio and other factors. Example values from a system (see Typical System with a Single Processor above) running the iperf network testing tool with the LWIP TCP/IP stack in raw mode are shown in the following four tables, where the first contains the hit rate for transactions from all ports, and the remaining show per port hit rate and latencies for the three active ports.

**Table 10: Application Total Hit Rate**

| Туре  | Hit Rate |  |

|-------|----------|--|

| Read  | 99.82%   |  |

| Write | 92.93%   |  |

Table 11: System Cache Hit Rate and Latencies for MicroBlaze D-Side Port

| Туре  | Hit Rate | Min | Max | Average | Standard<br>Deviation |

|-------|----------|-----|-----|---------|-----------------------|

| Read  | 99.68%   | 6   | 290 | 8       | 3                     |

| Write | 96.63%   | 4   | 31  | 4       | 1                     |

Table 12: System Cache Hit Rate and Latencies for MicroBlaze I-Side Port

| Туре  | Hit Rate | Min | Max | Average | Standard<br>Deviation |

|-------|----------|-----|-----|---------|-----------------------|

| Read  | 9.96%    | 5   | 568 | 6       | 2                     |

| Write | N/A      | N/A | N/A | N/A     | N/A                   |

Table 13: System Cache Hit Rate and Latencies for Generic Port

| Туре  | Hit Rate | Min | Max | Average | Standard<br>Deviation |

|-------|----------|-----|-----|---------|-----------------------|

| Read  | 76.68%   | 7   | 388 | 18      | 13                    |

| Write | 9.78%    | 6   | 112 | 24      | 5                     |

#### **Throughput**

The System Cache core is fully pipelined and can have a theoretical maximum transaction rate of one read or write hit data concurrent with one read and one write miss data per clock cycle when there are no conflicts with earlier transactions.

This theoretical limit is subject to memory subsystem bandwidth, intra-transaction conflicts and cache hit detection overhead, which reduce the achieved throughput to less than three data beats per clock cycle.

# **Resource Use**

The System Cache core uses instantiated block RAM or UltraRAM; how many varies with configuration. Distributed RAM is inferred by the RTL code and is also dependent on the configuration.

For full details about performance and resource use, visit the Performance and Resource Use web page.

# **Port Descriptions**

#### **CCIX Port Descriptions**

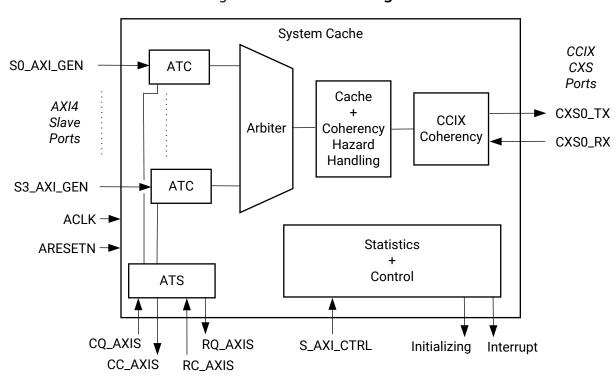

The block diagram of the System Cache core configured for CCIX is shown in the following figure. All interfaces are compliant to AXI4, AXI4-Stream or CXS where applicable. The input signals ACLK and ARESETN implement clock and reset for the entire System Cache core.

Figure 15: CCIX Block Diagram

ATS AXI4-Stream Ports

X23134-063020

**Table 14: CCIX Interfaces**

| Name                    | Туре       | Description                      |

|-------------------------|------------|----------------------------------|

| ACLK                    | Input      | Core clock                       |

| ARESETN                 | Input      | Synchronous reset of core        |

| Initializing            | Output     | Core is initializing after reset |

| Sx_AXI_GEN <sup>1</sup> | AXI4 Slave | Generic cache port               |

Table 14: CCIX Interfaces (cont'd)

| Name       | Туре               | Description              |  |

|------------|--------------------|--------------------------|--|

| S_AXI_CTRL | AXI4-Lite Slave    | Control port             |  |

| CXS0_RX    | CXS Receive        | CXS interface            |  |

| CXS0_TX    | CXS Transmit       | CXS Interface            |  |

| CQ_AXIS    | AXI4 Stream Slave  | ATS CQ Interface         |  |

| CC_AXIS    | AXI4 Stream Master | ATS CC Interface         |  |

| RC_AXIS    | AXI4 Stream Slave  | ATS RC Interface         |  |

| RQ_AXIS    | AXI4 Stream Master | ATS RQ Interface         |  |

| Interrupt  | Output             | Control interrupt output |  |

1. x = 0 to 3

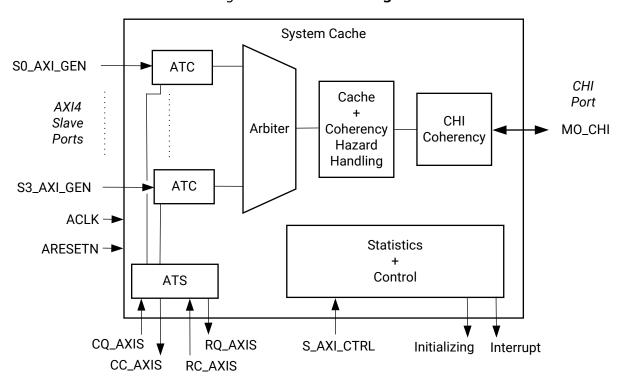

#### **CHI Port Descriptions**

The block diagram of the System Cache core configured for CHI is shown in the following figure. All interfaces are compliant to AXI4, AXI4-Stream or CHI where applicable. The input signals ACLK and ARESETN implement clock and reset for the entire System Cache core. The MO\_CHI interface contains all 6 channels and the separate signals to handle link and system coherency handshake.

Figure 16: CHI Block Diagram

ATS AXI4-Stream Ports

X24854-112620

**Table 15: CHI Interfaces**

| Name                    | Туре               | Description                                               |  |

|-------------------------|--------------------|-----------------------------------------------------------|--|

| ACLK                    | Input              | Core clock                                                |  |

| ARESETN                 | Input              | Synchronous reset of core                                 |  |

| Initializing            | Output             | Core is initializing after reset                          |  |

| Sx_AXI_GEN <sup>1</sup> | AXI4 Slave         | Generic cache port                                        |  |

| S_AXI_CTRL              | AXI4-Lite Slave    | Control port                                              |  |

| M0_CHI                  | CHI                | CHI Interface containing all 6 channels and extra signals |  |

| CQ_AXIS                 | AXI4 Stream Slave  | ATS CQ Interface                                          |  |

| CC_AXIS                 | AXI4 Stream Master | ATS CC Interface                                          |  |

| RC_AXIS                 | AXI4 Stream Slave  | ATS RC Interface                                          |  |

| RQ_AXIS                 | AXI4 Stream Master | ATS RQ Interface                                          |  |

| Interrupt               | Output             | Control interrupt output                                  |  |

Notes:

1. x = 0 to 3

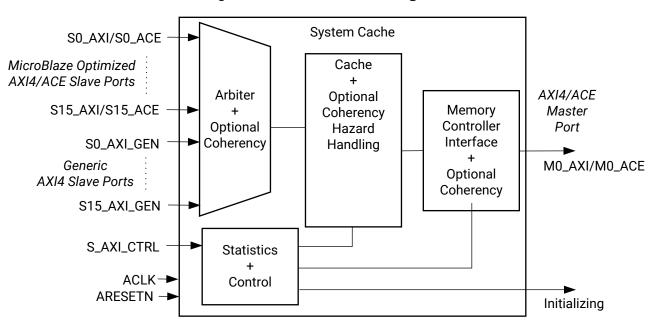

#### **AXI4/ACE Port Descriptions**

The block diagram for the System Cache core is shown in the following figure. All System Cache core interfaces are compliant with AXI4. The input signals ACLK and ARESETN implement clock and reset for the entire System Cache core.

Figure 17: AXI/ACE Block Diagram

X17763-062620

Table 16: I/O Interfaces

| Name                               | Туре            | Description                              |  |

|------------------------------------|-----------------|------------------------------------------|--|

| ACLK                               | Input           | Core clock                               |  |

| ARESETN                            | Input           | Synchronous reset of core                |  |

| Initializing                       | Output          | Core is initializing after reset         |  |

| Sx_AXI <sup>1</sup> , <sup>2</sup> | AXI4 Slave      | MicroBlaze optimized cache port          |  |

| Sx_ACE <sup>1</sup> , <sup>2</sup> | ACE Slave       | MicroBlaze optimized cache coherent port |  |

| Sx_AXI_GEN <sup>1</sup>            | AXI4 Slave      | Generic cache port                       |  |

| M0_AXI <sup>3</sup>                | AXI4 Master     | Memory controller master port            |  |

| M0_ACE <sup>3</sup>                | ACE Master      | Master interface to ACE port on PS       |  |

| S_AXI_CTRL                         | AXI4-Lite Slave | Control port                             |  |

#### Notes:

- 1. x = 0-15

- 2. Sx\_AXI and Sx\_ACE are mutually exclusive.

- 3. M0\_AXI and M0\_ACE are mutually exclusive.

# **Register Space**

In the following tables Access is indicated by R for read-only, W for write-only and R/W for Read/Write.

All registers in the optional Statistics and Control module are 64 bits wide. The address map structure is shown in the following table. The data width of the control interface is configurable to be 32 (default) or 64 bits. For the 32-bit interface a write to a control-type register takes effect on the write to the lower 32-bits. For a 64-bit interface the control register write always takes effect immediately.

# Category

**Table 17: Category Field**

| Address (binary)      | Description                                          |

|-----------------------|------------------------------------------------------|

| 0_00yy_yyxx_xxxx_xx00 | Statistics Functionality for Ports (Optimized ports) |

| 0_01yy_yyxx_xxxx_xx00 | Statistics Functionality for Ports (Generic ports)   |

| 0_1000_00xx_xxxx_xx00 | Statistics Field for Arbiter                         |

| 0_1100_00xx_xxxx_xx00 | Statistics Field for Access                          |

| 0_1100_01xx_xxxx_xx00 | Statistics Field for ATS                             |

| 1_0000_00xx_xxxx_xx00 | Statistics Field for Lookup                          |

| 1_0100_00xx_xxxx_xx00 | Statistics Field for Update                          |

| 1_1000_00xx_xxxx_xx00 | Statistics Field for Backend AXI/ACE                 |

| 1_1001_00xx_xxxx_xx00 | Reserved                                             |

| 1_1001_10xx_xxxx_xx00 | Reserved                                             |

| 1_1010_00xx_xxxx_xx00 | Statistics Field for Backend CCIX/CHI                |

| 1_1100_00xx_xxxx_xx00 | Field for Control                                    |

# **Functionality**

# **Statistics Registers**

#### **Statistics Field for Ports**

Table 18: Statistics Fields for Optimized Port 0

| Offset <sup>1</sup> | Register Name | Access | Format <sup>2</sup> | Description                            |

|---------------------|---------------|--------|---------------------|----------------------------------------|

| 0x0_0000            | RdSegO0       | R      | COUNT               | Segments Per Read Transaction          |

| 0x0_0020            | WrSegO0       | R      | COUNT               | Segments Per Write Transaction         |

| 0x0_0040            | RdInfoQueueO0 | R      | QUEUE               | Read Information Port Queue Statistics |

Table 18: Statistics Fields for Optimized Port 0 (cont'd)

| Offset <sup>1</sup> | Register Name | Access | Format <sup>2</sup> | Description                                |

|---------------------|---------------|--------|---------------------|--------------------------------------------|

| 0x0_0060            | RdDataQueueO0 | R      | QUEUE               | Read Data Port Queue Statistics            |

| 0x0_0080            | BIPInfoQueuO0 | R      | QUEUE               | BRESP Information Port Queue Statistics    |

| 0x0_00A0            | BPQueueO0     | R      | QUEUE               | BRESP Port Queue Statistics                |

| 0x0_00C0            | WrInfoQueueO0 | R      | QUEUE               | Write Information Port Queue Statistics    |

| 0x0_00E0            | WrDataQueueO0 | R      | QUEUE               | Write Data Port Queue Statistics           |

| 0x0_0100            | RdBlockO0     | R      | COUNT               | Read Blocked from Arbitration              |

| 0x0_0120            | WrHitO0       | R      | SCOUNT              | Write Hits                                 |

| 0x0_0140            | WrMissO0      | R      | SCOUNT              | Write Miss                                 |

| 0x0_0160            | WrMissDirtyO0 | R      | SCOUNT              | Write Miss Dirty                           |

| 0x0_0180            | RdHitO0       | R      | SCOUNT              | Read Hit                                   |

| 0x0_01A0            | RdMissO0      | R      | SCOUNT              | Read Miss                                  |

| 0x0_01C0            | RdMissDirtyO0 | R      | SCOUNT              | Read Miss Dirty                            |

| 0x0_01E0            | LockWrHitO0   | R      | SCOUNT              | Locked Write Hit                           |

| 0x0_0200            | LockRdHitO0   | R      | SCOUNT              | Locked Read Hit                            |

| 0x0_0220            | FirstWrHitO0  | R      | SCOUNT              | First Write Hit                            |

| 0x0_0240            | RdLatencyO0   | R      | COUNT               | Read Latency                               |

| 0x0_0260            | WrLatencyO0   | R      | COUNT               | Write Latency                              |

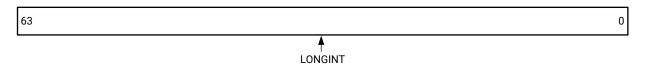

| 0x0_0280            | CRLSO0        | R/W    | LONGINT             | Configuration for read latency statistics  |

| 0x0_02A0            | CWLSO0        | R/W    | LONGINT             | Configuration for write latency statistics |

- 1. Address offset is given for Optimized Port 0. For offset to other per port registers use the formulas:

- Optimized Port x Offset = IP Offset + x \* 0x400, x = 1 to 15

- Generic Port x Offset = IP Offset + x \* 0x400 + 0x4000, x = 1 to 15

- 2. See section Register Records and Formats for details

#### Statistics Field for Arbiter

Table 19: Statistics Field for Arbiter

| Offset   | Register Name    | Access | Format <sup>1</sup> | Description                                               |

|----------|------------------|--------|---------------------|-----------------------------------------------------------|

| 0x0_8000 | ValidArbit       | R      | COUNT               | Arbiter Transaction Clock Cycles after arbitration        |

| 0x0_8020 | ConcurrentAccess | R      | COUNT               | Arbiter Transactions available to select when arbitrating |

#### Notes:

1. See section Register Records and Formats for details

#### **Statistics Field for Access**

**Table 20: Statistics Field for Access**

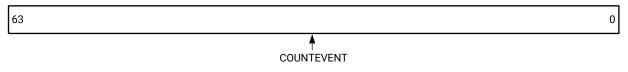

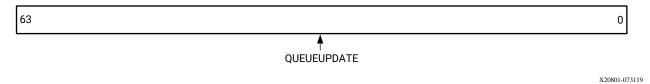

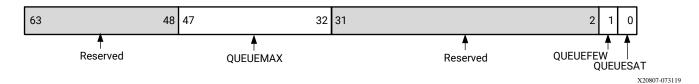

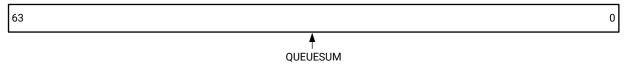

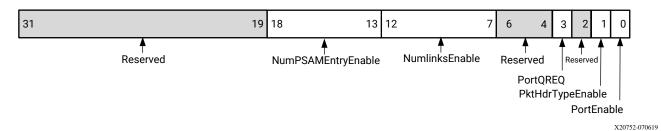

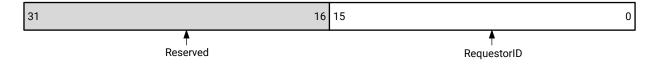

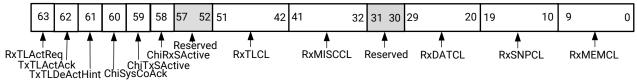

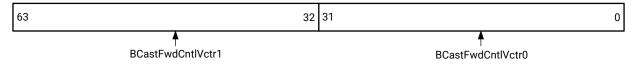

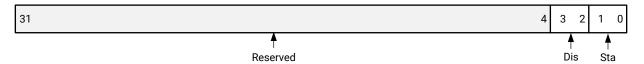

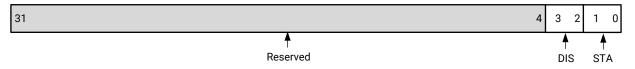

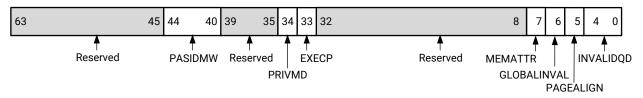

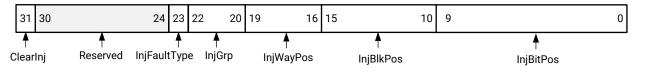

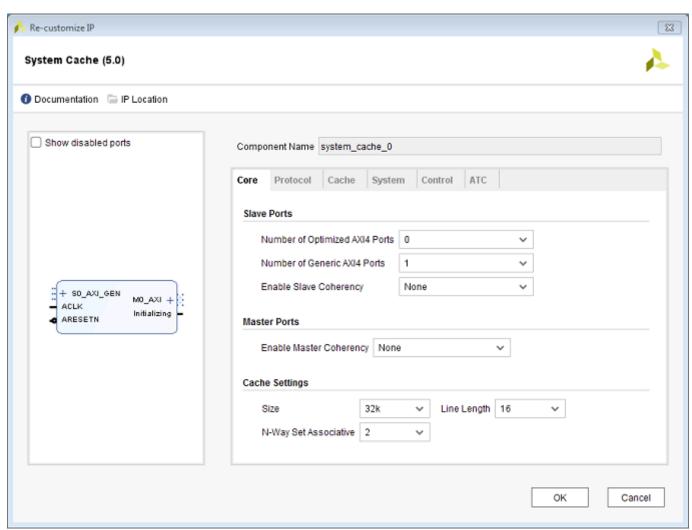

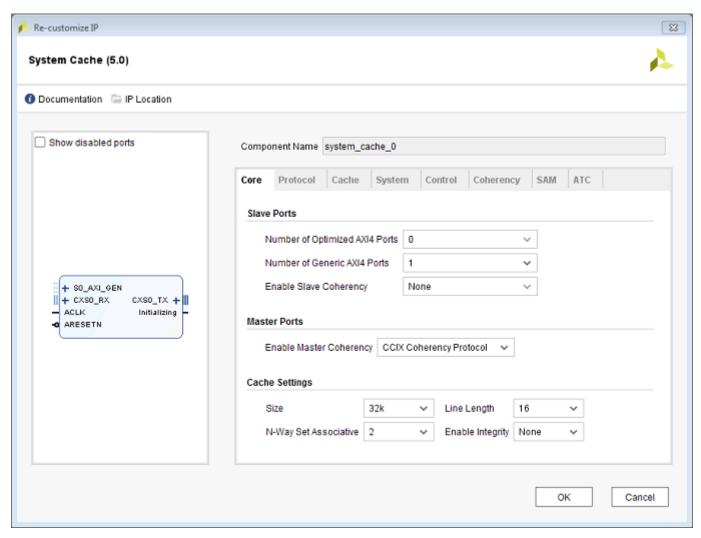

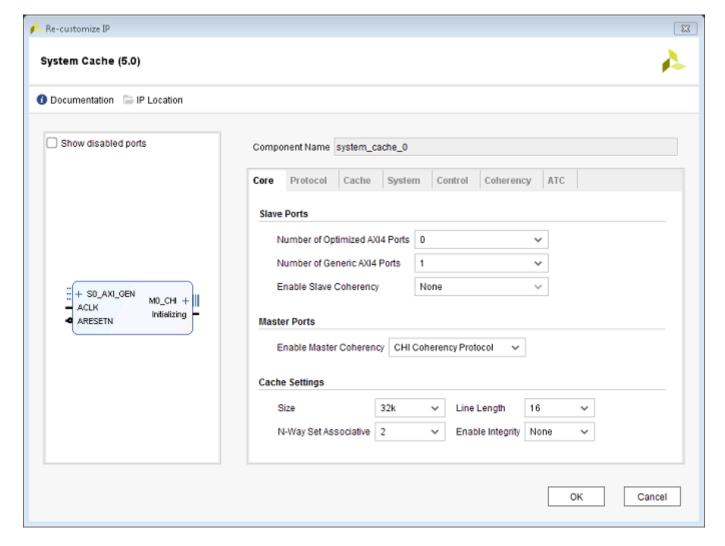

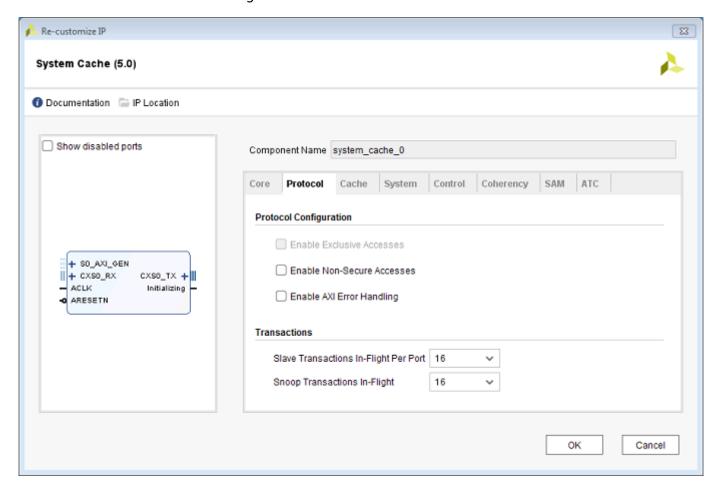

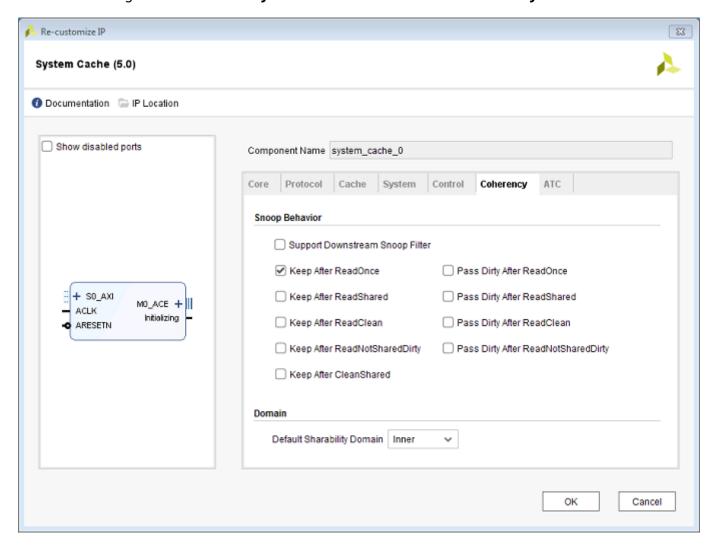

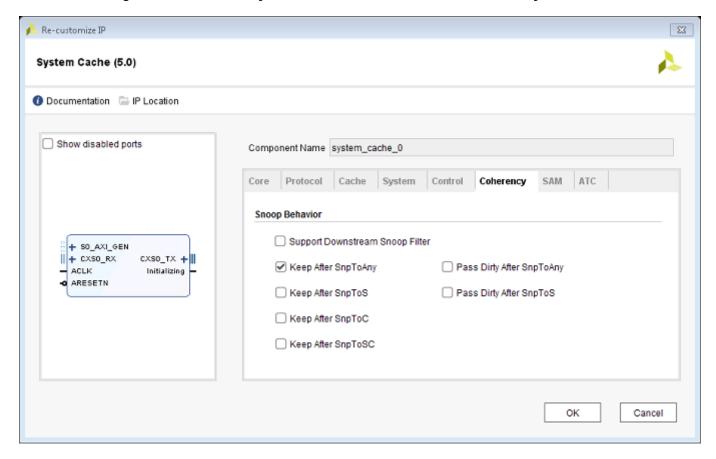

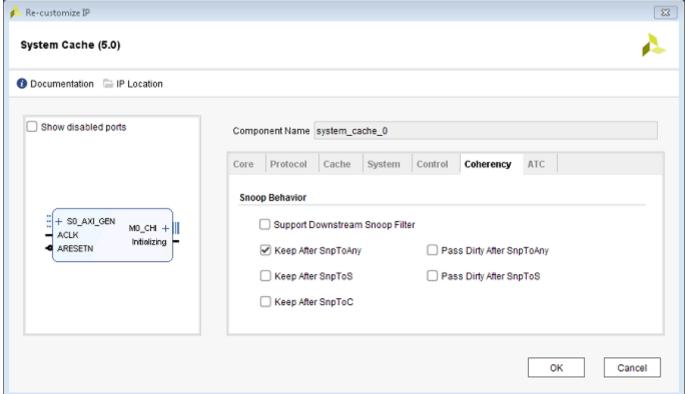

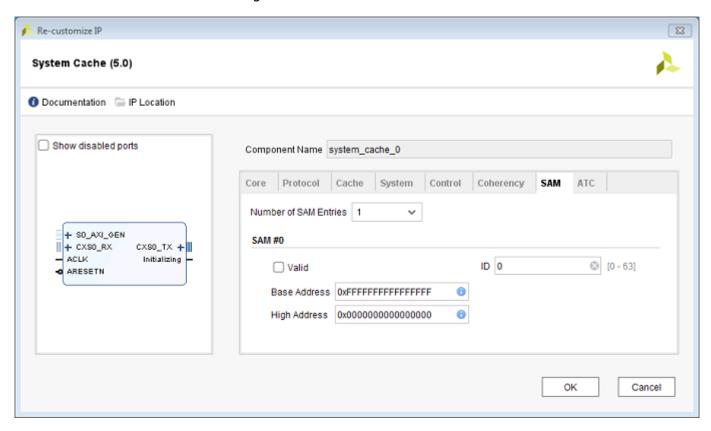

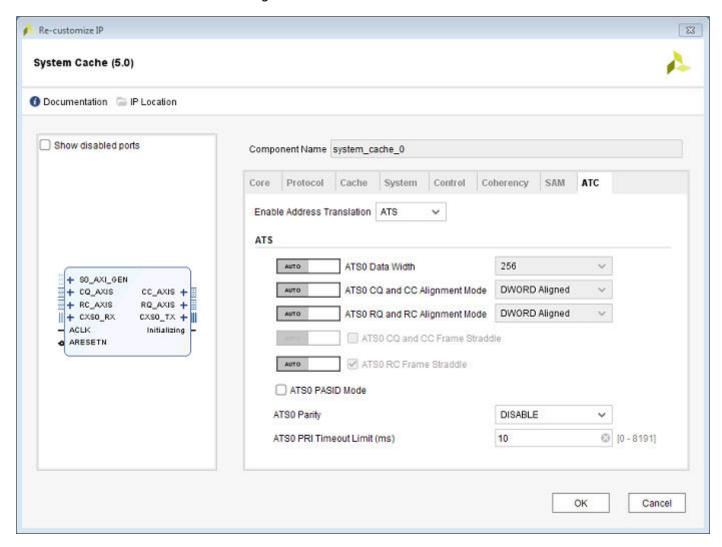

| Offset   | Register Name     | Access | Format <sup>1</sup> | Description                                           |