# Soft-Decision FEC Integrated Block v1.1

# LogiCORE IP Product Guide

Vivado Design Suite

PG256 (v1.1) February 4, 2021

# **Table of Contents**

| Chapter 1: IP Facts                             | 4  |

|-------------------------------------------------|----|

| Features                                        | 4  |

| IP Facts                                        | 7  |

| Chapter 2: Overview                             | 8  |

| Applications                                    | 8  |

| Licensing and Ordering                          | 8  |

| Chapter 3: Product Specification                | 10 |

| Modes of Operation                              | 11 |

| Standards                                       | 12 |

| Performance                                     | 12 |

| Port Descriptions                               | 13 |

| Register Space                                  | 17 |

| AXI4-Stream Interface Definition                | 33 |

| Chapter 4: Designing with the Core              | 50 |

| Clocking                                        |    |

| Resets                                          |    |

| 5G New Radio Block Length                       |    |

| Interrupt                                       |    |

| Interface FIFOs                                 |    |

| Interface Dependencies                          |    |

| Parameter Management                            |    |

| LDPC Code Support                               |    |

| LDPC Code Memory Error Detection and Correction |    |

| Interface Protocols                             |    |

| Throughput Limits of Interfaces                 |    |

| Chapter 5: Design Flow Steps                    | 69 |

| Customizing and Generating the Core             |    |

| Constraining the Core                           |    |

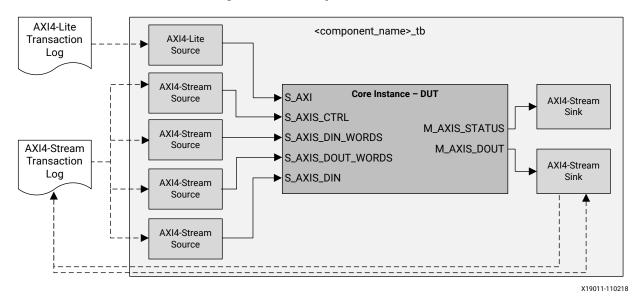

| Simulation                                         | 82  |

|----------------------------------------------------|-----|

| Synthesis and Implementation                       | 82  |

| Chapter 6: C Model                                 | 85  |

| Unpacking and Model Contents                       |     |

| Installation                                       |     |

| C Model Interface                                  |     |

| MATLAB Interface                                   | 93  |

| Chapter 7: Example Design                          | 95  |

| Simulation-Only Example Design                     | 95  |

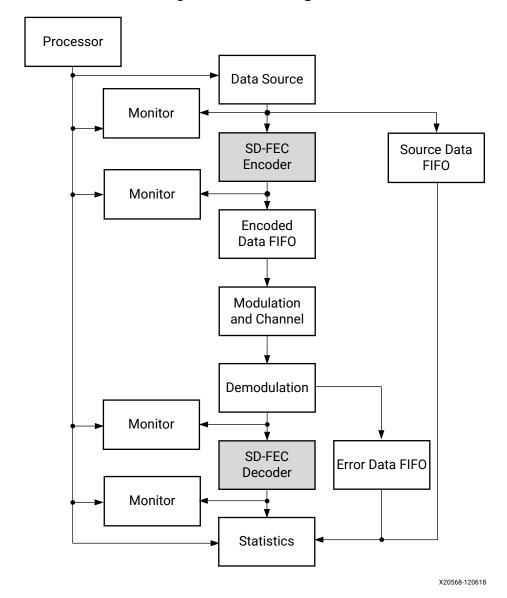

| Processor-Based Example Design                     | 96  |

| Appendix A: Upgrading                              | 103 |

| Appendix B: Debugging                              | 104 |

| Finding Help on Xilinx.com                         |     |

| Debug Tools                                        | 105 |

| Simulation Debug                                   | 106 |

| Hardware Debug                                     | 108 |

| Interface Debug                                    | 108 |

| Appendix C: SD-FEC Low-Level Bare-Metal Driver     | 110 |

| Overview                                           | 110 |

| Data Structures                                    | 111 |

| User API                                           | 113 |

| Interrupt Handling                                 | 117 |

| Examples                                           | 117 |

| Appendix D: Additional Resources and Legal Notices | 120 |

| Xilinx Resources                                   | 120 |

| Documentation Navigator and Design Hubs            | 120 |

| References                                         | 120 |

| Revision History                                   | 121 |

| Plassa Paad: Important Logal Notices               | 122 |

# **IP Facts**

The Soft-Decision Forward Error Correction (SD-FEC) Integrated Block supports Low Density Parity Check (LDPC) decoding and encoding and turbo code decoding. The LDPC codes used are highly configurable, and the specific code used can be specified on a codeword-by-codeword basis. The SD-FEC Integrated Block IP core is extremely flexible, allowing many unique custom LDPC codes to be used.

### **Features**

The SD-FEC core is a highly flexible soft-decision FEC decoder and LDPC encoder offering the following features:

- Function configurable between either:

- LDPC decode or encode of customer-specified Quasi-cyclic (QC) codes, including standard and custom, or

- Turbo decode of codes used by LTE

- Peak throughput of the order:

- . 1.78 Gb/s turbo decode @ 6 iterations

- 2.84 Gb/s for LDPC decode @ 8 iterations

- <sub>o</sub> 19.82 Gb/s for LDPC encode

- Scalable implementation

- Multiple instantiations on a device (see Placement Location Guidelines for SD-FEC IP Core)

- High bandwidth AXI4-Stream interfaces

**Note:** Throughput depends on the codes and how they are mixed and the actual clock frequency on the device. See Clocking for further details.

#### **Related Information**

Placement Location Guidelines for SD-FEC IP Core Clocking

# LDPC Decoding/Encoding

- Highly configurable codes

- A range of quasi-cyclic codes can be configured over an AXI4-Lite interface

- Code parameter memory can be shared across up to 128 codes

- Codes can be selected on a block-by-block basis

- Encoder can re-use suitable decoder codes

- Normalized min-sum decoding algorithm

- Normalization factor programmable (from 0.0625 to 1 in steps of 0.0625) for layers

- Number of iterations between 1 and 63

- Specified for each block using the AXI4-Stream control interface

- Early termination

- Specified for each block to be none, one, or both of the following:

- Parity check passes

- No change in hard information or parity bits since last iteration

- Soft or hard outputs

- Specified for each block to include information and optional parity

- 6-bit soft log-likelihood ratio (LLR) input (8-bit interface, two fractional bits, with external saturation before input to symmetric range -7.75 to +7.75 assumed) and 8-bit output

- In- or out-of-order execution of blocks, with user specified ID field to identify blocks

- Encoder and decoder variants, with optional support for improved throughput when submatrix size is small

- Optional final parity check to update parity pass/fail for final output

- Optional initialization of codes from device configuration, avoiding download using AXI4-Lite interface

- Support logic for 5G NR provides code generation and download to SD-FEC internal memory during run-time and initialization

- Support logic for non-5G provides code generation and download to SD-FEC internal memory during initialization

### **Turbo Decoding**

Max, Max Scale (scale factor is programmable as a multiple of 0.0625), or Max Star

- Number of iterations between 1 and 63

- Specified for each block using the AXI4-Stream control interface

- Early termination

- Specified for each block to be none, one, or both of the following:

- No change in hard decision since last iteration

- CRC pass

- Soft or hard outputs

- $_{\circ}$  Specified for each block to include systematic and optionally parity 0 and parity 1

- 8-bit soft LLR on input and output (8-bit interface, two fractional bits, with external saturation before input to symmetric range -31.75 to +31.75 is assumed)

### **Interfaces**

- Separate clocks on each interface to ease integration

- Wide data interfaces on input and output with configurable support for 1, 2, or 4 lanes

- Ability to specify number of inputs and outputs on each lane on either a block-by-block basis, or transfer basis

- Separate inputs to specify control parameters and receive status output on a block-by-block basis

### **IP Facts**

| LogiCORE IP Facts Table              |                                                                            |  |  |

|--------------------------------------|----------------------------------------------------------------------------|--|--|

|                                      | Core Specifics                                                             |  |  |

| Supported Device Family <sup>1</sup> | Zynq® UltraScale+™ RFSoC                                                   |  |  |

| Supported User Interfaces            | AXI4-Lite, AXI4-Stream                                                     |  |  |

| Resources                            | Performance and Resource Utilization web page                              |  |  |

|                                      | Provided with Core                                                         |  |  |

| Design Files                         | Encrypted RTL                                                              |  |  |

| Example Design                       | IP integrator Block Diagram                                                |  |  |

| Test Bench                           | Verilog                                                                    |  |  |

| Constraints File                     | Xilinx® Design Constraints (XDC)                                           |  |  |

| Simulation Model                     | System Verilog SecureIP model                                              |  |  |

|                                      | C numerical model                                                          |  |  |

| Supported S/W Driver <sup>2</sup>    | Standalone                                                                 |  |  |

|                                      | Linux                                                                      |  |  |

|                                      | Tested Design Flows <sup>3</sup>                                           |  |  |

| Design Entry                         | Vivado® Design Suite                                                       |  |  |

| Simulation                           | For supported simulators, see the Xilinx Design Tools: Release Notes Guide |  |  |

| Synthesis                            | Vivado                                                                     |  |  |

| Support                              |                                                                            |  |  |

| Release Notes and Known Issues       | Master Answer Record: 70720                                                |  |  |

| All Vivado IP Change Logs            | Master Vivado IP Change Logs: 72775                                        |  |  |

| Xilinx Support web page              |                                                                            |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog.

- 2. Standalone driver details can be found in <Install Directory>/Vitis/2019.2/data/embeddedsw/XilinxProcessorIPLib/drivers/.

- Linux: Linux OS and driver support information is available from the Linux SD-FEC Driver page.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

Forward Error Correction (FEC) codes such as Low Density Parity Check (LDPC) and turbo codes provide a means to control errors in data transmissions over unreliable or noisy communication channels. The SD-FEC Integrated Block provides an optimized block for soft-decision decoding of these codes. Fixed turbo codes, as used by LTE, are supported directly, whereas custom and standardized LDPC codes are supported through the ability to specify the parity check matrix through an AXI4-Lite bus or using the optional programmable logic (PL)-based support logic.

# **Applications**

The SD-FEC Integrated Block is intended for use in applications requiring LTE turbo decoding or LDPC encode/decode using QC-based codes, such as 5G wireless, DOCSIS 3.1 cable modems, backhaul, and any other applications employing custom QC codes such as backhaul.

- 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; NR;

Multiplexing and channel coding (Release 15) (3GPP Std TS 38.212 V15.0.0)

- Data-Over-Cable Service Interface Specifications DOCSIS 3.1, Physical Layer Specification (DOCSIS 3.1)

#### **Related Information**

LDPC Code Overview

# **Licensing and Ordering**

This Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP module is provided at no additional cost with the Xilinx Vivado<sup>®</sup> Design Suite under the terms of the Xilinx End User License.

Registration is required to obtain the license.

Information about other Xilinx<sup>®</sup> LogiCORE<sup>™</sup> IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

France Telecom, for itself and certain other parties, claims certain intellectual property rights covering Turbo Codes technology, and has decided to license these rights under a licensing program called the Turbo Codes Licensing Program. Supply of this IP core does not convey a license nor imply any right to use any Turbo Codes patents owned by France Telecom, TDF or GET. Contact France Telecom for information about its Turbo Codes Licensing Program at the following address: France Telecom R&D, VAT/TURBOCODES, 38, rue du Général Leclerc, 92794 Issy Moulineaux, Cedex 9, France.

# **Product Specification**

A block diagram of the SD-FEC Integrated Block is shown in the following figure, which includes the high speed clock (667 MHz) domain and the Clock Domain Crossing (CDC) blocks. Optional Support logic is provided around the SD-FEC block to configure it; for 5G NR the optional logic provides support for both initialization and run-time configuration and for non-5G NR it provides support for initialization only. The optional support logic is generated using the Vivado<sup>®</sup> Integrated Design Environment. The optional support logic and SD-FEC block are referred to as the SD-FEC core.

AXI4-Lite Turbo/LDPC Mode Parameter Bus Interfaces On/Off (PARAM) •LDPC Code Description 32b AXI4-Lite Slave **Optional Support Logic** SD-FEC Block CDC **Parameters** LDPC Decoder/ **AXI MM** Interface Encoder 32b/40b 32b 32b/40b 32b CDC CTRL STĂTUS Configurable Shared Memory DIN\_WORDS — Sub-system 32b DOUT\_ WORDS 0/P 8b Interface I/P 512b DIN 512b 128b 128b DOUT Turbo Decoder High Speed Clock Domain Up to 16 LLRs per For Turbo up to 12 LLRs cycle @ 667 MHz per cycle @ 667 MHz Key: 1x, 2x, 4x Width AXI4-Stream (per sample) Conversion & Clock AXI4-Stream (per block) Domain crossing AXI4-Lite Internal Memory Bus CDC **Clock Domain Crossing** (arrow shows direction of data flow) X17336-112718

Figure 1: SD-FEC Core Interfaces

The SD-FEC core provides:

- Turbo Decode for LTE

- LDPC decode for a wide range of user-defined codes

- LDPC encode for a wide range of user-defined codes

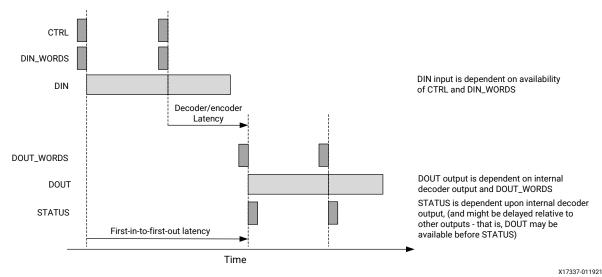

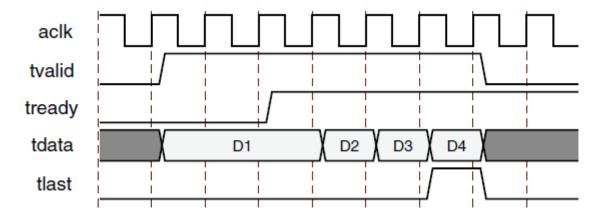

The core uses AXI4 interfaces. A single AXI4-Lite memory mapped bus is used for parameters, such as LDPC code definitions, that persist for more than one block, and AXI4-Stream interfaces are used to provide data on a sample-by-sample basis (for example, DIN), or block-by-block basis (for example, CTRL). These interfaces provide handshake signals in addition to data. Further details are given in the AXI4-Stream Interface section. Data input and output buffers provide some scope to overlap input and output with encoder/decoder operation.

As shown in the previous figure, the internals of the SD-FEC core operate off a high speed clock, whereas the interfaces have their own clocks for ease of integration. Clock Domain Crossing (CDC) is provided on all interfaces and the data interfaces include width conversion to maintain high bandwidth with lower interface clock frequency. Specifically, the high speed clock domain has a 128-bit data interface capable of carrying up to 16 8-bit LLRs per clock cycle of the core, but the block has a 512-bit data interface, which allows up to four 128-bit samples to be time division multiplexed onto the core interface. This number can be configured to 1, 2, or 4 (using the AXI4-Lite interface), and if configured to 4, for example, it allows the interface clock rate to be reduced by a factor of four relative to the core clock while maintaining maximum bandwidth.

**Note:** DIN\_WORDS and DOUT\_WORDS have a more advanced mode of operation, where the number of elements is specified for each transfer over DIN or DOUT. This is supported by width conversion.

#### **Related Information**

**AXI4-Stream Interface**

# **Modes of Operation**

The SD-FEC IP core operates in two modes, 5G New Radio (NR) and non-5G NR.

### **5G New Radio**

In 5G NR mode, the SD-FEC IP core support logic internally handles the run-time configuration of the LDPC code and shared LDPC code parameters. On receiving a particular code definition through the AXI4-Stream control interface, the support logic generates LDPC code and shared LDPC code parameters for the given LDPC code and then downloads them to the SD-FEC internal memory. In this mode, do not write LDPC code and shared LDPC code parameters using the AXI4-Lite interface because any writes makes the behavior unpredictable.

**Note:** For this mode, ensure that both the CTRL (bit-0 and STATUS (bit-3) bits in the AXIS\_ENABLE register are set to 1. Writing any other value to the CTRL (bit-0) makes the behavior unpredictable.

### Non-5G New Radio

This is further classified into initialized and run-time configured modes.

### Run-time Configured Non-5G New Radio Mode

In this mode the core is configured at run-time using the AXI4-Lite parameter interface and the AXI4-Stream control interface for either turbo decode or LDPC encode or decode.

#### **Initialized Non-5G New Radio Mode**

In this mode the core support logic generates initialization and configuration parameters at start up from the options set in the Vivado<sup>®</sup> IDE for either turbo decode or LDPC encode or decode. In this mode and for LDPC, do not write LDPC code and shared LDPC code parameters using the AXI4-Lite parameter interface because any write can overwrite the initialized codes and make the behavior unpredictable.

### **Standards**

- Turbo decode required by the LTE standard is defined in:

- 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA); Multiplexing and channel coding (Release 15) (3GPP Std TS 36.212 V15.0.1)

- LDPC codes required for the following standards are provided by the core:

- IEEE Standard for Information technology Local and Metropolitan area Network Standards (IEEE Std 802.11)

- Data-Over-Cable Service Interface Specifications DOCSIS 3.1, Physical Layer Specification (DOCSIS 3.1)

- 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; NR; Multiplexing and channel coding (Release 15) (3GPP Std TS 38.212 V15.0.0)

### **Performance**

For details on the clock frequency supported by a device and resource utilization, visit the Performance and Resource Utilization web page.

### Throughput and Latency

To view the throughput and latency figures for 5G New Radio, WiFi 802.11ac, and DOCSIS 3.1, for LDPC encoding and decoding, and the figures for turbo decoding, visit the Throughput and Latency web page.

#### **Related Information**

**LDPC Block Interleaving**

### **BER Performance**

To view the BER plots for 5G New Radio, WiFi 802.11ac, DOCSIS 3.1, for LDPC encoding and decoding, and the BER plots for turbo decoding, visit the BER Performance web page.

# **Port Descriptions**

The following tables shows the core pinout.

### **Global Core Ports**

Table 1: Global Core Ports

| Signal                 | I/O | Clock<br>Domain | Description                                                                     |

|------------------------|-----|-----------------|---------------------------------------------------------------------------------|

| reset_n                | I   | None            | Master asynchronous reset                                                       |

| core_clk               | I   | core_clk        | Main processing clock for processing core                                       |

| interrupt <sup>1</sup> | 0   | s_axi_aclk      | Indicates error conditions. Behavior controlled by interrupt control registers. |

#### Notes:

# **Data Input Ports (DIN)**

The data input bus (DIN) is an AXI4-Stream slave interface. The data input bus uses the  $s_axis_din_aclk$  clock.

**Table 2: Data Input Ports**

| Port              | I/O |

|-------------------|-----|

| s_axis_din_aclk   | I   |

| s_axis_din_tvalid | I   |

<sup>1.</sup> The interrupt pin is present if the S\_AXI parameter interface is *not* set to Initialized or any interrupt source is enabled.

Table 2: Data Input Ports (cont'd)

| Port                                              | I/O |

|---------------------------------------------------|-----|

| s_axis_din_tready                                 | 0   |

| s_axis_din_tlast                                  | I   |

| s_axis_din_tdata[128*(LANE_NUM_IN) <sup>1</sup> ] | I   |

#### **Related Information**

Data Input (DIN)

**Throughput Limits of Interfaces**

# **Data Input Control Ports (DIN\_WORDS)**

The data input control bus (DIN\_WORDS) controls the number of words on the data input bus (DIN). It is an AXI4-Stream slave interface. The data input control bus uses the <code>s\_axis\_din\_words\_aclk</code> clock. Ports associated with <code>DIN\_WORDS</code> interface are present if <code>DIN\_Interface</code> is set to Unconfigured, or <code>DIN\_Interface</code> is set to Pre-Configured and <code>DIN\_Words\_Configuration</code> is set to Per\_Block or Per\_Transaction (that is, the interface is not Fixed).

**Table 3: Data Input Control Ports**

| Port                                                   | I/O |

|--------------------------------------------------------|-----|

| s_axis_din_words_aclk                                  | I   |

| s_axis_din_words_tvalid                                | I   |

| s_axis_din_words_tready                                | 0   |

| s_axis_din_words_tlast                                 | I   |

| s_axis_din_words_tdata[8*(LANE_NUM_IN) <sup>12</sup> ] | I   |

#### Notes:

- 1. Width is 8 bits when word configuration is Per Block.

- 2. LANE\_NUM\_IN is the number of lanes configured using AXIS\_WIDTH.DIN.

#### **Related Information**

Data Input Control (DIN\_WORDS)

# **Data Output Ports (DOUT)**

The data output bus (DOUT) is an AXI4-Stream master interface. The data output bus uses the  $m_axis_dout_aclk$  clock.

<sup>1.</sup> LANE\_NUM\_IN is the number of lanes configured using AXIS\_WIDTH.DIN.

**Table 4: Data Output Ports**

| Port                                                | I/O |

|-----------------------------------------------------|-----|

| m_axis_dout_aclk                                    | I   |

| m_axis_dout_tvalid                                  | 0   |

| m_axis_dout_tready                                  | I   |

| m_axis_dout_tlast                                   | 0   |

| m_axis_dout_tdata[128*(LANE_NUM_OUT) <sup>1</sup> ] | 0   |

1. LANE\_NUM\_OUT is the number of lanes configured using AXIS\_WIDTH.DOUT.

#### **Related Information**

Data Output (DOUT)

Throughput Limits of Interfaces

### **Data Output Control Ports (DOUT\_WORDS)**

The data output control port bus (DOUT\_WORDS) controls the number of words on the data output bus. It is an AXI4-Stream slave interface. The data output control port bus uses the <code>s\_axis\_dout\_words\_aclk</code> clock. Ports associated with the <code>DOUT\_WORDS</code> interface are present if <code>DOUT\_Interface</code> is set to Unconfigured, or <code>DOUT\_Interface</code> is set to Pre-Configured and <code>DOUT\_Words\_Configuration</code> is set to Per\_Block or Per\_Transaction (that is, the interface is not Fixed).

**Table 5: Data Output Control Ports**

| Port                                                     | I/O |

|----------------------------------------------------------|-----|

| s_axis_dout_words_aclk                                   | I   |

| s_axis_dout_words_tvalid                                 | I   |

| s_axis_dout_words_tready                                 | 0   |

| s_axis_dout_words_tlast                                  | I   |

| s_axis_dout_words_tdata[8*(LANE_NUM_OUT) <sup>12</sup> ] | I   |

#### Notes:

- 1. Width is 8 bits when word configuration is Per Block.

- 2. LANE\_NUM\_OUT is the number of lanes configured using AXIS\_WIDTH.DOUT.

#### **Related Information**

Data Output Control (DOUT\_WORDS)

### **Control Input Ports (CTRL)**

The control input bus (CTRL) is an AXI4-Stream slave interface. The control input bus uses the  $s_axis_ctrl_aclk$  clock. The control input provides information specific to each block. Its definition depends on whether 5G NR standard support is selected in the Vivado® IDE.

**Table 6: Control Input Ports**

| Port                                  | I/O |

|---------------------------------------|-----|

| s_axis_ctrl_aclk                      | I   |

| s_axis_ctrl_tvalid                    | I   |

| s_axis_ctrl_tready                    | 0   |

| s_axis_ctrl_tdata[32/40] <sup>1</sup> | I   |

#### Notes:

#### **Related Information**

Control Input (CTRL)

### **Status Output Ports (STATUS)**

The status output bus (STATUS) is an AXI4-Stream master interface. The status output bus uses the  $m_axis_status_aclk$  clock. The status output provides information specific to each block. Its definition depends on whether 5G NR standard support is selected in the Vivado® IDE.

**Table 7: Status Output Ports**

| Port                                    | I/O |

|-----------------------------------------|-----|

| m_axis_status_aclk                      | I   |

| m_axis_status_tvalid                    | 0   |

| m_axis_status_tready                    | I   |

| m_axis_status_tdata[32/40] <sup>1</sup> | 0   |

#### Notes:

### **Related Information**

Status Output (STATUS)

<sup>1. 40</sup> bits if Standard is set to 5G, otherwise 32 bits.

<sup>1. 40</sup> bits if Standard is set to 5G, otherwise 32 bits.

### **Parameter Ports (PARAM)**

The parameter bus is an AXI4-Lite memory-mapped slave interface. The parameter bus uses the  $s_{axi_aclk}$  clock. The AXI4-Lite interface is present when Parameter\_Interface is not set to Initialized.

The parameter bus allows two outstanding transactions on the write interface, and one outstanding transaction on the read interface. The higher number of outstanding transactions on the write interface improves the write download throughput, allowing an LDPC code to be updated more quickly.

**Table 8: Parameter Ports**

| Port               | I/O |

|--------------------|-----|

| s_axi_aclk         | I   |

| s_axi_awaddr[17:0] | I   |

| s_axi_awvalid      | I   |

| s_axi_awready      | 0   |

| s_axi_wdata[31:0]  | I   |

| s_axi_wvalid       | I   |

| s_axi_wready       | 0   |

| s_axi_bready       | I   |

| s_axi_bvalid       | 0   |

| s_axi_araddr[17:0] | I   |

| s_axi_arvalid      | I   |

| s_axi_arready      | 0   |

| s_axi_rready       | I   |

| s_axi_rdata[31:0]  | 0   |

| s_axi_rvalid       | 0   |

# **Register Space**

**IMPORTANT!** Registers should be programmed through a device driver (this generates correct values from simple definitions of LDPC codes). The driver is provided by Xilinx.

The register map consists of the following types of parameters:

- Core Parameters (common to all codes)

- Turbo Code Parameters

- LDPC Code Parameters (per code)

- Shared LDPC Code Parameters

All registers start on 32-bit word aligned addresses. The two LSBs of the read and write addresses are assumed to be zero. Register read write access restrictions are summarized in the following sections. Further details of how code parameters might be managed are provided under Parameter Management.

**Table 9: Register Space**

| Address (Hex)    | Register Name                    |  |

|------------------|----------------------------------|--|

| Core Par         | ameters                          |  |

| 0x00             | AXI_WR_PROTECT Register          |  |

| 0x04             | CODE_WR_PROTECT Register         |  |

| 0x08             | ACTIVE Register                  |  |

| 0x0C             | AXIS_WIDTH Register              |  |

| 0x10             | AXIS_ENABLE Register             |  |

| 0x14             | FEC_CODE Register                |  |

| 0x18             | ORDER Register                   |  |

| 0x1C             | Interrupt Status Register (ISR)  |  |

| 0x20             | Interrupt Enable Register (IER)  |  |

| 0x24             | Interrupt Disable Register (IDR) |  |

| 0x28             | Interrupt Mask Register (IMR)    |  |

| 0x2C             | ECC Interrupt Status Register    |  |

| 0x30             | ECC Interrupt Enable Register    |  |

| 0x34             | ECC Interrupt Disable Register   |  |

| 0x38             | ECC Interrupt Mask Register      |  |

| 0x3C             | BYPASS Register                  |  |

| Turbo Code       | Parameters                       |  |

| 0x100            | Turbo Code Register              |  |

| LDPC Code        | Parameters                       |  |

| 0x2000+CODE*0x10 | REG0 Register                    |  |

| 0x2004+CODE*0x10 | REG1 Register                    |  |

| 0x2008+CODE*0x10 | REG2 Register                    |  |

| 0x200C+CODE*0x10 | REG3 Register                    |  |

| Shared LDPC Co   | ode Parameters                   |  |

| 0x10000-0x103FC  | SC_TABLE Register                |  |

| 0x18000-0x18FFC  | LA_TABLE Register                |  |

| 0x20000-0x27FFC  | QC_TABLE Register                |  |

### **Related Information**

Parameter Management

### **Core Parameters**

Readable core parameters can be read at any time when the core is out of reset.

**Note:** Any restrictions regarding when a core parameter can be written, are provided as table notes in the relevant parameter tables.

### AXI\_WR\_PROTECT Register (0x00)

Table 10: AXI\_WR\_PROTECT Register

| Bit | Default<br>Value | Access Type | Description                                                                |

|-----|------------------|-------------|----------------------------------------------------------------------------|

| 0   | 0                | R/W         | Prevents write to all other registers. 0: Write allowed 1: Write protected |

#### Notes:

### CODE\_WR\_PROTECT Register (0x04)

Table 11: CODE\_WR\_PROTECT Register

| Bit | Default<br>Value | Access Type | Description                                                                                                                                                                               |

|-----|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0                | R/W         | Prevents write to turbo code and LDPC code registers and shared LDPC code tables Both CODE_WR_PROTECT and AXI_WR_PROTECT must be 0 to enable writes.  0: Write allowed 1: Write protected |

#### Notes:

### ACTIVE Register (0x08)

**Table 12: ACTIVE Register**

| Bit | Default<br>Value | Access Type | Description                          |

|-----|------------------|-------------|--------------------------------------|

| 0   | 0                | RO          | Activity of the decoder.             |

|     |                  |             | 0: No outstanding blocks in the core |

|     |                  |             | 1: The core is working on a block    |

For 5G mode to function properly, this register must be set to 0: Write allowed (if not already set by the Vivado® IDE) before the first CTRL word is applied.

<sup>1.</sup> For 5G mode to function properly, this register *must* be set to 0: Write allowed (if not already set by the Vivado® IDE) before the first CTRL word is applied.

### AXIS\_WIDTH Register (0x0C)

Table 13: AXIS\_WIDTH Register

| Bit | Default<br>Value | Access Type | Description                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | 0                | R/W         | DOUT_WORDS                                                                                                                                                                                                                                                                                                                                   |

|     |                  |             | 0: The DOUT_WORDS input is block based. Only one value is input per block on DOUT_WORDS, and this specifies the number of LLRs in each 128-bit lane for a complete block (for example, a value of 16 on DOUT_WORDS indicates that all 128 bits of each lane of DOUT should be used).                                                         |

|     |                  |             | 1: The DOUT_WORDS input is supplied for each AXI transaction on DOUT. For every AXI transaction on DOUT there must be a corresponding transaction on DOUT_WORDS. If DOUT_WIDTH is set to use multiple lanes, then DOUT_WORDS must provide a value for each 128-bit lane as given in the table in LLR Output Words (DOUT_WORDS).              |

| 4:3 | 0                | R/W         | DOUT: Width conversion applied to DOUT and DOUT_WORDS data                                                                                                                                                                                                                                                                                   |

|     |                  |             | 0: 1x128b                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 1: 2x128b                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 2: 4x128b                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 3: Reserved                                                                                                                                                                                                                                                                                                                                  |

| 2   | 0                | R/W         | DIN_WORDS                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 0: The DIN_WORDS input is block based. Only one value is input per block on DIN_WORDS, and this specifies the number of LLRs in each 128-bit lane for a complete block (for example, a value of 16 on DIN_WORDS indicates that all 128 bits of each lane of DIN should be used).                                                             |

|     |                  |             | 1: The DIN_WORDS input is supplied for each AXI transaction on DIN. For every AXI transaction on DIN there must be a corresponding transaction on DIN_WORDS. If DIN_WIDTH is set to use multiple lanes, then DIN_WORDS must provide a value for each 128-bit lane as given in the table in Data Input Control AXI4-Stream Slave (DIN_WORDS). |

| 1:0 | 0                | R/W         | DIN: Width conversion applied to DIN and DIN_WORDS data                                                                                                                                                                                                                                                                                      |

|     |                  |             | 0: 128b                                                                                                                                                                                                                                                                                                                                      |

|     |                  |             | 1: 2x128b                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 2: 4x128b                                                                                                                                                                                                                                                                                                                                    |

|     |                  |             | 3: Reserved                                                                                                                                                                                                                                                                                                                                  |

#### Notes:

1. This register should only be changed after reset when the interfaces are disabled.

### **Related Information**

Data Output Control (DOUT\_WORDS)

Data Input Control (DIN\_WORDS)

### AXIS\_ENABLE Register (0x10)

Table 14: AXIS\_ENABLE Register

| Bit | Default<br>Value | Access Type | Description                                                                                                         |

|-----|------------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| 5   | 0                | R/W         | DOUT_WORDS: Deasserts ready out and valid internally on DOUT_WORDS to disable input.  0: Disabled 1: Enabled        |

| 4   | 0                | R/W         | DOUT: Deasserts valid out and ready internally on DOUT to disable output.  0: Disabled 1: Enabled                   |

| 3   | 0                | R/W         | STATUS <sup>1</sup> : Deasserts valid out and ready internally on STATUS to disable output.  0: Disabled 1: Enabled |

| 2   | 0                | R/W         | DIN_WORDS: Deasserts ready out and valid internally on DIN_WORDS to disable input.  0: Disabled 1: Enabled          |

| 1   | 0                | R/W         | DIN: Deasserts ready out and valid internally on DIN to disable input. 0: Disabled 1: Enabled                       |

| 0   | 0                | R/W         | CTRL <sup>2</sup> : Deasserts ready out and valid internally on CTRL to disable input.  0: Disabled 1: Enabled      |

#### Notes:

- 1. For 5G mode to function properly, STATUS *must* be set to Enabled (if not already set by the Vivado® IDE) before the first CTRL word is applied.

- 2. For 5G mode to function properly, CTRL *must* be set to Enabled (if not already set by the Vivado IDE) before the first CTRL word is applied.

### FEC\_CODE Register (0x14)

Table 15: FEC\_CODE Register

| Bit | Default<br>Value | Access Type | Description         |

|-----|------------------|-------------|---------------------|

| 0   | 0                | R/W         | FEC code to be used |

|     |                  |             | 0: Turbo code       |

|     |                  |             | 1: LDPC code        |

#### Notes:

1. This register should only be changed when the core is not active (ACTIVE is 0).

### **ORDER Register (0x18)**

**Table 16: ORDER Register**

| Bit | Default<br>Value | Access Type | Description                                                           |

|-----|------------------|-------------|-----------------------------------------------------------------------|

| 0   | 0                | R/W         | Specifies whether the order of blocks can change from input to output |

|     |                  |             | 0: Maintain order<br>1: Out-of-order                                  |

#### Notes:

### Interrupt Status Register (ISR) (0x1C)

**Table 17: Interrupt Status Register**

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                 |

|------------------|------------------|-------------|-----------------------------|

| 5                | 0                | R/W         | DOUT_WORDS tlast unexpected |

| 4                | 0                | R/W         | DOUT_WORDS tlast missing    |

| 3                | 0                | R/W         | DIN_WORDS tlast unexpected  |

| 2                | 0                | R/W         | DIN_WORDS tlast missing     |

| 1                | 0                | R/W         | DIN tlast unexpected        |

| 0                | 0                | R/W         | DIN tlast missing           |

#### Notes:

- 1. Write 1 to respective bit to clear.

- 2. This register reflects the raw interrupt status and is not masked by the IMR.

### Interrupt Enable Register (IER) (0x20)

**Table 18: Interrupt Enable Register**

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                 |

|------------------|------------------|-------------|-----------------------------|

| 5                | 0                | WO          | DOUT_WORDS tlast unexpected |

| 4                | 0                | WO          | DOUT_WORDS tlast missing    |

| 3                | 0                | WO          | DIN_WORDS tlast unexpected  |

| 2                | 0                | WO          | DIN_WORDS tlast missing     |

| 1                | 0                | WO          | DIN tlast unexpected        |

| 0                | 0                | WO          | DIN tlast missing           |

#### Notes:

1. Read 0. Write 1 to respective bit to enable interrupt (respective bit of IMR is set to 0). Write 0 ignored.

<sup>1.</sup> This register should only be changed when the core is not active (ACTIVE is 0).

### Interrupt Disable Register (IDR) (0x24)

Table 19: Interrupt Disable Register

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                 |

|------------------|------------------|-------------|-----------------------------|

| 5                | 0                | WO          | DOUT_WORDS tlast unexpected |

| 4                | 0                | WO          | DOUT_WORDS tlast missing    |

| 3                | 0                | WO          | DIN_WORDS tlast unexpected  |

| 2                | 0                | WO          | DIN_WORDS tlast missing     |

| 1                | 0                | WO          | DIN tlast unexpected        |

| 0                | 0                | WO          | DIN tlast missing           |

#### Notes:

### Interrupt Mask Register (IMR) (0x28)

**Table 20: Interrupt Mask Register**

| Bit | Default<br>Value | Access Type | Description                 |

|-----|------------------|-------------|-----------------------------|

| 5   | 1                | RO          | DOUT_WORDS tlast unexpected |

| 4   | 1                | RO          | DOUT_WORDS tlast missing    |

| 3   | 1                | RO          | DIN_WORDS tlast unexpected  |

| 2   | 1                | RO          | DIN_WORDS tlast missing     |

| 1   | 1                | RO          | DIN tlast unexpected        |

| 0   | 1                | RO          | DIN tlast missing           |

#### Notes:

### ECC Interrupt Status Register (0x2C)

**Table 21: ECC Interrupt Status Register**

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description <sup>2</sup>                                                                                                        |

|------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 29               | 0                | R/W         | LDPC REF NM_NMQC Table ECC two-bit error (5G NR mode)/ LDPC CODE REG ECC two-bit error (Initialized non-5G mode) <sup>3,4</sup> |

| 28               | 0                | R/W         | LDPC REF QC Table ECC two-bit error <sup>3,4</sup>                                                                              |

| 27               | 0                | R/W         | LDPC REF LA Table ECC two-bit error <sup>3,4</sup>                                                                              |

| 26               | 0                | R/W         | LDPC REF SC Table ECC two-bit error <sup>3,4</sup>                                                                              |

| 25               | 0                | R/W         | LDPC REF NM_NMQC Table ECC event (5G NR mode)/ LDPC CODE REG ECC event (Initialized non-5G mode) <sup>3,5</sup>                 |

| 24               | 0                | R/W         | LDPC REF QC Table ECC event <sup>3</sup>                                                                                        |

<sup>1.</sup> Read 0. Write 1 to respective bit to disable interrupt (respective bit of IMR is set to 1). Write 0 ignored.

<sup>1.</sup> If mask bit is set, then interrupt is masked, that is, it does not cause the interrupt pin to go High.

Table 21: ECC Interrupt Status Register (cont'd)

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description <sup>2</sup>                                     |

|------------------|------------------|-------------|--------------------------------------------------------------|

| 23               | 0                | R/W         | LDPC REF LA Table ECC event <sup>3</sup>                     |

| 22               | 0                | R/W         | LDPC REF SC Table ECC event <sup>3</sup>                     |

| 21               | 0                | R/W         | LDPC final parity calc memory ECC two-bit error <sup>4</sup> |

| 20               | 0                | R/W         | LDPC QC_TABLE memory 3 ECC two-bit error <sup>4</sup>        |

| 19               | 0                | R/W         | LDPC QC_TABLE memory 2 ECC two-bit error <sup>4</sup>        |

| 18               | 0                | R/W         | LDPC QC_TABLE memory 1 ECC two-bit error <sup>4</sup>        |

| 17               | 0                | R/W         | LDPC QC_TABLE memory 0 ECC two-bit error <sup>4</sup>        |

| 16               | 0                | R/W         | LDPC LA_TABLE memory ECC two-bit error <sup>4</sup>          |

| 15               | 0                | R/W         | LDPC SC_TABLE memory ECC two-bit error <sup>4</sup>          |

| 14               | 0                | R/W         | LDPC code REG3 memory ECC two-bit error <sup>4</sup>         |

| 13               | 0                | R/W         | LDPC code REG2 memory ECC two-bit error <sup>4</sup>         |

| 12               | 0                | R/W         | LDPC code REG1 memory ECC two-bit error <sup>4</sup>         |

| 11               | 0                | R/W         | LDPC code REG0 memory ECC two-bit error <sup>4</sup>         |

| 10               | 0                | R/W         | LDPC final parity calc memory ECC event <sup>5</sup>         |

| 9                | 0                | R/W         | LDPC QC_TABLE memory 3 ECC event                             |

| 8                | 0                | R/W         | LDPC QC_TABLE memory 2 ECC event                             |

| 7                | 0                | R/W         | LDPC QC_TABLE memory 1 ECC event                             |

| 6                | 0                | R/W         | LDPC QC_TABLE memory 0 ECC event                             |

| 5                | 0                | R/W         | LDPC LA_TABLE memory ECC event                               |

| 4                | 0                | R/W         | LDPC SC_TABLE memory ECC event                               |

| 3                | 0                | R/W         | LDPC code REG3 memory ECC event                              |

| 2                | 0                | R/W         | LDPC code REG2 memory ECC event                              |

| 1                | 0                | R/W         | LDPC code REG1 memory ECC event                              |

| 0                | 0                | R/W         | LDPC code REG0 memory ECC event                              |

- 1. Write 1 to respective bit to clear.

- 2. This register reflects the raw interrupt status and is not masked by the IMR.

- 3. These memories exist in the SD-FEC support logic in 5G NR and initialized non-5G modes.

- 4. The ECC two-bit error register is set when two errors are detected in a word read from the respective memory. It can also be set when the number of errors in a word is greater than two—however, this is not guaranteed. Uncorrected multi-bit errors can result in incorrect core behavior.

- 5. An ECC event is when one or more errors have been detected in a word read from the respective memory. If present without an ECC two-bit error then only a single error has been detected, which has been corrected.

### ECC Interrupt Enable Register (0x30)

**Table 22: ECC Interrupt Enable Register**

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                                                                                                                     |

|------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 29               | 0                | WO          | LDPC REF NM_NMQC Table ECC two-bit error (5G NR mode)/ LDPC CODE REG ECC two-bit error (Initialized non-5G mode) <sup>2,3</sup> |

| 28               | 0                | WO          | LDPC REF QC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 27               | 0                | WO          | LDPC REF LA Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 26               | 0                | WO          | LDPC REF SC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 25               | 0                | WO          | LDPC REF NM_NMQC Table ECC event (5G NR mode)/ LDPC CODE REG ECC event (Initialized non-5G mode) <sup>2,3</sup>                 |

| 24               | 0                | WO          | LDPC REF QC Table ECC event <sup>2</sup>                                                                                        |

| 23               | 0                | WO          | LDPC REF LA Table ECC event <sup>2</sup>                                                                                        |

| 22               | 0                | WO          | LDPC REF SC Table ECC event <sup>2</sup>                                                                                        |

| 21               | 0                | WO          | LDPC final parity calc memory ECC two-bit error <sup>3</sup>                                                                    |

| 20               | 0                | WO          | LDPC QC_TABLE memory 3 ECC two-bit error <sup>3</sup>                                                                           |

| 19               | 0                | WO          | LDPC QC_TABLE memory 2 ECC two-bit error <sup>3</sup>                                                                           |

| 18               | 0                | WO          | LDPC QC_TABLE memory 1 ECC two-bit error <sup>3</sup>                                                                           |

| 17               | 0                | WO          | LDPC QC_TABLE memory 0 ECC two-bit error <sup>3</sup>                                                                           |

| 16               | 0                | WO          | LDPC LA_TABLE memory ECC two-bit error <sup>3</sup>                                                                             |

| 15               | 0                | WO          | LDPC SC_TABLE memory ECC two-bit error <sup>3</sup>                                                                             |

| 14               | 0                | WO          | LDPC code REG3 memory ECC two-bit error <sup>3</sup>                                                                            |

| 13               | 0                | WO          | LDPC code REG2 memory ECC two-bit error <sup>3</sup>                                                                            |

| 12               | 0                | WO          | LDPC code REG1 memory ECC two-bit error <sup>3</sup>                                                                            |

| 11               | 0                | WO          | LDPC code REG0 memory ECC two-bit error <sup>3</sup>                                                                            |

| 10               | 0                | WO          | LDPC final parity calc memory ECC event <sup>4</sup>                                                                            |

| 9                | 0                | WO          | LDPC QC_TABLE memory 3 ECC event                                                                                                |

| 8                | 0                | WO          | LDPC QC_TABLE memory 2 ECC event                                                                                                |

| 7                | 0                | WO          | LDPC QC_TABLE memory 1 ECC event                                                                                                |

| 6                | 0                | WO          | LDPC QC_TABLE memory 0 ECC event                                                                                                |

| 5                | 0                | WO          | LDPC LA_TABLE memory ECC event                                                                                                  |

| 4                | 0                | WO          | LDPC SC_TABLE memory ECC event                                                                                                  |

| 3                | 0                | WO          | LDPC code REG3 memory ECC event                                                                                                 |

| 2                | 0                | WO          | LDPC code REG2 memory ECC event                                                                                                 |

| 1                | 0                | WO          | LDPC code REG1 memory ECC event                                                                                                 |

Table 22: ECC Interrupt Enable Register (cont'd)

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                     |

|------------------|------------------|-------------|---------------------------------|

| 0                | 0                | WO          | LDPC code REG0 memory ECC event |

- Read 0. Write 1 to respective bit to enable interrupt (respective bit of ECC Interrupt Mask register is set to 0). Write 0

ignored.

- 2. These memories exist in the SD-FEC support logic in 5G NR and initialized non-5G modes.

- 3. The ECC two-bit error register is set when two errors are detected in a word read from the respective memory. It can also be set when the number of errors in a word is greater than two—however, this is not guaranteed. Uncorrected multi-bit errors can result in incorrect core behavior. A core reset is recommended, followed by re-programming of the LDPC code parameters.

- 4. An ECC event is when one or more errors have been detected in a word read from the respective memory. If present without an ECC two-bit error then only a single error has been detected, which has been corrected. To avoid this potentially becoming an uncorrectable two-bit error at a later time the memory contents should be refreshed.

### ECC Interrupt Disable Register (0x34)

Table 23: ECC Interrupt Disable Register

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                                                                                                                     |

|------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 29               | 0                | WO          | LDPC REF NM_NMQC Table ECC two-bit error (5G NR mode)/ LDPC CODE REG ECC two-bit error (Initialized non-5G mode) <sup>2,3</sup> |

| 28               | 0                | WO          | LDPC REF QC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 27               | 0                | WO          | LDPC REF LA Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 26               | 0                | WO          | LDPC REF SC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 25               | 0                | WO          | LDPC REF NM_NMQC Table ECC event (5G NR mode)/ LDPC CODE REG ECC event (Initialized non-5G mode) <sup>2,4</sup>                 |

| 24               | 0                | WO          | LDPC REF QC Table ECC event <sup>2</sup>                                                                                        |

| 23               | 0                | WO          | LDPC REF LA Table ECC event <sup>2</sup>                                                                                        |

| 22               | 0                | WO          | LDPC REF SC Table ECC event <sup>2</sup>                                                                                        |

| 21               | 0                | WO          | LDPC final parity calc memory ECC two-bit error <sup>3</sup>                                                                    |

| 20               | 0                | WO          | LDPC QC_TABLE memory 3 ECC two-bit error <sup>3</sup>                                                                           |

| 19               | 0                | WO          | LDPC QC_TABLE memory 2 ECC two-bit error <sup>3</sup>                                                                           |

| 18               | 0                | WO          | LDPC QC_TABLE memory 1 ECC two-bit error <sup>3</sup>                                                                           |

| 17               | 0                | WO          | LDPC QC_TABLE memory 0 ECC two-bit error <sup>3</sup>                                                                           |

| 16               | 0                | WO          | LDPC LA_TABLE memory ECC two-bit error <sup>3</sup>                                                                             |

| 15               | 0                | WO          | LDPC SC_TABLE memory ECC two-bit error <sup>3</sup>                                                                             |

| 14               | 0                | WO          | LDPC code REG3 memory ECC two-bit error <sup>3</sup>                                                                            |

| 13               | 0                | WO          | LDPC code REG2 memory ECC two-bit error <sup>3</sup>                                                                            |

| 12               | 0                | WO          | LDPC code REG1 memory ECC two-bit error <sup>3</sup>                                                                            |

| 11               | 0                | WO          | LDPC code REG0 memory ECC two-bit error <sup>3</sup>                                                                            |

| 10               | 0                | WO          | LDPC final parity calc memory ECC event <sup>4</sup>                                                                            |

| 9                | 0                | WO          | LDPC QC_TABLE memory 3 ECC event                                                                                                |

Table 23: ECC Interrupt Disable Register (cont'd)

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                      |

|------------------|------------------|-------------|----------------------------------|

| 8                | 0                | WO          | LDPC QC_TABLE memory 2 ECC event |

| 7                | 0                | WO          | LDPC QC_TABLE memory 1 ECC event |

| 6                | 0                | WO          | LDPC QC_TABLE memory 0 ECC event |

| 5                | 0                | WO          | LDPC LA_TABLE memory ECC event   |

| 4                | 0                | WO          | LDPC SC_TABLE memory ECC event   |

| 3                | 0                | WO          | LDPC code REG3 memory ECC event  |

| 2                | 0                | WO          | LDPC code REG2 memory ECC event  |

| 1                | 0                | WO          | LDPC code REG1 memory ECC event  |

| 0                | 0                | WO          | LDPC code REG0 memory ECC event  |

- 1. Read 0. Write 1 to respective bit to disable interrupt (respective bit of ECC Interrupt Mask register is set to 1). Write 0 ignored.

- 2. These memories exist in the SD-FEC support logic in 5G NR and initialized non-5G modes.

- 3. The ECC two-bit error register is set when two errors are detected in a word read from the respective memory. It can also be set when the number of errors in a word is greater than two—however, this is not guaranteed. Uncorrected multi-bit errors can result in incorrect core behavior. A core reset is recommended, followed by re-programming of the LDPC code parameters.

- 4. An ECC event is when one or more errors have been detected in a word read from the respective memory. If present without an ECC two-bit error then only a single error has been detected, which has been corrected. To avoid this potentially becoming an uncorrectable two-bit error at a later time the memory contents should be refreshed.

### ECC Interrupt Mask Register (0x38)

Table 24: ECC Interrupt Mask Register

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                                                                                                                     |

|------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 29               | 0                | RO          | LDPC REF NM_NMQC Table ECC two-bit error (5G NR mode)/ LDPC CODE REG ECC two-bit error (Initialized non-5G mode) <sup>2,3</sup> |

| 28               | 0                | RO          | LDPC REF QC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 27               | 0                | RO          | LDPC REF LA Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 26               | 0                | RO          | LDPC REF SC Table ECC two-bit error <sup>2,3</sup>                                                                              |

| 25               | 0                | RO          | LDPC REF NM_NMQC Table ECC event (5G NR mode)/ LDPC CODE REG ECC event (Initialized non-5G mode) <sup>2,4</sup>                 |

| 24               | 0                | RO          | LDPC REF QC Table ECC event <sup>2</sup>                                                                                        |

| 23               | 0                | RO          | LDPC REF LA Table ECC event <sup>2</sup>                                                                                        |

| 22               | 0                | RO          | LDPC REF SC Table ECC event <sup>2</sup>                                                                                        |

| 21               | 1                | RO          | LDPC final parity calc memory ECC two-bit error <sup>3</sup>                                                                    |

| 20               | 1                | RO          | LDPC QC_TABLE memory 3 ECC two-bit error <sup>3</sup>                                                                           |

| 19               | 1                | RO          | LDPC QC_TABLE memory 2 ECC two-bit error <sup>3</sup>                                                                           |

| 18               | 1                | RO          | LDPC QC_TABLE memory 1 ECC two-bit error <sup>3</sup>                                                                           |

| 17               | 1                | RO          | LDPC QC_TABLE memory 0 ECC two-bit error <sup>3</sup>                                                                           |

Table 24: ECC Interrupt Mask Register (cont'd)

| Bit <sup>1</sup> | Default<br>Value | Access Type | Description                                          |

|------------------|------------------|-------------|------------------------------------------------------|

| 16               | 1                | RO          | LDPC LA_TABLE memory ECC two-bit error <sup>3</sup>  |

| 15               | 1                | RO          | LDPC SC_TABLE memory ECC two-bit error <sup>3</sup>  |

| 14               | 1                | RO          | LDPC code REG3 memory ECC two-bit error <sup>3</sup> |

| 13               | 1                | RO          | LDPC code REG2 memory ECC two-bit error <sup>3</sup> |

| 12               | 1                | RO          | LDPC code REG1 memory ECC two-bit error <sup>3</sup> |

| 11               | 1                | RO          | LDPC code REG0 memory ECC two-bit error <sup>3</sup> |

| 10               | 1                | RO          | LDPC final parity calc memory ECC event <sup>4</sup> |

| 9                | 1                | RO          | LDPC QC_TABLE memory 3 ECC event                     |

| 8                | 1                | RO          | LDPC QC_TABLE memory 2 ECC event                     |

| 7                | 1                | RO          | LDPC QC_TABLE memory 1 ECC event                     |

| 6                | 1                | RO          | LDPC QC_TABLE memory 0 ECC event                     |

| 5                | 1                | RO          | LDPC LA_TABLE memory ECC event                       |

| 4                | 1                | RO          | LDPC SC_TABLE memory ECC event                       |

| 3                | 1                | RO          | LDPC code REG3 memory ECC event                      |

| 2                | 1                | RO          | LDPC code REG2 memory ECC event                      |

| 1                | 1                | RO          | LDPC code REG1 memory ECC event                      |

| 0                | 1                | RO          | LDPC code REG0 memory ECC event                      |

- 1. If mask bit is set, then interrupt is masked, that is, it does not cause the interrupt pin to go High.

- 2. These memories exist in the SD-FEC support logic in 5G NR and initialized non-5G modes.

- 3. The ECC two-bit error register is set when two errors are detected in a word read from the respective memory. It can also be set when the number of errors in a word is greater than two—however, this is not guaranteed. Uncorrected multi-bit errors can result in incorrect core behavior. A core reset is recommended, followed by re-programming of the LDPC code parameters.

- 4. An ECC event is when one or more errors have been detected in a word read from the respective memory. If present without an ECC two-bit error then only a single error has been detected, which has been corrected. To avoid this potentially becoming an uncorrectable two-bit error at a later time the memory contents should be refreshed.

### BYPASS Register (0x3C)

**Table 25: BYPASS Register**

| Bit | Default<br>Value | Access Type | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0                | R/W         | Perform function with given number of iterations (early termination not supported, so associated termination bits must be set to zero in CTRL input while BYPASS is set), but output is same as input (minus tail bits for turbo decode) accounting for any soft to hard conversion.  Parity pass/CRC flag is based on input values:  0: Normal operation 1: Output same as input |

#### Notes:

1. This register should only be changed when the core is not active (ACTIVE is 0).

### **Turbo Code Parameters Register (0x100)**

If the core is out of reset, turbo code parameters can be read at any time. Turbo code parameters should only be updated when the core is not active (ACTIVE is 0).

Table 26: Turbo Code Register

| Bit  | Default<br>Value | Access Type | Description                                               |

|------|------------------|-------------|-----------------------------------------------------------|

| 11:8 | 0xC              | R/W         | SCALE_FACTOR 0: Scale=1 1-15: Scale = 0.0625*SCALE_FACTOR |

| 0    | 0                | R/W         | ALG: Turbo Decode Algorithm 0: Max_scale 1: Max star      |

### **LDPC Code Parameters**

**IMPORTANT!** Do not update the LDPC code parameters in 5G mode.

The LDPC code parameters can be written at any time; however registers should not be written that are associated with a code which is being processed by the engine (otherwise the behavior is unpredictable, and lockup might result, requiring a reset). The LDPC code parameters can only be read while the core is not active (ACTIVE=0); otherwise 0 is returned. Settings for the LDPC code parameters and shared tables are provided in the Vivado® IDE core configuration for a particular code definition. These registers must be provided for each code where the code register is derived using CODE, which takes a value 0 to 127. The code definition to be used is supplied for a block through the CTRL interface.

### REGO Register (0x2000+CODE\*0x10)

Table 27: REGO Register

| Bit   | Access Type | Description                                                                                           |

|-------|-------------|-------------------------------------------------------------------------------------------------------|

| 30:16 | R/W         | K: Number of information bits. $2 \le K \le 32766$ , multiples of P. Also $K \le 256 \times P$ .      |

| 15:0  | R/W         | N: Number of codeword bits.<br>$4 \le N \le 32768$ multiples of P. Also $N \le 256 \times P$ and N>K. |

#### Notes

- 1. See Non-5G Control Interface Definition for LDPC Decode and Encode for CODE definition.

- 2. Setting invalid parameter values results in an interrupt and otherwise undefined behavior, requiring a reset to recover.

- 3. The default value is undefined.

#### **Related Information**

Non-5G NR Control Interface Definition for LDPC Decode Non-5G NR Control Interface Definition for LDPC Encode

### REG1 Register (0x2004+CODE\*0x10)

Table 28: REG1 Register

| Bit   | Access Type | Description                                                                                                                                                                                                                       |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19:11 | R/W         | NM: Specifies internal soft-data memory requirements of codeword. Parameter set by the Vivado® IDE for the given code definition.                                                                                                 |

| 10    | R/W         | NO_PACKING: Determines whether multiple QC operations should be performed in the same clock cycle.  0: Pack multiple QC operations when P allows.  1: Do not pack multiple QC operations. If Packing is not enabled in the Vivado |

|       |             | IDE, then NO_PACKING is internally overridden to be 1.                                                                                                                                                                            |

| 9:0   | R/W         | P: Size of sub-matrix<br>Range: 2 ≤ P ≤ 512                                                                                                                                                                                       |

#### Notes:

- 1. See Non-5G Control Interface Definition for LDPC Decode and Encode for CODE definition.

- 2. Setting invalid parameter values results in incorrect operation, requiring a reset to recover.

- 3. The default value is undefined.

### **Related Information**

Non-5G NR Control Interface Definition for LDPC Decode Non-5G NR Control Interface Definition for LDPC Encode

### REG2 Register (0x2008+CODE\*0x10)

Table 29: REG2 Register

| Bit   | Access Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |