# Xilinx T1 Telco Accelerator Card

## 5G Virtual BBU, O-DU, and O-CU Acceleration

#### **OVERVIEW**

Xilinx T1 Telco Accelerator card provides high performance, low latency, and power efficiency needed for 5G O-DU deployments. The turnkey solution enables operators, system integrators, and OEMs to get to market quickly and to simplify the deployment of services at the edge.

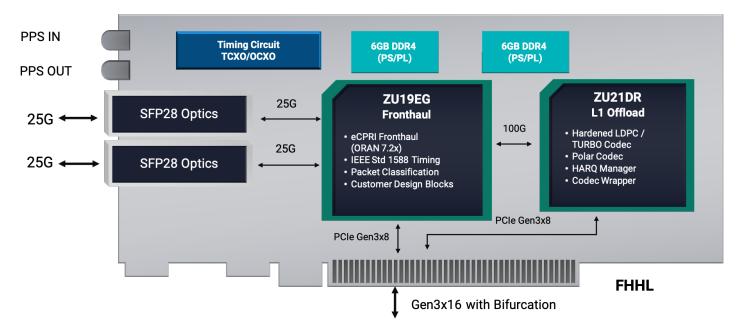

T1 card uses 16nm Zynq® UltraScale+™ MPSoC and Zynq UltraScale+ RFSoC devices to accelerate fronthaul and real-time baseband (L1) lookaside processing.

- > ZU19EG MPSoC provides the 3GPP O-RAN 7.2 split fronthaul traffic termination for 5G eCPRI/RoE/SyncE protocols. The Zynq UltraScale+ MPSoC also implements IEEE Std 1588 timing functionality with onboard reference clock timing circuit.

- > ZU21DR RFSoC includes 4G/5G encode and decode acceleration along with wrapper functions such as rate matching and CRC logic. Zynq UltraScale+ RFSoC has hardened soft-decision forward error correction (SD-FEC), which can perform high-performance encode and decode with low latency and low power.

The T1 card's PCle® Gen3 x16 connecter is bifurcated into dual PCle Gen3 x8 interfaces, giving each device independent access to the host. The board is a single slot full height, half length (FHHL) form factor with two SFP28 optical interface connectors.

#### TARGET APPLICATIONS

- > 5G ORAN-7.2 Fronthaul termination

- > 5G L1 baseband acceleration

- > 5G Fronthaul with Low-PHY (optional) functions

#### **PERFORMANCE**

Virtualization requires significant acceleration of latency-sensitive and compute-intensive functions. The T1 card performance metrics below are based on in-lab measurements of the card reference design. Watch the launch video at: <a href="https://www.xilinx.com/T1">www.xilinx.com/T1</a>.

## L1 (Baseband) Acceleration Performance

|             | Performance | Latency |

|-------------|-------------|---------|

| LDPC Encode | 17.8Gb/s    | 14µs    |

| LDPC Decode | 8.1Gb/s     | 16µs    |

#### Fronthaul Performance

| Fronthaul Configuration(1)                 | Performance                                                                                                  | Notes                                        |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ACTIVE-STANDBY with O-RAN Processing on T1 | <ul> <li>25Gb/s Active (2 sectors of 4T4R 100MHz)</li> <li>25Gb/s Standby (If Active link fails)</li> </ul>  | For high-reliability deployments             |

| ACTIVE with O-RAN Processing on T1         | <ul> <li>25Gb/s Active (1 sector of 4T4R 100MHz)</li> <li>25Gb/s Active (1 sector of 4T4R 100MHz)</li> </ul> | For deployments utilizing fronthaul gateways |

| ACTIVE<br>With O-RAN in software           | > 50Gb/s (4 sectors of 4T4R 100MHz<br>with 4 layers each)                                                    | For high-density deployments                 |

(1) Other configurations for fronthaul are possible

| SoCs                           | Xilinx   Zynq UltraScale Plus RFSoC   XCZU21DR  Xilinx   Zynq UltraScale+ MPSoC   XCZU19EG                                                                                                                                                            |                                                                                                                                                                                           |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3005                           |                                                                                                                                                                                                                                                       |                                                                                                                                                                                           |  |

| SoC Resources                  | XCZU21DR                                                                                                                                                                                                                                              | XCZU19EG                                                                                                                                                                                  |  |

|                                | <ul> <li>System Logic cells - 930K</li> <li>CLB LUT - 425K</li> <li>SDFEC -8</li> <li>DSP Slices - 4,272</li> <li>BRAM - 38.0Mb</li> <li>URAM - 22.5Mb</li> </ul>                                                                                     | <ul> <li>System Logic cells - 1,143K</li> <li>CLB LUT - 523K</li> <li>CLB Flip-Flops -1,045K</li> <li>DSP Slices - 1,968</li> <li>BRAM - 34.6Mb</li> <li>URAM - 36.0Mb</li> </ul>         |  |

| Form Factor                    | <ul> <li>Full-height, half-length (FHHL)</li> <li>x16 PCle form factor</li> <li>Width: 167.65mm</li> <li>Height: 111.15mm</li> <li>Depth: 34.8mm</li> </ul>                                                                                           |                                                                                                                                                                                           |  |

| PCIe Interface                 | PCIe Gen3 x16 interface bifurcated to two PCIe Gen3 x8                                                                                                                                                                                                |                                                                                                                                                                                           |  |

| Onboard Memory                 | XCZU21DR                                                                                                                                                                                                                                              | XCZU19EG                                                                                                                                                                                  |  |

|                                | <ul> <li>1x Banks of 4GB x72 (64 bit +8bit ECC) - PL</li> <li>1x Banks of 2GB x 40 (32 bit +8bit ECC) - PS</li> <li>Total Capacity 4GB in PL</li> <li>Total Capacity 2GB in PS</li> </ul>                                                             | <ul> <li>1x Banks of 4GB x72 (64 bit +8bit ECC) - PL</li> <li>1x Banks of 2GB x 40 (32 bit +8bit ECC) - PS</li> <li>Total Capacity 4GB in PL</li> <li>Total Capacity 2GB in PS</li> </ul> |  |

| In System Upgrade              | Standard Xilinx tandem and partial reconfiguration support for both devices                                                                                                                                                                           |                                                                                                                                                                                           |  |

| Programming                    | <ul> <li>1x 2Gb QSPI NOR Flash for FPGA configuration for ZU19EG</li> <li>1x 2Gb QSPI NOR Flash for FPGA configuration for ZU21DR</li> </ul>                                                                                                          |                                                                                                                                                                                           |  |

| Network Interface(s)           | > 2xSFP28 optical interfaces to XCZU19EG (User Configurable, includes 10/25 Ethernet)                                                                                                                                                                 |                                                                                                                                                                                           |  |

| Other External<br>Interface(s) | Micro USB for JTAG support (FPGA programming and debug) and access to BMC                                                                                                                                                                             |                                                                                                                                                                                           |  |

| Reference Design               | Vivado® design (diagnostic bit file) and commands for testing all datapath interfaces available for diagnostic bit files for both FPGAs                                                                                                               |                                                                                                                                                                                           |  |

| Cooling                        | Passive cooling, custom heat sink                                                                                                                                                                                                                     |                                                                                                                                                                                           |  |

| Board Management<br>Controller | <ul> <li>Power sequencing and reset</li> <li>Field upgrades</li> <li>FPGA configuration and control</li> <li>Clock configuration</li> <li>Temperature monitoring</li> <li>USB 2.0</li> </ul>                                                          |                                                                                                                                                                                           |  |

| Operating Temperature          | 0-100°C (up to 110°C for NEBS excursion)                                                                                                                                                                                                              |                                                                                                                                                                                           |  |

| Power                          | < 75W typical                                                                                                                                                                                                                                         |                                                                                                                                                                                           |  |

| Clocking Options               | <ul> <li>Low-Jitter, configurable clock ranging from10MHz to 750 MHz</li> <li>Capable of ITU-T G8273.2</li> <li>1 PPS input and output mode support</li> <li>Have assembly option for OCXO and/or TCXO for Master and slave mode operation</li> </ul> |                                                                                                                                                                                           |  |

## 1. Timing Circuitry

- > TCXO/OCXO with PPS in and out.

- > PS (A53) for 1588 protocol stack

## 2. Fronthaul Termination

- > 2x25G eCPRI w/TSN + RS-FEC & 1588

- > Aggregation Logic

- > Buffer memory

- > Packet Classification

#### 3. L1 Offload

- > LDPC/TURBO codecs

- > Polar codecs

- > HARQ management

- > Codec Surrounding/Wrapper logic

- CRC logic

- Rate Matching/De-Matching

Figure 1: Xilinx T1 Block Diagram

Corporate Headquarters

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA Tel: 408-559-7778 www.xilinx.com Xilinx Europe

Xilinx Europe

Bianconi Avenue

Citywest Business Campus

Saggart, County Dublin

Ireland

Tel: +353-1-464-0311

Japan Xilinx K.K.

Allilix N.N. Art Village Osaki Central Tower 4F 1-2-2 Osaki, Shinagawa-ku Tokyo 141-0032 Japan Tel: +81-3-6744-7777 japan.xilinx.com Asia Pacific Pte. Ltd.

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com India

Xilinx India Technology Services Pvt. Ltd. Block A, B, C, 8th & 13th floors, Meenakshi Tech Park, Survey No. 39 Gachibowli(V), Seri Lingampally (M), Hyderabad -500 084 Tel: +91-40-6721-4747 www.xilinx.com