## Future of Adaptive Computing: The Composable Data Center

Salil Raje, EVP & GM, Data Center Group March 2021

#### **Data Center Trends**

- Explosion of unstructured data

- Diversity of workloads

- Latency-sensitive applications

- Evolving standards

#### TIME

#### **Key Challenges for Data Centers**

Meet performance and latency requirements

Quickly adapt to changing workloads

Minimize TCO and power

Evolve to more efficient architectures

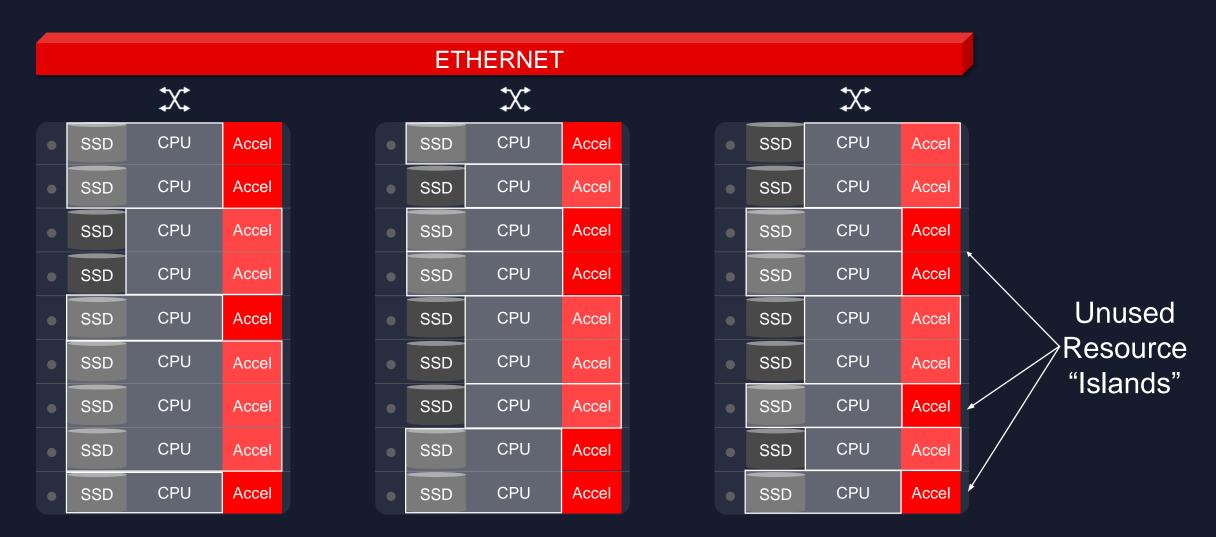

#### **Limitations of Current Data Center Architecture:**

Fixed Configuration + Sub-optimal Utilization

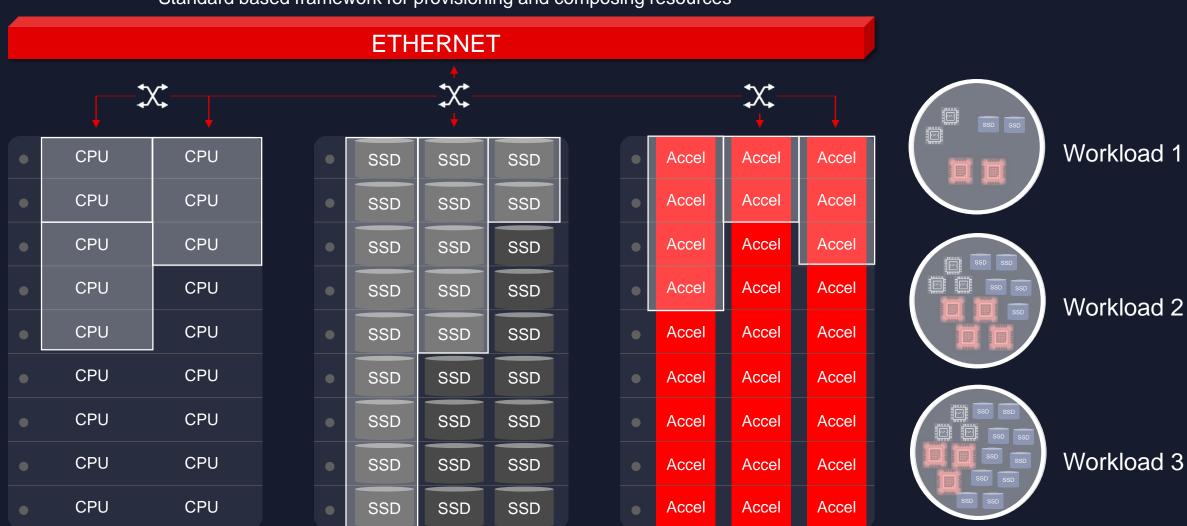

#### The Solution: Composable Data Center

Decoupling of resources

Pooling them + accessible from anywhere

Provisioning workloads with exact resources needed

Reconfigurable via software

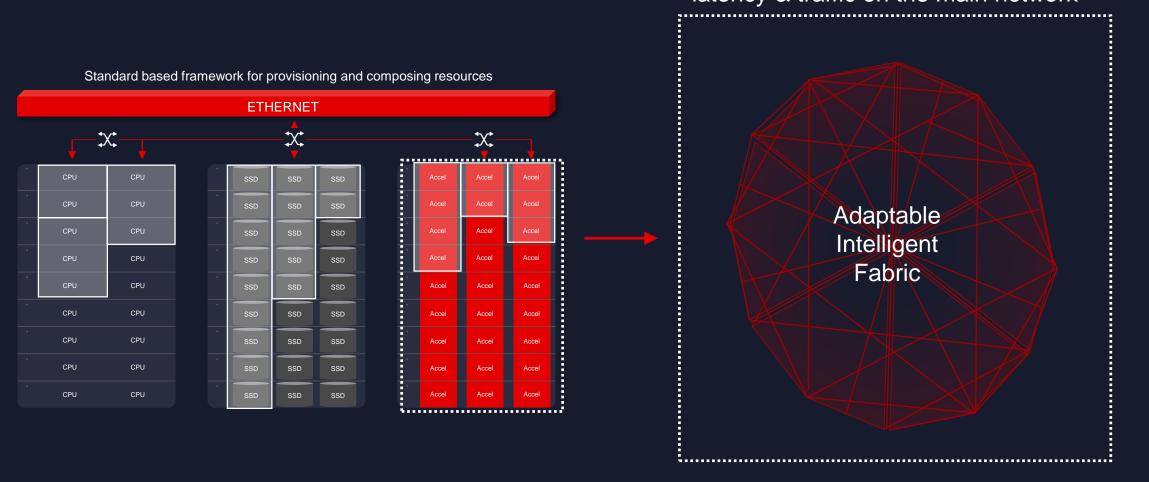

#### Composable Data Center Utilizes Resources Efficiently

Standard based framework for provisioning and composing resources

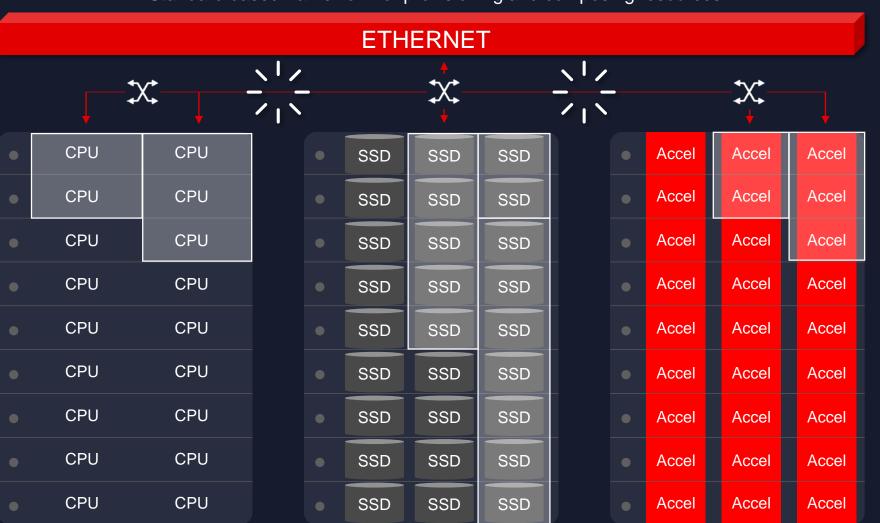

#### Main Challenge of Composable Data Center: Latency

Standard based framework for provisioning and composing resources

Increased

Latency

&

Reduced

Bandwidth

7

#### FPGAs Enabling the Composable Data Center

01.

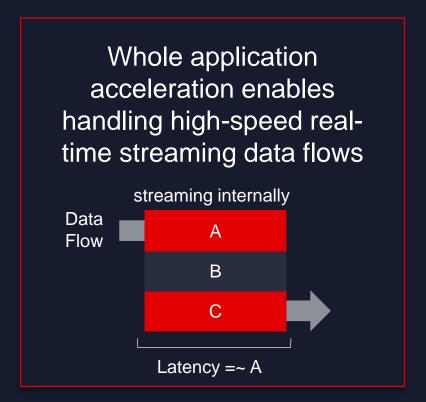

Adaptable & scalable acceleration improves workload performance

02.

Bringing compute closer to data to reduces latency & bandwidth

03.

Adaptable Intelligent fabric enables efficient pooling of resources

#### Adaptable & Scalable Acceleration Improves Performance

#### FPGA advantages in data center

Customizable architecture adapts to specific applications to maximize workload performance

Encryption

Analytics

Same architecture can be scaled and algorithms ported to fit different place in the data center

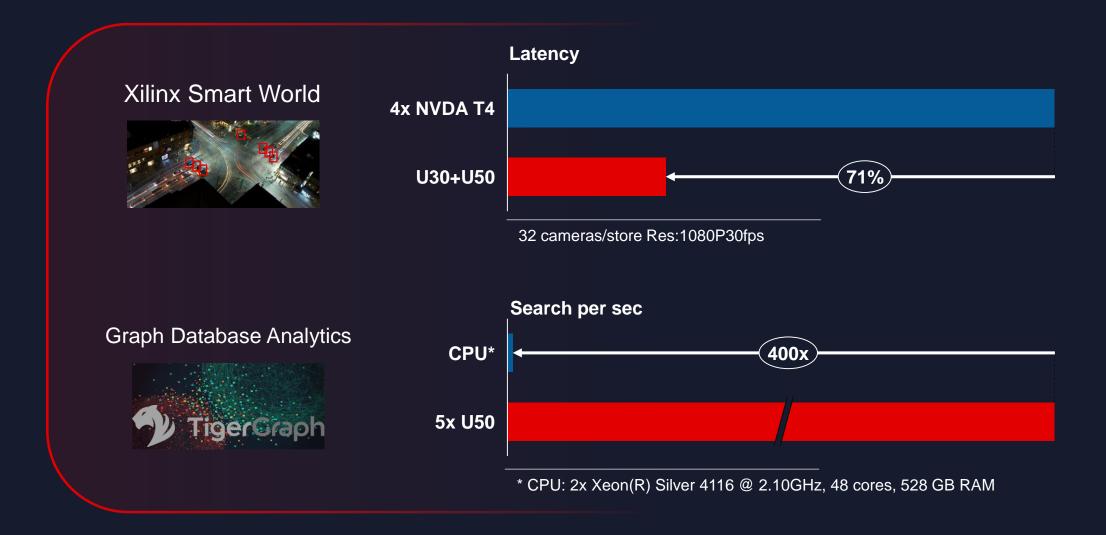

#### FPGAs Enabling Workload Acceleration

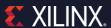

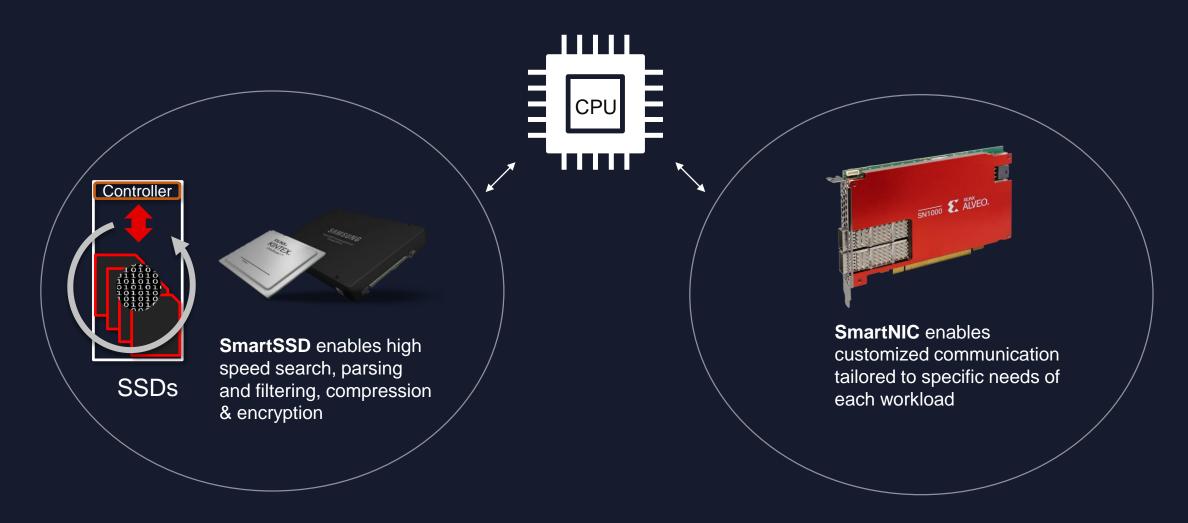

#### Bringing Compute Closer to Data at Rest & In Motion

Reduces Bandwidth Need & Improves Latency

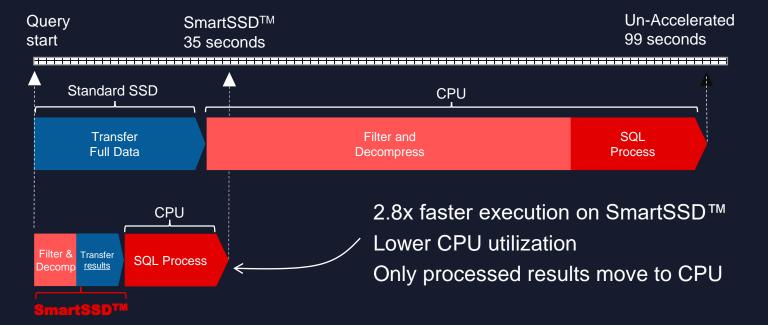

#### **Moving Compute Closer to Storage**

- High speed NPU search

- Parsing and filtering

- Compression/Decompression

- Encryption/Decryption

SmartSSDs

#### **SmartSSD Computational Storage Device**

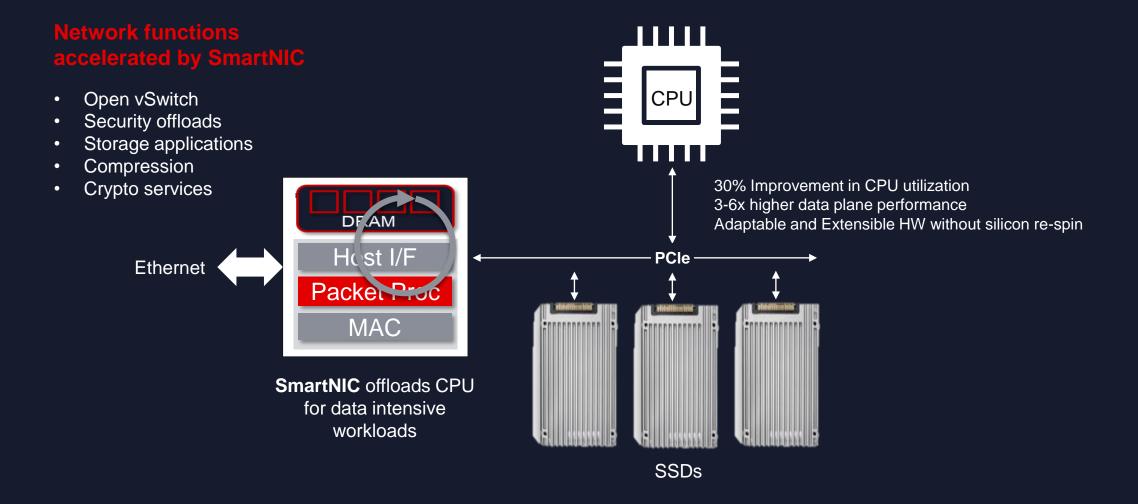

#### **FPGAs as SmartNIC Network Accelerators**

#### **Alveo SN1000 SmartNIC**

Software-defined hardware acceleration for all offloads

Application specific data paths at line-rate performance

P4, C, C++ programming for fast, adaptable hardware acceleration

Heterogeneous architecture with control and data plane isolation

#### Next Gen FPGAs Enable Adaptable Intelligent Fabric

Local communication among accelerators reduces latency & traffic on the main network

### Integrated VITIS + Hoperan Adaptable Elements

Domain specific Frameworks Resource provisioning and Frameworks composition Frameworks (A) **WFFMPEG** Libraries C/C++ | Python | RTL | P4 Vitis + P4 Compilers Analyzers Debuggers ARM, HLS, Al Engines, P4 Vitis Runtime (XRT) Vitis target platform **SmartSSD SmartNIC** Compute Acceleration

# XILINX Paving the Way to the Composable Data Center of the Future

Rapid Reconfigurability | Reduced Latency | Flexible Architecture