## Xilinx Answer 43879 MIG 7 Series DDR3/DDR2 - Hardware Debug Guide

**Important Note:** This downloadable PDF of an Answer Record is provided to enhance its usability and readability. It is important to note that Answer Records are Web-based content that are frequently updated as new information becomes available. You are reminded to visit the Xilinx Technical Support Website and review (Xilinx Answer 43879) for the latest version of this Answer Record.

## Introduction

Calibration failures and data errors can occur for many reasons and the debug of these errors can be time consuming. This answer record is intended to provide a clear step-by-step debug process to quickly identify the root cause of the failure and move to resolution.

## **MIG Usage**

To focus the debug of calibration or data errors, use the provided MIG Example Design on the targeted board with the Debug Feature enabled through the MIG 7 Series GUI. The latest MIG 7 Series release should be used to generate the Example Design.

## **Debug Tools**

Many tools are available to debug memory interface design issues. This section indicates which resources are useful for debugging a given situation.

## **Example Design**

Generation of a DDR2 or DDR3 design through the MIG 7 series tool produces an example design and a user design. The example design includes a synthesizable testbench with a traffic generator that is fully verified in simulation and hardware. This example design can be used to observe the behavior of the MIG 7 series design and can also aid in identifying board-related problems. For complete details on the example design, see the "Quick Start Example Design" in the 7 Series FPGAs Memory Interface Solutions User Guide (UG586). This debug guide answer record further describes using the example design to perform hardware validation.

#### **Debug Signals**

The MIG 7 series tool includes a Debug Signals Control option on the FPGA Options screen. Enabling this feature allows calibration, tap delay, and read data signals to be monitored using the ChipScope<sup>™</sup> analyzer. Selecting this option port maps the debug signals to ILA and VIO cores of the ChipScope analyzer in the design top module. For details on enabling this debug feature, see the "Getting Started with the CORE Generator<sup>™</sup> Tool" section in the *7 Series FPGAs Memory Interface Solutions User Guide* (UG586). The debug port is disabled for functional simulation and can only be enabled if the signals are actively driven by the user design.

#### **Reference Boards**

The KC705 and VC707 evaluation kits are Xilinx development boards that include FPGA interfaces to a DDR3 SODIMM. These boards can be used to test user designs and analyze board layout.

# 🐮 XILINX.

## ChipScope Pro Tool

The ChipScope<sup>™</sup> Pro tool inserts logic analyzer, bus analyzer, and VIO software cores directly into the design. The ChipScope Pro tool allows the user to set trigger conditions to capture application and MIG signals in hardware. Captured signals can then be analyzed through the ChipScope Pro logic analyzer tool.

# **General Checks**

This section details the list of general checks, primarily board level, which need to be verified before moving forward with the debug process. Strict adherence to the proper board design is critical in working with high speed memory interfaces.

- Ensure all guidelines referenced in the "Design Guidelines" sections of the 7 Series FPGAs Memory Interface Solutions User Guide (UG586) have been followed. The Design Guidelines section includes information on trace matching, PCB Routing, noise, termination, I/O Standards, and pin/bank requirements. Adherence to these guidelines, along with proper board design and signal integrity analysis, is critical to the success of high-speed memory interfaces.

- Measure all voltages on the board during idle and non-idle times to ensure the voltages are set appropriately and noise is within specifications.

- Ensure the termination voltage regulator (Vtt) is turned on (set to 0.75V).

- Ensure Vref is measured.

- When applicable, check VRN/VRP resistors. Note the values are not the same as Virtex-6 FPGA.

- Look at the clock inputs to ensure they are clean.

- Check the reset to ensure the polarity is correct and the signal is clean.

- Check terminations. The 7 Series FPGAs Memory Interface Solutions User Guide (UG586) should be used as a guideline.

- Perform general signal integrity analysis.

- IBIS simulations should be run to ensure terminations, ODT, and output drive strength settings are appropriate.

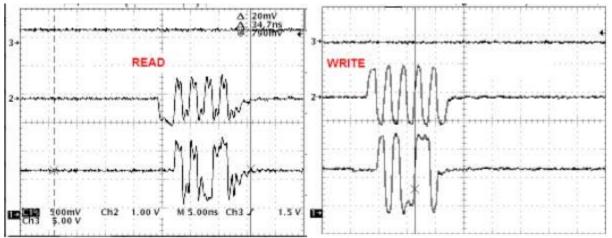

- Observe DQ/DQS on a scope at the memory. View the alignment of the signals and analyze the signal integrity during both writes and reads.

- Observe the Address and Command signals on a scope at the memory. View the alignment and analyze the signal integrity.

- Verify the memory parts on the board(s) in test are the correct part(s) set through MIG. The timing parameters and signals widths (i.e., address, bank address) must match between the RTL and physical parts. Read/write failures can occur due to a mismatch.

- Verify SDRAM pins are behaving correctly. Look for floating or grounded signals. It is rare, but manufacturing issues with the memory devices can occur and result in calibration failures.

- If Data Mask (DM) is not being used, ensure DM is tied Low at the memory with the appropriate termination as noted in the memory datasheet.

- Measure the CK/CK\_n, DQS/DQS\_n, and system clocks for duty cycle distortion and general signal integrity.

- If internal Vref is used, ensure the constraints are set appropriately according to the Xilinx Constraints Guide. When the constraints are applied properly, a note similar to the following will be in the .bgn Bit

- Gen report file:

- o There were two CONFIG constraint(s) processed from example\_top.pcf.

- CONFIG INTERNAL\_VREF\_BANK12 = "0.75" CONFIG INTERNAL\_VREF\_BANK14 = "0.75"

- Check the iodelay\_ctrl ready signal.

- Check the PLL lock.

- Check the phaser\_ref lock signal.

- Bring the init\_calib\_complete out to a pin and check with a scope.

# **Calibration Stages**

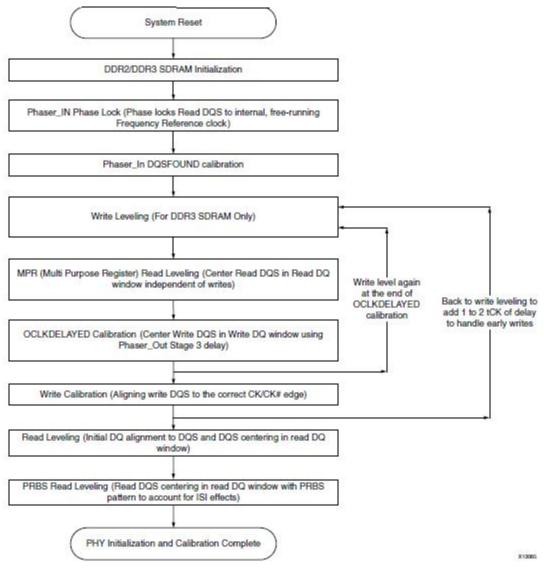

Figure 1 - Calibration Stages

## **Memory Initialization**

The PHY executes a JEDEC-compliant DDR2 or DDR3 initialization sequence following the de-assertion of system reset. Each DDR2 or DDR3 SDRAM has a series of mode registers accessed via mode register set (MRS) commands. These mode registers determine various SDRAM behaviors, such as burst length, read and write CAS latency, and additive latency. The MIG 7 series designs will never issue a calibration failure during Memory Initialization.

All other initialization/calibration stages are reviewed in the appropriate Debugging Calibration Stages section below.

# **Determine the Failing Calibration Stage**

Using ChipScope analyzer, configure the device and open the provided "example\_top.cpj" file. This file is generated in the "example\_design/par" directory when the Debug Signals feature is enabled during core generation. Observe the following debug signals in the provided "Basic" ILA core. This will indicate which calibration stage failed:

#### Table 1: DDR3/DDR2 "Basic ILA" Debug Signals

| Signal Name               | ILA/VIO<br>Connection | Signal Description                                                                      |

|---------------------------|-----------------------|-----------------------------------------------------------------------------------------|

| init_calib_complete       | ila_basic[0]          | Signifies memory initialization and calibration have completed successfully             |

| dbg_wrlvl_start           | ila_basic[1]          | Signifies the start of the Write Leveling stage of calibration                          |

| dbg_wrlvl_done            | ila_basic[2]          | Signifies successful completion of the Write Leveling stage of calibration              |

| dbg_wrlvl_err             | ila_basic[3]          | Signifies the Write Leveling stage of calibration exhibited errors and did not complete |

| dbg_pi_phaselock_start    | ila_basic[4]          | Signifies the start of the PHASELOCK stage of calibration                               |

| dbg_pi_phaselock_done     | ila_basic[5]          | Signifies successful completion of the PHASELOCK stage of calibration                   |

| dbg_pi_phaselock_err      | ila_basic[6]          | Signifies the PHASELOCK stage of calibration exhibited errors and did not complete      |

| dbg_pi_dqsfound_start     | ila_basic[7]          | Signifies the start of the DQSFOUND stage of calibration                                |

| dbg_pi_dqsfound_done      | ila_basic[8]          | Signifies successful completion of the DQSFOUND stage of calibration                    |

| dbg_pi_dqsfound_err       | ila_basic[9]          | Signifies the DQSFOUND stage of calibration exhibited errors and did not complete       |

| dbg_rdlvl_start[0]        | ila_basic[10]         | Signifies the start of Read Leveling Stage 1 calibration                                |

| dbg_rdlvl_start[1]        | ila_basic[11]         | Signifies the start of the MPR stage of calibration                                     |

| dbg_rdlvl_done[0]         | ila_basic[12]         | Signifies the successful completion of Read Leveling Stage 1 calibration                |

| dbg_rdlvl_done[1]         | ila_basic[13]         | Signifies the successful completion of the MPR Stage of calibration                     |

| dbg_rdlvl_err[0]          | ila_basic[14]         | Signifies Read Leveling Stage 1 calibration exhibited errors and did not complete       |

| dbg_rdlvl_err[1]          | ila_basic[15]         | Signifies the MPR stage of calibration exhibited errors and did not<br>complete         |

| dbg_oclkdelay_calib_start | ila_basic[16]         | Signifies the start of the OCLKDELAY stage of calibration                               |

| dbg_oclkdelay_calib_done  | ila_basic[17]         | Signifies successful completion of the OCLKDELAY stage of calibration                   |

| dbg_wrcal_start           | ila_basic[19]         | Signifies the start of the Write Calibration stage of calibration                       |

| dbg_wrcal_done            | ila_basic[20]         | Signifies successful completion of the Write Calibration stage of<br>calibration        |

| dbg_wrcal_err             | ila_basic[21]         | Signifies Write Calibration exhibited errors and did not complete                       |

Each of these stages can be used as triggers in the Basic, Write Path, and Read Path ILA ChipScope cores to determine why the stage failed. The section below details these debugging steps.

## **Debug Signals**

#### Table 2: DDR23/DDR2 Debug Signals

| Debug Signal | ILA/VIO Connection     | Signal Description |

|--------------|------------------------|--------------------|

|              |                        |                    |

|              | © Copyright 2012 Xilir | או                 |

| init_calib_complete       | ila_basic[0]     | Signifies memory initialization and calibration have completed successfully                            |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------|

| dbg_wrlvl_start           | ila_basic[1]     | Signifies the start of the Write Leveling stage of calibration                                         |

| dbg_wrlvl_done            | ila_basic[2]     | Signifies successful completion of the Write<br>Leveling stage of calibration                          |

| dbg_wrlvl_err             | ila_basic[3]     | Signifies the Write Leveling stage of<br>calibration exhibited errors and did not<br>complete          |

| dbg_pi_phaselock_start    | ila_basic[4]     | Signifies the start of the PHASELOCK stage<br>of calibration                                           |

| dbg_pi_phaselock_done     | ila_basic[5]     | Signifies successful completion of the<br>PHASELOCK stage of calibration                               |

| dbg_pi_phaselock_err      | ila_basic[6]     | Signifies the PHASELOCK stage of calibration exhibited errors and did not complete                     |

| dbg_pi_dqsfound_start     | ila_basic[7]     | Signifies the start of the DQSFOUND stage of<br>calibration                                            |

| dbg_pi_dqsfound_done      | ila_basic[8]     | Signifies successful completion of the<br>DQSFOUND stage of calibration                                |

| dbg_pi_dqsfound_err       | ila_basic[9]     | Signifies the DQSFOUND stage of calibration exhibited errors and did not complete                      |

| dbg_rdlvl_start[0]        | ila_basic[10]    | Signifies the start of Read Leveling Stage 1 calibration                                               |

| dbg_rdlvl_start[1]        | ila_basic[11]    | Signifies the start of the MPR stage of<br>calibration                                                 |

| dbg_rdlvl_done[0]         | ila_basic[12]    | Signifies the successful completion of Read Leveling Stage 1 calibration                               |

| dbg_rdlvl_done[1]         | ila_basic[13]    | Signifies the successful completion of the MPR Stage of calibration                                    |

| dbg_rdlvl_err[0]          | ila_basic[14]    | Signifies Read Leveling Stage 1 calibration exhibited errors and did not complete                      |

| dbg_rdlvl_err[1]          | ila_basic[15]    | Signifies the MPR stage of calibration<br>exhibited errors and did not complete                        |

| dbg_oclkdelay_calib_start | ila_basic[16]    | Signifies the start of the OCLKDELAY stage<br>of calibration                                           |

| dbg_oclkdelay_calib_done  | ila_basic[17]    | Signifies successful completion of the<br>OCLKDELAY stage of calibration                               |

| dbg_wrcal_start           | ila_basic[19]    | Signifies the start of the Write Calibration stage of calibration                                      |

| dbg_wrcal_done            | ila_basic[20]    | Signifies successful completion of the Write Calibration stage of calibration                          |

| dbg_wrcal_err             | ila_basic[21]    | Signifies Write Calibration exhibited errors<br>and did not complete                                   |

| dbg_phy_init              | ila_basic[27:22] | State variable for the PHY Init state machine.<br>States can be decoded in the ddr_phy_init<br>module. |

# **£** XILINX。

| dbg_rddata            | ila_basic[92:29]   | Read data read out of the IN_FIFO for the DQS group selected through dbg_dqs on the VIO. This is a 64-bit bus. For an example of how the data is captured, see the Debug Read Data table below. This debug port will not capture ECC data.                                    |

|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cmp_data              | ila_basic[194:131] | Register version of compare data from the Traffic Generator.                                                                                                                                                                                                                  |

| dq_error_bytelane_cmp | ila_basic[203:195] | Indicates which byte has data comparison error for the Traffic Generator.                                                                                                                                                                                                     |

| wl_state_r            | ila_wrpath[4:0]    | State variable for the Write Leveling State<br>Machine. States can be decoded in the<br>ddr_phy_wrlvl.v module.                                                                                                                                                               |

| wrcal_dqs_cnt_r       | ila_wrpath[9:6]    | Signifies the DQS byte group being calibrated<br>during Write Leveling. The algorithm will<br>sequentially step through the DQS byte<br>groups until write leveling completes<br>successfully or a data byte group fails due a 0<br>to 1 transition not being detected on DQ. |

| wl_edge_detect_valid  | ila_wrpath[10]     | Signifies valid time Write Leveling algorithm is searching for edge                                                                                                                                                                                                           |

| rd_data_edge_detect   | ila_wrpath[11]     | Signifies Write Leveling calibration found the<br>0-to-1 edge transition                                                                                                                                                                                                      |

| wl_po_fine_cnt        | ila_wrpath         | Phaser_out Fine Taps found during Write<br>Leveling. Byte capture based on VIO<br>dbg_dqs setting.                                                                                                                                                                            |

| wl_po_fine_cnt_0-8    | ila_wrpath         | Phaser_out Fine Taps found during Write<br>Leveling                                                                                                                                                                                                                           |

| wl_po_coarse_cnt      | ila_wrpath         | Phaser_out Coarse Taps found during Write<br>Leveling. Byte capture based on VIO dbg_dqs<br>setting.                                                                                                                                                                          |

| wrl_po_coarse_cnt_0-8 | ila_wrpath         | Phaser_out Coarse Taps found during Write Leveling                                                                                                                                                                                                                            |

| ocal_tap_cnt          | ila_wrpath[37:32]  | Tap used to move to the center of the window after finding first and second edges                                                                                                                                                                                             |

| ocal_edge1_found      | ila_wrpath[38]     | Signifies that the first edge is found during<br>OCLKDELAY calibration when the taps are<br>decremented from 30                                                                                                                                                               |

| ocal_edge2_found      | ila_wrpath[39]     | Signifies that the second edge is found during OCLKDELAY calibration when the taps are incremented from 30                                                                                                                                                                    |

| ocal_edge1_taps       | ila_wrpath[45:40]  | Tap value when the first edge is found during OCLKDELAY calibration                                                                                                                                                                                                           |

| ocal_edge2_taps       | ila_wrpath[51:46]  | Tap value when the second edge is found during OCLKDELAY calibration                                                                                                                                                                                                          |

| ocal_state_r          | ila_wrpath[56:52]  | State variable for the OCLKDELAY state<br>machine. States can be decoded in the<br>ddr_phy_oclkdelay_cal module                                                                                                                                                               |

| pat_data_match        | ila_wrpath[64]     | Asserts when the valid pattern is detected                                                                                                                                                                                                                                    |

| pat_data_match_valid  | ila_wrpath[65]     | Toggles when the correct pattern is detected                                                                                                                                                                                                                                  |

| wrcal_dqs_cnt_r                  | ila_wrpath[69:66]       | Current DQS group being calibrated in Write<br>Calibration. When wrcal_start asserts,<br>wrcal_dqs_cnt_r is 0. The algorithm<br>sequentially steps through the DQS byte<br>groups checking to see if the read data<br>pattern matches the expected<br>FF00AA55555AA9966 pattern. If the pattern<br>matches, wrcal_dqs_cnt increments by 1. The<br>algorithm then starts looking for the correct<br>data pattern on the next byte until it reaches<br>DQS_WIDTH-1 or a data byte group fails due<br>to the data pattern not being detected<br>properly. The wrcal_dqs_cnt stays at<br>DQS_WIDTH-1 after wrcal_done signal is<br>asserted. |

|----------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cal2_state                       | ila_wrpath[74:70]       | Write Calibration state machine variable.<br>States can be decoded in the ddr_phy_wrcal.v<br>module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| not_empty_wait_cnt               | ila_wrpath[79:75]       | Count value during write calibration pattern<br>detection. Maximum count is 'd31. If count<br>reaches d'31, write calibration will fail with the<br>assertion of wrcal_err.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| early1_data                      | ila_wrpath[80]          | Asserts when the pattern detected is one CK clock cycle early. When this is asserted, the write leveling algorithm moves the CK clock one cycle. After CK is moved, the write calibration algorithm restarts pattern detection.                                                                                                                                                                                                                                                                                                                                                                                                          |

| early2_data                      | ila_wrpath[81]          | Asserts when the pattern detected is two CK clock cycles early. When this is asserted, the write leveling algorithm moves the CK clock two cycles. After CK is moved, the write calibration algorithm restarts pattern detection.                                                                                                                                                                                                                                                                                                                                                                                                        |

| stg2_tap_cnt                     | ila_wrpath              | Final Phaser_OUT Stage 3 tap count found during OCLKDELAYED Calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| dbg_pi_phase_locked_phy4lanes    | ila_rdpath[11:0]        | Signifies which of the PHASER_IN lanes has achieved lock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| dbg_pi_dqs_found_lanes_phy4lanes | ila_rdpath[23:12]       | Signifies which of the PHASER_IN lanes is able to find the DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| cal1_state_r                     | ila_rdpath[45:40]       | State machine variable for MPR and Read<br>Leveling Stage 1. States can be decoded in<br>the ddr_phy_rdlvl.v module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| cal1_cnt_cpt_r                   | ila_rdpath[49:46]       | Signifies the byte that failed MPR read leveling or read leveling stage 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| mux_rd_rise0                     | ila_rdpath / ila_wrpath | Data pattern received on rising edge 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| mux_rd_fall0                     | ila_rdpath / ila_wrpath | Data pattern received on falling edge 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mux_rd_rise1                     | ila_rdpath / ila_wrpath | Data pattern received on rising edge 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| mux_rd_fall1                     | ila_rdpath / ila_wrpath | Data pattern received on falling edge 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mux_rd_rise2                     | ila_rdpath / ila_wrpath | Data pattern received on rising edge 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| mux_rd_fall2                     | ila_rdpath / ila_wrpath | Data pattern received on falling edge 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mux_rd_rise3                     | ila_rdpath / ila_wrpath | Data pattern received on rising edge 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| mux_rd_fall3                               | ila_rdpath / ila_wrpath             | Data pattern received on falling edge 3.                                                                                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pat_data_match                             | ila_rdpath[114]                     | Toggles when the correct pattern is detected                                                                                                                                                                                                                                        |

| mux_rd_valid                               | ila_rdpath[115],                    | Asserts when the valid pattern is detected                                                                                                                                                                                                                                          |

| dbg_cpt_first_edge_cnt                     | ila_rdpath, per DQS and per RANK    | Signifies PHASER_IN fine tap count when the first edge in MPR and Read Leveling Stage 1 is found. Byte capture based on VIO dbg_dqs setting.                                                                                                                                        |

| dbg_cpt_first_edge_cnt_rnk0/1_byte0-8      | ila_rdpath, per DQS and per RANK    | Signifies PHASER_IN fine tap count when the first edge in MPR and Read Leveling Stage 1 is found.                                                                                                                                                                                   |

| dbg_cpt_second_edge_cnt                    | ila_rdpath, per DQS and per RANK    | Signifies PHASER_IN fine tap count when<br>then second edge in MPR and Read Leveling<br>Stage 1 is found. Byte capture based on VIO<br>dbg_dqs setting.                                                                                                                             |

| dbg_cpt_second_edge_cnt_rnk0/1_byte0-<br>8 | ila_rdpath, per DQS and per RANK    | Signifies PHASER_IN fine tap count when<br>then second edge in MPR and Read Leveling<br>Stage 1 is found.                                                                                                                                                                           |

| dbg_cpt_tap_cnt                            | ila_rdpath, per DQS and per RANK    | Signifies the center tap moved to based on<br>when the first and second edges were found.<br>Byte capture based on VIO dbg_dqs setting.                                                                                                                                             |

| dbg_cpt_tap_cnt_rnk0/1_byte0-8             | ila_rdpath, per DQS and<br>per RANK | Signifies the center tap moved to based on when the first and second edges were found.                                                                                                                                                                                              |

| dbg_dq_idelay_tap_cnt                      | ila_rdpath, per DQS and per RANK    | IDELAY tap value for MPR and Read Leveling<br>Stage 1. This should be within 2-3 taps across<br>all DQS byte groups. Byte capture based on<br>VIO dbg_dqs setting.                                                                                                                  |

| dbg_dq_idelay_tap_cnt_rnk0/1_byte0-8       | ila_rdpath, per DQS and per RANK    | IDELAY tap value for MPR and Read Leveling<br>Stage 1. This should be within 2-3 taps across<br>all DQS byte groups.                                                                                                                                                                |

| dbg_rd_data_offset_0                       | ila_rdpath[35:24].                  | Read Data Offset found during calibration                                                                                                                                                                                                                                           |

| dbg_calib_rd_data_offset_1                 | ila_rdpath[175:164]                 | Read Data Offset found during calibration                                                                                                                                                                                                                                           |

| dbg_calib_rd_data_offset_2                 | ila_rdpath[187:176]                 | Read Data Offset found during calibration                                                                                                                                                                                                                                           |

| dbg_data_offset                            | ila_rdpath[193:188]                 | Data Offset used during normal operation.<br>Value will change during writes, reads, and<br>idle. During writes, it is CWL+2+slot#. During<br>non-data commands, it is 0. During reads, it<br>should match what was found during<br>DQSFOUND calibration<br>(rd_data_offset_ranks). |

| dbg_data_offset_1                          | ila_rdpath[199:194]                 | Data Offset used during normal operation.<br>Value will change during writes, reads, and<br>idle. During writes, it is CWL+2+slot#. During<br>non-data commands, it is 0. During reads, it<br>should match what was found during<br>DQSFOUND calibration<br>(rd_data_offset_ranks). |

| dbg_data_offset_2                          | ila_rdpath[205:200]                 | Data Offset used during normal operation.<br>Value will change during writes, reads, and<br>idle. During writes, it is CWL+2+slot#. During<br>non-data commands, it is 0. During reads, it<br>should match what was found during<br>DQSFOUND calibration<br>(rd_data_offset_ranks). |

| dbg_bit                                    | vio_sync_out[8:0]                   |                                                                                                                                                                                                                                                                                     |

|                                            | © Copyright 2012 Xilir              |                                                                                                                                                                                                                                                                                     |

# **E**XILINX.

| dbg_dqs             | vio_sync_out[12:9]  | Selects the DQS byte group for the debug signals. For example, set to 4'b0000 to view the results on DQS[0].                                                                             |

|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vio_modify_enable   | vio_sync_out[36]    | Set to 1 to vary the command Traffic Generator command pattern.                                                                                                                          |

| vio_addr_mode_value | vio_sync_out[43:41] | Sets the address mode used by the Traffic<br>Generator.<br>1: Fixed Address<br>2: PRBS Address<br>3: Sequential Address                                                                  |

| vio_bl_mode_value   | vio_sync_out[49:48] | Sets the burst mode used by the Traffic<br>Generator<br>1: Fixed bl.<br>2: PRBS bl. If bl_mode value is set to 2, the<br>addr_mode value is forced to 2 to generate<br>the PRBS address. |

| vio_data_mask_gen   | vio_sync_out[58]    | Traffic generator Data Mask generation                                                                                                                                                   |

| vio_pause_traffic   | vio_sync_out[59]    | Set to 1 to pause the Traffic Generator.                                                                                                                                                 |

| dbg_clear_error     | vio_sync_out[63]    | Set to clear Traffic Generator errors. This signal can be used in checking for single bit errors or measuring a read window.                                                             |

# Debugging PHASER\_IN PHASELOCKED Calibration Failures (dbg\_pi\_phaselock\_err=1)

## **Calibration Overview**

During this stage of calibration, each PHASER\_IN is placed in the read calibration mode to phase align its free-running frequency reference clock to the associated read DQS. The calibration logic issues back-to-back read commands to provide the PHAESER\_IN block with a continuous stream of DQS pulses for it to achieve lock. Each DQS has an associated PHASER\_IN block. Dbg\_pi\_phase\_locked asserts when all PHASER\_INs have achieved lock and the PHASER\_INs are then placed in normal operation mode.

## Debug

If PHASER\_IN PHASELOCKED calibration failed, probe the DQS at the memory. A continuous stream of DQS pulses must be seen for lock to occur. Verify the signal integrity of the DQS pulses.

# Debugging PHASER\_IN DQSFOUND Calibration Failures (dbg\_pi\_dqsfound\_err=1)

## **Calibration Overview**

In this stage of calibration, the different DQS groups are aligned to the same PHY\_Clk and the optimal read data offset position is found with respect to the read command. The calibration logic issues a set of four back-to-back reads with gaps in between. Each Phaser\_IN detects the read DQS preamble. A single read data offset value is determined for all DQS groups. This data offset is then used during read requests to the PHY\_CONTROL block.

# 🐮 XILINX.

## Debug

- If the DQSFOUND stage fails, probe DQS at the memory. Sets of four back-to-back reads should be seen. Read DQS(s) is required by the PHASER\_IN(s) to establish the read\_data\_offset value. If the design is stuck in the DQSFOUND stage, start observing the quality of DQS at the memory.

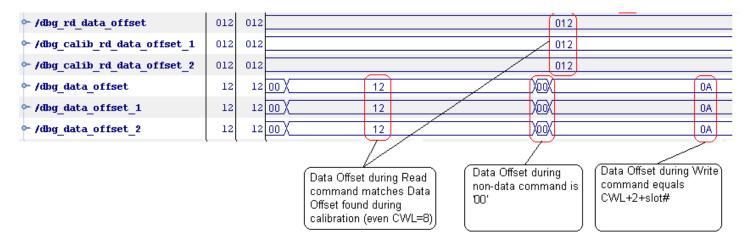

- Look at the read\_data\_offset values. There are two sets of read\_data\_offset values that need to be compared.

- To determine the read data offset found at the end of DQSFOUND calibration, look at dbg\_rd\_data\_offset\_0, dbg\_calib\_data\_offset\_1 (only when more than 1 bank is used), dbg\_calib\_data\_offset\_2 (only when 3 banks are used).

- To determine the data offset used during normal operation reads, look at dbg\_data\_offset, dbg\_data\_offset\_1 (only when more than one bank is used), and dbg\_data\_ofset\_2 (only when three banks are used).

- These signals will change between reads, writes, and non-data commands. During writes, the value is CWL+2+slot#. During non-data commands, the value is 0. During reads, the value should match what was found during DQSFOUND calibration (dbg\_rd\_data\_offset\_0, dbg\_rd\_data\_offset\_1, and dbg\_rd\_data\_offset\_2).

- Compare the read data offset values used during calibration and normal operation reads. These values should

match for reads with even CWL and be off by 1 for reads with odd CWL. One additional offset is added for odd

CWL values because reads/writes are assigned to slot1 by the memory controller, whereas slot0 is used for even

CWL.

- The read data offset should be equal to CL + 4 or 5 which is the CL plus the round trip delay on the PCB.

- When this stage fails (pi\_dqsfound\_err=1), look to see if any of the dbg\_calib\_rd\_data\_offset/\_1/\_2 have calculated offsets. If not, focus on the DQS signals associated with the failing bank by probing each and analyzing the signal integrity.

If pi\_dqsfound\_err asserted, denoting a failure during DQSFOUND calibration, use **pi\_dqsfound\_err=1 as the trigger**. If this stage completed successfully with the asserting of pi\_dqsfound\_done=1, use **pi\_dqsfound\_done=1 as the trigger** to analyze how the stage completed. Look at dbg\_rd\_data\_offset, dbg\_calib\_rd\_data\_offest\_1, and dbg\_calib\_rd\_data\_offest \_2, these values should vary by one at the most. Next, compare these values to the values used during normal operation reads on the dbg\_data\_offset, dbg\_data\_offset\_1 and dbg\_data\_offset\_2 signals. Record the results in the "7 Series DDR3 Calibration Results" spreadsheet.

| Debug Signal               | ILA/VIO<br>Connection | Signal Description                                                                                                                                                                                                                                                            |

|----------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dbg_pi_dqsfound_start      | ila_basic[7]          | Signifies the start of the DQSFOUND stage of calibration                                                                                                                                                                                                                      |

| dbg_pi_dqsfound_done       | ila_basic[8]          | Signifies successful completion of the DQSFOUND stage of<br>calibration                                                                                                                                                                                                       |

| dbg_pi_dqsfound_err        | ila_basic[9]          | Signifies the DQSFOUND stage of calibration exhibited errors and did not complete                                                                                                                                                                                             |

| dbg_rd_data_offset_0       | ila_rdpath[35:24].    | Read Data Offset found during calibration                                                                                                                                                                                                                                     |

| dbg_calib_rd_data_offset_1 | ila_rdpath[175:164]   | Read Data Offset found during calibration                                                                                                                                                                                                                                     |

| dbg_calib_rd_data_offset_2 | ila_rdpath[187:176]   | Read Data Offset found during calibration                                                                                                                                                                                                                                     |

| dbg_data_offset            | ila_rdpath[193:188]   | Data Offset used during normal operation. Value will change<br>during writes, reads, and idle. During writes, it is CWL+2+slot#.<br>During non-data commands, it is 0. During reads, it should match<br>what was found during DQSFOUND calibration<br>(rd_data_offset_ranks). |

| dbg_data_offset_1          | ila_rdpath[199:194]   | Data Offset used during normal operation. Value will change<br>during writes, reads, and idle. During writes, it is CWL+2+slot#.<br>During non-data commands, it is 0. During reads, it should match<br>what was found during DQSFOUND calibration<br>(rd_data_offset_ranks). |

## Table 3: Debug Signals of Interest for DQSFOUND Calibration

| dbg_data_offset_2 | ila_rdpath[205:200] | Data Offset used during normal operation. Value will change<br>during writes, reads, and idle. During writes, it is CWL+2+slot#.<br>During non-data commands, it is 0. During reads, it should match<br>what was found during DQSFOUND calibration<br>(rd_data_offset_ranks). |

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## Expected ChipScope Tool Results

Figure 2 - Expected ChipScope Tool Results

## Debugging Write Leveling Failures (dbg\_wrlvl\_err = 1)

## **Calibration Overview**

Write leveling, a new features in DDR3 SDRAMs, allows the controller to adjust each write DQS phase independently with respect to the CK forwarded to the DDR3 SDRAM device. This compensates for the skew between DQS and CK and meets the tDQSS specification. During this stage, the PHY logic asserts the Write\_Calib\_N input to the PHY Control Block to indicate the start of write leveling. Periodic write requests are issued to the PHY Control Block to generate periodic DQS pulses. The PHASER\_IN outputs a free-running clock to capture the DQ feedback into the DQ IN\_FIFOs. The PHASER\_OUT fine and coarse taps are used to phase shift DQS one tap at a time until a 0-to-1 transition is seen on the feedback DQ.

Write Leveling is performed at three different points during the calibration process. After memory initialization completes, the PHASER\_OUT fine and coarse taps are set to zero. Write Leveling is then initially performed to align DQS to CK. After OCLKDELAYED calibration completes, the coarse tap values found during the initial Write Leveling are carried over and the fine taps are reset to zero. Write Leveling is performed again to ensure the DQS-to-CK relationship is still correct. Finally, during Write Calibration both the fine and coarse delays are carried over and final adjustments are made when necessary. During Write Calibration, the appropriate pattern must be detected. If Write Leveling aligned DQS to the wrong CK clock, final PHASER\_OUT fine/coarse delay adjustments are required to move DQS up to two CK clock cycles. This section shows how to capture the Write Leveling results after each of these adjustments.

## **Debug Steps**

- Verify DQS is toggling on the board. The FPGA sends DQS during Write Leveling. If DQS is not toggling, something is wrong with the setup and the General Checks section of this answer record should be thoroughly reviewed.

- Verify fly-by-routing is implemented correctly on the board.

- Verify CK to DQS trace routing. The CK clocks should be longer then DQS. The recommended value for additional total electrical delay on CK/CK# relative to DQS/DQS# is 150ps, but any value greater than 0ps is acceptable.

- The Mode Registers must be properly set up to enable Write Leveling. Specifically, address bit A7 must be correct. If the part chosen in MIG is not accurate or there is a problem with the connection of the address bits on the board, this could be an issue. If the Mode Registers are not set up to enable Write Leveling, the 0-to-1 transition will never be seen. Note that for dual rank design when address mirroring is used, address bit A7 is not the same between the two ranks.

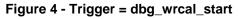

- When dbg\_wrlvl\_err asserts (equals 1), users must determine during which of the three different stages write leveling is performed the failure occurred. Set the ChipScope trigger to dbg\_wrlvl\_err=1 and look at the other "DDR Basic" signals to see which stages completed.

- 1. If only PHASELOCK and DQSFOUND completed, the write leveling failure occurred during the initial run through.

- 2. If dbg\_wrcal\_start did not assert, the write leveling failure occurred after OCLKDELAYED calibration.

- 3. If dbg\_wrcal\_start asserted but dbg\_wrcal\_done did not, the write leveling failure occurred during the final run through during Write Calibration.

- When dbg\_wrlvl\_done asserts (equals 1) and the results of each Write Leveling stage is of interest, separately use the following three ChipScope triggers to capture the Write Leveling tap results for each stage. Seeing how Write Leveling completed is useful to see how far apart the taps are for different DQS byte groups.

- 1. dbg\_wrlvl\_done=1

- 2. dbg\_wrcal\_start=1

- 3. init\_calib\_complete=1

- To capture the write leveling results at each stage, change/increment dbg\_dqs on the VIO and set the appropriate trigger as noted above. Look at the taps results and record in the "7 Series DDR3 Calibration Results" spreadsheet. Later releases of MIG include results for all DQS byte groups removing the need to use dbg\_dqs.

**NOTE:** The tap variance across DQS byte groups will be quite different due to fly-by routing.

| Debug Signal         | ILA/VIO<br>Connection | Signal Description                                                                                                                                                                                                                                                      |

|----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dbg_wrlvl_start      | ila_basic[1]          | Signifies the start of the Write Leveling stage of calibration                                                                                                                                                                                                          |

| dbg_wrlvl_done       | ila_basic[2]          | Signifies successful completion of the Write Leveling stage of calibration                                                                                                                                                                                              |

| dbg_wrlvl_err        | ila_basic[3]          | Signifies the Write Leveling stage of calibration exhibited errors and did not complete                                                                                                                                                                                 |

| wl_state_r           | ila_wrpath[4:0]       | State variable for the Write Leveling State Machine. States can be decoded in the ddr_phy_wrlvl.v module.                                                                                                                                                               |

| wrcal_dqs_cnt_r      | ila_wrpath[9:6]       | Signifies the DQS byte group being calibrated during Write Leveling.<br>The algorithm will sequentially step through the DQS byte groups until<br>write leveling completes successfully or a data byte group fails due a 0<br>to 1 transition not being detected on DQ. |

| wl_edge_detect_valid | ila_wrpath[10]        | Signifies valid time Write Leveling algorithm is searching for edge                                                                                                                                                                                                     |

| rd_data_edge_detect  | ila_wrpath[11]        | Signifies Write Leveling calibration found the 0-to-1 edge transition                                                                                                                                                                                                   |

| wl_po_fine_cnt        | ila_wrpath | Phaser_out Fine Taps found during Write Leveling. Byte capture based on VIO dbg_dqs setting.   |

|-----------------------|------------|------------------------------------------------------------------------------------------------|

| wl_po_fine_cnt_0-8    | ila_wrpath | Phaser_out Fine Taps found during Write Leveling                                               |

| wl_po_coarse_cnt      | ila_wrpath | Phaser_out Coarse Taps found during Write Leveling. Byte capture based on VIO dbg_dqs setting. |

| wrl_po_coarse_cnt_0-8 | ila_wrpath | Phaser_out Coarse Taps found during Write Leveling                                             |

## Expected ChipScope Tool Results

| vizeseivenfol                                   |         |        |           |                     |          |              |     |       |       |        |     |     |     |         | 1        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |          |             |

|-------------------------------------------------|---------|--------|-----------|---------------------|----------|--------------|-----|-------|-------|--------|-----|-----|-----|---------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-------------|

| /dbg_oclkdelay_cali                             | b_done  | •      |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      | Bus/Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | Vi       | alue        |

| _/dbg_oclkdelay_cali                            | b_start |        |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      | vio modify_enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |          | 0           |

| —/dbg_rdlvl_err[1]                              |         |        |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | -        |             |

| /dbg_rdlvl_err[0]                               | _       |        |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      | vio_data_mask_gen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1              | L        | 0           |

| /dbg_rdlvl_done[1]                              |         |        |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      | vio_pause_traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |          | 0           |

| /dbg_rdlvl_done[0]                              |         |        |           |                     |          |              |     |       |       |        |     |     |     |         | Х        |      | dbg_clear_error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |          | 0           |